# DUP11 Bit Synchronous Interface User's Manual

# DUP11 Bit Synchronous Interface User's Manual

Copyright © 1976, 1982 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

#### Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DIGITAL | DECsystem-10     | MASSBUS |

|---------|------------------|---------|

| DEC     | DECSYSTEM-20     | OMNIBUS |

| PDP     | DIBOL            | OS/8    |

| DECUS   | <b>EDUSYSTEM</b> | RSTS    |

| UNIBUS  | VAX              | RSX     |

| 01(1200 | VMS              | IAS     |

## **CONTENTS**

|           |                                                        | Page |

|-----------|--------------------------------------------------------|------|

| CHAPTER 1 | INTRODUCTION                                           |      |

| 1.1       | SCOPE                                                  | 1-1  |

| 1.2       | DUP11 GENERAL DESCRIPTION                              | 1-1  |

| 1.3       | SDLC AND DDCMP PROTOCOLS                               |      |

| 1.3.1     | Introduction                                           |      |

| 1.3.2     | General Information                                    |      |

| 1.3.3     | SDLC Protocol Description                              |      |

| 1.3.3.1   | Message Format                                         |      |

| 1.3.3.2   | Abort Sequence                                         |      |

| 1.3.4     | DDCMP Protocol                                         |      |

| 1.3.4.1   | Controlling Data Transfers                             | 1-5  |

| 1.3.4.2   | Error Checking and Recovery                            | 1-3  |

| 1.3.4.3   |                                                        |      |

|           | Character Coding                                       |      |

| 1.3.4.4   | Data Transparency                                      |      |

| 1.3.4.5   | Data Channel Utilization                               |      |

| 1.3.4.6   | Synchronization                                        |      |

| 1.3.4.7   | Bootstrapping                                          | 1-8  |

| CHAPTER 2 | INSTALLATION                                           |      |

| 2.1       | SCOPE                                                  |      |

| 2.2       | UNPACKING AND INSPECTION                               | 2-1  |

| 2.3       | TOOLS REQUIRED FOR INSTALLATION                        | 2-1  |

| 2.4       | PREINSTALLATION SET-UP PROCEDURES                      | 2-1  |

| 2.5       | INSTALLATION                                           |      |

| 2.5.1     | M7867 Module Installation                              |      |

| 2.5.2     | H3001 Distribution Panel Installation                  |      |

| 2.5.2.1   | H3001 Installation in an I/O Bulkhead                  |      |

| 2.5.2.2   | H3001 Installation in Cabinets Without an I/O Bulkhead |      |

| 2.6       | VERIFICATION OF HARDWARE OPERATION                     |      |

| 2.7       | COMPATIBILITY                                          |      |

| 2.8       | POWER REQUIREMENTS                                     |      |

| 2.9       | DEVICE ADDRESSES.                                      | 2-19 |

| 2.9.1     | Introduction                                           |      |

| 2.9.2     | Floating Device Address Assignment                     |      |

| 2.9.3     | Device Address Selection                               |      |

| 2.10      | VECTOR ADDRESSES                                       |      |

| 2.10.1    | Introduction                                           |      |

| 2.10.1    | Floating Vector Address Assignment                     |      |

| 2.10.2    | Vector Address Selection                               |      |

| 2.10.3    | Accial Wantess Delection                               | 2-22 |

## **CONTENTS (Cont)**

REGISTER DESCRIPTIONS AND OPERATING FEATURES

**CHAPTER 3**

Page

| 3.1        | INTRODUCTION                                               |             |

|------------|------------------------------------------------------------|-------------|

| 3.2        | DUP11 REGISTERS AND DEVICE ADDRESS SELECTION               |             |

| 3.3        | INTERRUPT VECTORS                                          |             |

| 3.4        | PRIORITY SELECTION                                         |             |

| 3.5        | REGISTER BIT ASSIGNMENTS                                   |             |

| 3.6        | MAJOR OPERATING FEATURES                                   |             |

| 3.6.1      | Introduction                                               |             |

| 3.6.2      | Modem Control                                              |             |

| 3.6.3      | Transmitter Section                                        |             |

| 3.6.4      | Receiver Section                                           | 3-27        |

| APPENDIX A | PDP-11 MEMORY ORGANIZATION AND ADDRESSING CONVENTIONS      | I           |

|            | FIGURES                                                    |             |

| Figure No. | Title                                                      | Page        |

| 1-1        | SDLC Message Format                                        | . 1-3       |

| 1-2        | DDCMP Data Message Format                                  | . 1-5       |

| 1-3        | DDCMP Sample Handshaking Procedure                         |             |

| 2-1        | DUP11 Parts Diagram                                        | . 2-2       |

| 2-2        | Component Location                                         | 2-4         |

| 2-3        | DUP11 Cabling                                              | 2-5         |

| 2-4        | DUP11 (M7867 Module) Mounted in DD11-B                     | . 2-5       |

| 2-5        | H3001 Installation in a Horizontally Oriented I/O Bulkhead |             |

| 2-6        | H3001 Installation in a Vertically Oriented I/O Bulkhead   |             |

| 2-7        | Side Rail Installation of H3001 Distribution Panel         |             |

| 2-8        | Installation Procedure Flowchart                           |             |

| 2-9        | H3001 Distribution Panel                                   |             |

| 3-1        | DUP11 Register Configurations and Bit Assignments          |             |

| 3-2        | Receiver Control and Status Register Format                | . 3-3       |

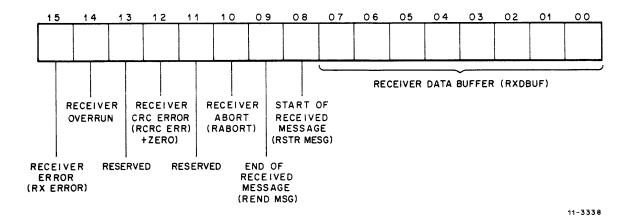

| 3-3        | Receiver Data Buffer Register Format                       | . 3-9       |

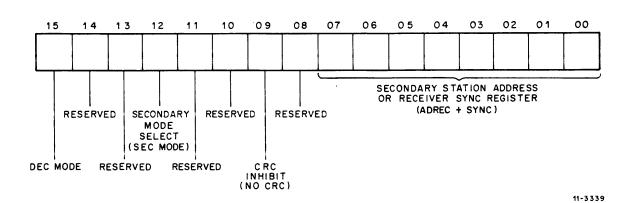

| 3-4        | Parameter Control and Status Register Format               |             |

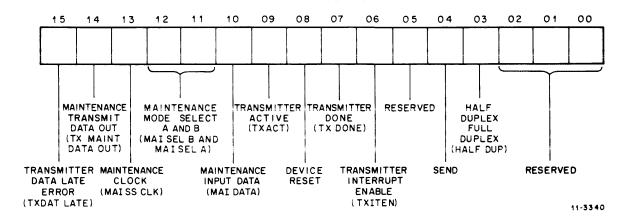

| 3-5        | Transmitter Control and Status Register Format             |             |

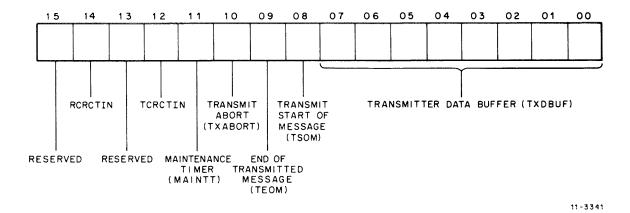

| 3-6        | Transmitter Data Buffer Register Foramt                    | . 3-20      |

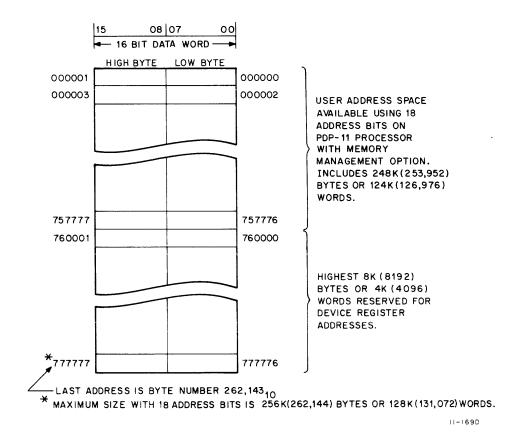

| A-1        | Memory Organization for Maximum Size Using 18 Address Bits |             |

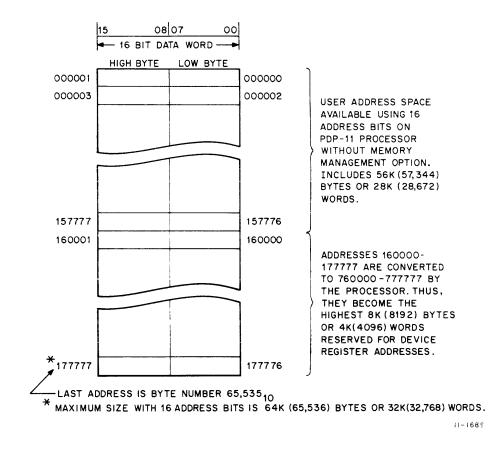

| A-2        | Memory Organization for Maximum Size Using 16 Address Bits | <b>A</b> -3 |

|            |                                                            |             |

## **TABLES**

| Table No. | Title                                                                | Page |

|-----------|----------------------------------------------------------------------|------|

| 2-1       | M7867 Jumper Configuration                                           | 2-3  |

| 2-2       | H3001 Switch Settings                                                | 2-11 |

| 2-3       | Guide for Setting Switches to Select Device Address                  | 2-21 |

| 2-4       | Guide for Setting Switches to Select Vector Address                  | 2-23 |

| 3-1       | DUP11 Registers                                                      | 3-1  |

| 3-2       | Bit Descriptions for Receiver Control and Status Register (RXCSR)    | 3-3  |

| 3-3       | Bit Descriptions for Receiver Data Buffer Register (RXDBUF)          | 3-9  |

| 3-4       | Bit Descriptions for Parameter Control and Status Register (PARCSR)  | 3-12 |

| 3-5       | Bit Descriptions for Transmitter Control and Status Register (TXCSR) | 3-14 |

| 3-6       | Bit Descriptions for Transmitter Data Buffer Register (TXDBUF)       | 3-20 |

### CHAPTER 1 INTRODUCTION

#### 1.1 SCOPE

This manual provides the user with the information necessary to install and operate the DUP11 Synchronous Line Interface. The manual is organized into three chapters and one appendix.

Chapter 1 - Introduction

Chapter 2 – Installation

Chapter 3 – Register Description

Appendix A – PDP-11 Memory Organization and Addressing Conventions

This chapter provides a general description of the DUP11 and a general discussion of the Synchronous Data Link Control (SDLC) protocol and Digital Data Communications Message Protocol (DDCMP).

#### 1.2 DUP11 GENERAL DESCRIPTION

The DUP11 provides a data path between a synchronous modem and the Unibus. It operates under the discipline of SDLC, ADCCP, DDCMP, and other similar protocols. Protocols of the BISYNC family can be used with some loss of efficiency due to the additional software decisions required.

The DUP11 provides parallel-to-serial conversion of data to be transmitted and serial-to-parallel conversion of received data. Logic is provided to create a transparent data stream and to compute a CRC check character during transmission. All information is handled in 8-bit bytes and VRC parity is not provided. CRC error detection is provided during reception. Modem control and level conversion logic is provided also.

Interrupt control logic is used to generate requests for the transfer of data between the DUP11 and the PDP-11 system memory via the Unibus. No direct memory access (DMA) logic is contained in the DUP11.

The DUP11 contains logic to perform the following functions:

- 1. Program control of secondary station address recognition. Primary station operation is used as the default condition (SDLC protocol family only).

- 2. Programmable SYN character recognition (DDCMP and BISYNC protocol families).

- 3. CRC characters computation and error detection (SDLC and DDCMP protocol families).

- 4. Automatic transmission of flag characters initiated by the program (SDLC protocol family only).

- 5. Program control of transmission of abort sequence and 16 zero sequence (SDLC protocol family only).

- 6. Hardware detection of received flags and abort sequences (SDLC protocol family only).

The DUP11, including level conversion, is contained on a hex module. The DUP11 is connected to the modem via a BC05C cable and BC02 cable that support RS232-C specifications only. Current mode operation is not supported by the DUP11 and it is not compatible with the DF11 series options.

The modem control logic is compatible with Bell 201, 208, and 209 series modems. There is no interlock between the transfer of data and modem control. The program controls handshaking with the modem, if it is required. Once the handshaking has been completed, the program can initiate the transfer of data. The modem control logic includes secondary receive and transmit leads. These leads can be redefined by the Field Service engineer at the user's request.

#### 1.3 SDLC AND DDCMP PROTOCOLS

#### 1.3.1 Introduction

This discussion provides a general description of the SDLC and DDCMP protocols. It is the prerequisite to a thorough understanding of the operation of the DUP11. Details of the SDLC, DDCMP, ADCCP and BISYNC protocols are found in the following documents:

Digital Data Communications Message Protocol (Digital Equipment 130-959-007-02) IBM Binary Synchronous Communications General Information (GA27-3004-2) ADCCP ANSI X3S34/475 DR7 ADCCP ANSI X3S34/584 DR1

#### 1.3.2 General Information

Although the mentioned protocols are not identical, they are similar enough to operate with the DUP11. The program directly controls the DUP11 operation through the use of control and status registers. The program must provide a continuous flow of data to be transmitted. No intra-message fill characters are allowed. The program must also service the receiver data buffer within the prescribed time.

When transmitting in the SDLC or DDCMP family of protocols, the program must form the address and command fields plus any other header information that is required. The program must maintain the transmitter data buffer and set marker bits to delimit the transmitted message. When receiving in the SDLC or DDCMP family of protocols, the program must interpret the header information, service the receiver data buffer, and monitor the status bits associated with the received data.

Protocols such as BISYNC that achieve transparency by using special control characters are less efficient than SDLC and DDCMP when used with the DUP11. This occurs because of the increased program involvement required to maintain transparency and compute the CRC character. The CRC control logic in the DUP11 is not suited to protocols in which special control characters appear within the body of the message. For these protocols, the CRC logic should be disabled by setting the NO CRC bit (PARCSR bit 9).

#### 1.3.3 SDLC Protocol Description

1.3.3.1 Message Format - The SDLC message format is shown in Figure 1-1. This format is called a frame and is the standard structure for all transmissions.

| ĺ | FLAG     | ADDRESS | CONTROL | INFORMATION     | FRAME CHECK SEQUENCE | FLAG     |

|---|----------|---------|---------|-----------------|----------------------|----------|

| l | 01111110 | 8 BITS  | 8 BITS  | VARIABLE LENGTH | 16 BITS              | 01111110 |

11-3430

Figure 1-1 SDLC Message Format

The frame starts with the 8-bit Flag sequence, 01111110, followed in order by the Address sequence, Control sequence, Information sequence (if present), Frame Check sequence, and ends with another Flag sequence. In some applications, the Flag is preceded by a sequence of 16 zeros.

Each sequence in the frame is discussed below with emphasis on related operational features of the DUP11, if applicable.

#### Flag Character

The flag character is a unique 8-bit character of the form 01111110. Flag characters are used to delimit the message. They can be used to fill in between messages but cannot be used as fillers within messages. When the transmitter initiates the start of a message by asserting the TSOM (transmitter start of message) bit, the initial flag character is automatically transmitted. If the TSOM bit is still asserted at the end of the first flag character, another flag character is transmitted. When the TXDONE (transmitter done bit) is asserted by the DUP11 subsequent to the program's asserting of the TSOM bit, the program may respond by loading data into the TXDBUF (transmitter data buffer) low byte, or leave the TSOM bit asserted and send another flag.

In some applications, the TSOM and TEOM bits are used to initiate a sequence of 16 zeros. This sequence can be initiated only from the idle state. To transmit this sequence, SEND must be asserted and TXACT must be cleared. With these requirements met, the program simultaneously sets TSOM and TEOM and the 16 zeros are transmitted. When the first zero bit is presented to the serial output, TXDONE is set. Now, the program should clear TEOM and on the next transition of TXDONE the program should clear TSOM. The first data character can be loaded now. This point marks the start of the initial flag character, the first data character is transmitted subsequent to the current flag character.

When the last character of a message has been loaded into the TXDBUF, that character is then transmitted. Subsequent to loading the last character, the TXDONE bit is asserted again by the DUP11. This marks the start of the transmission of the last character. At this time, the TEOM (transmitter end of message) may be asserted in the upper byte of the TXDBUF. The character currently being serialized (i.e., the last character of the message) is transmitted and followed by a CRC check character and the terminating flag character. This concludes the message.

When the receiver logic is enabled by the software, it searches for flag characters. If the basic SDLC or ADCCP message format is followed and the receiver is programmed to operate in the secondary mode, the following actions occur.

The eight bits after the last received flag are compared to the secondary station address. If a match is not found, the receiver continues to hunt for a flag. When the next flag character is located, this comparison of addresses is reiterated.

If the character subsequent to the flag character matches the secondary station address, characters received subsequent to the address character cause the RXDONE (receiver done) bit to be asserted. The RSOM (receiver start of message) bit is presented to the program along with the first data character.

When the secondary station receiver is actively transferring data, the following events occur when a terminating flag character is detected. The receiver logic automatically resumes the address search as cited earlier. Also, a status entry is made into the receiver data buffer, the REOM bit is asserted and the CRC error bit is set if an error was detected. The lower byte of data in this entry is invalid.

When the receiver logic is programmed to operate as a primary station, all characters subsequent to the last received flag character cause the RXDONE bit to be asserted. The first character of the frame is accompanied by the RSOM bit.

When the terminating flag character of a message is received, primary station operation is the same as cited above for secondary station operation. When the next data character is received, the receiver logic again sets the RSOM and RXDONE bits. The last two bytes preceding the flag were the receiver CRC bytes.

#### Address Character

The address character appears subsequent to the flag character and is eight bits long. This format supports a maximum of 256 addresses. The protocol has provisions for the recursive expansion of the number of addresses. This feature is not supported by the DUP11 hardware. It must be maintained by the program. In the secondary station mode, the program must load the address of the receiving station into the low byte of the PARCSR.

#### Control Field

The 8-bit control field follows the address character. This field is controlled by the program and is encoded to indicate the commands and responses to control the data link. This field has three formats as described below.

- 1. Nonsequenced Format used by the primary station primarily for data link management. Such duties include activating and initializing secondary stations, controlling the response mode of secondary stations, and reporting procedural errors.

- 2. Supervisory Format does not contain an information field but it is an adjunct to the information format. It is used by the primary station to poll the secondary stations. The secondary stations use this format to provide acknowledgment to the primary station.

- 3. Information Format used by primary and secondary stations for the transfer of information fields.

#### Information Field

This field is used for the transmission of data or status information. This field contains an arbitrary number of characters as specified by the documents covering the protocols. The DUP11 handles the data in this field as eight bit characters.

When one character is transmitted from the transmitter shift register, another character is taken from the data buffer. If the data buffer is empty, the transmitted data lead goes to a mark hold state. Also, a status bit is asserted to indicate the data underrun condition in SDLC or ADCCP and an Abort character is automatically transmitted.

There are no restrictions on bit patterns that appear between flags in an SDLC frame. Therefore, the transmitted data may contain six or more contiguous 1s and this pattern could be interpreted as a flag which would inadvertently terminate an incomplete frame. To prevent this action and to maintain data

transparency, the DUP11 contains 0 insertion and 0 removal logic that is active on all characters between the flags. During transmission, when five contiguous 1s occur, the transmitter automatically inserts a 0 after the fifth 1. During reception, the 0 after five contiguous 1s is automatically removed. This applies to all fields except the Flag.

#### Frame Check Sequence (FCS) Field

This 16-bit field follows the information field and is also referred to as the Block Check Character (BCC) or CRC check character. It is used in all SDLC frames to detect errors.

Logic to compute CRC check characters is included in the transmitter logic. Similarly, logic is included in the receiver logic to check the results when the check character is received. This operation of computing and verifying the CRC check is transparent to the program. Any error in the computation of the received check character in SDLC type protocol operation is indicated by a status bit in the receiver data buffer. If DDCMP operation is selected, the program must monitor a status bit to detect the desired accumulated results.

Two CRC polynomials are supported by the DUP11: CRC 16 and CCITT. When the SDLC or ADCCP mode of operation is selected, the CCITT polynomial is used and the internal CRC registers are effectively initialized to all 1s. During transmission, the complement of the accumulated CRC character is sent. If the SDLC or ADCCP mode is not selected, the CRC 16 polynomial is used providing CRC checking is not inhibited.

1.3.3.2 Abort Sequence – An abort is the premature termination of a data line by the transmitting station. An abort is detected by the reception of more than seven contiguous 1s. When the abort sequence is received, the message in progress is terminated. A flag (RXERROR) is set and RXDONE is set also. If the program has set RXITEN, an a interrupt request is generated when RXDONE is set. A transmitting station can send abort sequences under program control by setting the TXABORT bit. If the program response time to the TXDONE bit is excessive, the TXDATLAT bit is set and the transmitter idles abort characters.

#### 1.3.4 DDCMP Protocol

DDCMP (Digital Data Communications Message Protocol) was developed to provide full-duplex message transfer over standard existing hardware.

1.3.4.1 Controlling Data Transfers – The DDCMP message format is shown in Figure 1-2. A single control character is used in a DDCMP message, and is the first character in the message. Three control characters are provided in DDCMP to differentiate between the three possible types of messages:

SOH – data message follows

ENQ - control message follows

DLE - bootstrap message follows.

Note that the use of a fixed-length header and message-size declaration obviates the BSC requirement for extensive message and header delimiter codes.

Figure 1-3 shows a simple example of data exchange between the DUP11/PDP-11 and a data terminal. More efficient procedures can be derived after a study of DDCMP.

| SYN  | SYN | SOH  | COUNT   | FLAG   | RESPONSE | SEQUENCE | ADDRESS | CRC-1   | DATA                                       | CRC-2   |

|------|-----|------|---------|--------|----------|----------|---------|---------|--------------------------------------------|---------|

| 3114 | STN | 3011 | 14 BITS | 2 BITS | 8 BITS   | 8 BITS   | 8 BITS  | 16 BITS | (ANY NUMBER OF 8-BIT CHARACTERS UP TO 214) | 16 BITS |

11-2897

Figure 1-2 DDCMP Data Message Format

### DUP11/PDP-11 **TERMINAL** Sends a STRT (START) message which means: "I want to begin sending data to you and the sequence number of my first message will be 1."-Receives STRT message. Sends a STACK (Start Acknowledge) message which means: "OK with me; here is the first sequence number (5) I will use in sending data messages to you." Receives STACK Sends Data Messages with a response field set to 4 and the sequence field set to 1, which means: "I am looking for your message 1." Other messages may be sent at this time (i.e., messages 2, 3, etc.) without waiting for a response. Receives Data Message 1 and checks it for sequence and CRC errors. If there is a sequence error, go to 12. If there is no error, go to 9. A CRC error was detected. Computer B sends a NAK message with the response field set to 0, which means: "All messages up to 0 (Modulo 256) have been accepted and message 1 is in error." Computer A receives NAK, retransmits Message 1 and any other messages sent since (i.e., 2, 3, etc.) if already sent. Sends ACK response of 1 either in a separate ACK message or in the response field of a data message. Receives ACK and releases Message 1. Continues sending messages. Discard message and wait for proper Message 2. Times out because of lack of response for Message 2. Sends a reply for Message 2. Send NACK response of 1 in the response field. Retransmits Message 2 and following messages.

Figure 1-3 DDCMP Sample Handshaking Procedure

1.3.4.2 Error Checking and Recovery – DDCMP uses CRC-16 for detecting transmission errors. When an error occurs, DDCMP sends a separate NAK message. DDCMP does not require an acknowledgment message for all data messages. The number in the response field of a normal header, or in either the special NAK or ACK message, specifies the sequence number of the last good message received. For example, if messages 4, 5, and 6 have been received since the last time an acknowledgment was sent and message 6 is bad, the NAK message specifies number 5 which says "messages 4 and 5 are good and 6 is bad." When DDCMP operates in full-duplex mode, the line does not have to be turned around – the NAK is simply added to the sequence of messages for the transmitter.

When a sequence error occurs in DDCMP, the receiving station does not respond to the message. The transmitting station detects from the response field of the messages it receives (or via time-out) that the receiving station is still looking for a certain message and sends it again. For example, if the next message the receiver expects to receive is 5, but 6 is received, the receiver will not change the response field of its data messages, which contains 4. This says: "I accept all messages up through message 4 and I'm still looking for message 5."

- 1.3.4.3 Character Coding DDCMP uses ASCII control characters for SYN, SOH, ENQ and DLE. The remainder of the message, including the header, is transparent.

- 1.3.4.4 Data Transparency DDCMP defines transparency by use of a count field in the header. The header is of fixed length. The count in the header determines the length of the transparent information field, which can be 0 to 16,383 bytes long. To validate the header and count field, it is followed by a 16-bit CRC-16 field; all header characters are included in the CRC calculation. Once validated, the count is used to receive the data and to locate the second CRC-16 which is calculated on the datafield. Thus, character stuffing is avoided.

- 1.3.4.5 Data Channel Utilization DDCMP uses either full- or half-duplex circuits at optimum efficiency. In the full-duplex mode, DDCMP operates as two dependent one-way channels, each containing its own data stream. The acknowledgments are the only dependency which must be sent in the data stream in the opposite direction.

Separate ACK messages are unnecessary and reduce control overhead. Acknowledgments are simply placed in the response field of the next message for the opposite direction. If several messages are received correctly before the terminal is able to send a message, all of them can be acknowledged by one response. Only when a transmission error occurs, or when traffic in the opposite direction is light (no data message to send) is it necessary to send a special NAK or ACK message, respectively.

In summary, DDCMP data channel utilization features include:

- 1. Low control character overhead

- 2. No "character stuffing"

- 3. No separate ACKs when traffic is heavy saving on extra SYN characters and inter-message gaps

- 4. Multiple acknowledgments (up to 255) with one ACK

- 5. The ability to support point-to-point and multipoint lines.

- 1.3.4.6 Synchronization DDCMP achieves synchronization through the use of two ASCII SYN characters preceding the SOH, ENQ, or DLE. It is not necessary to synchronize between messages as long as no gap exists. Gaps are filled with SYN characters. Two sync characters are required but more are usually transmitted. If synchronization between messages is deliberately lost by sending PAD (all 1s) characters, the inter-message interval must be at least 14 character times in length.

- 1.3.4.7 Bootstrapping DDCMP has a bootstrap message as part of the protocol. It begins with the ASCII control character DLE. The information field contains the system reload programs and is totally transparent.

## CHAPTER 2 INSTALLATION

#### 2.1 SCOPE

This chapter provides information for installing and checking out a DUP11 Synchronous Line Interface.

#### 2.2 UNPACKING AND INSPECTION

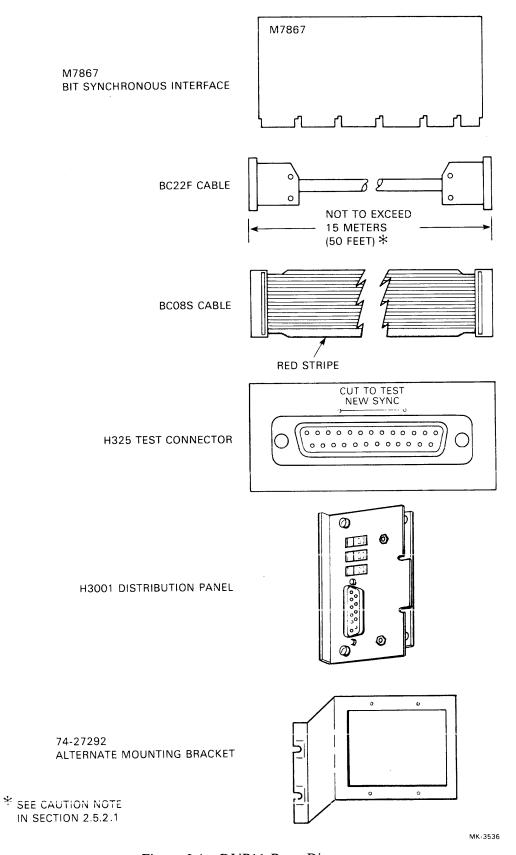

There is only one version of the DUP11 – the DUP11-DA; it consists of six items (refer to Figure 2-1).

M7867 Bit Synchronous Interface BC22F-25 Cable BC08S-10 Cable H325 Test Connector H3001 Distribution Panel 74-27292 Bracket\*

Inspect these parts for visible damage. Report any damage or shortage immediately to the shipper and the DIGITAL representative.

#### 2.3 TOOLS REQUIRED FOR INSTALLATION

The standard field service tool kit contains all the required tools for the installation of the DUP11.

#### 2.4 PREINSTALLATION SET-UP PROCEDURES

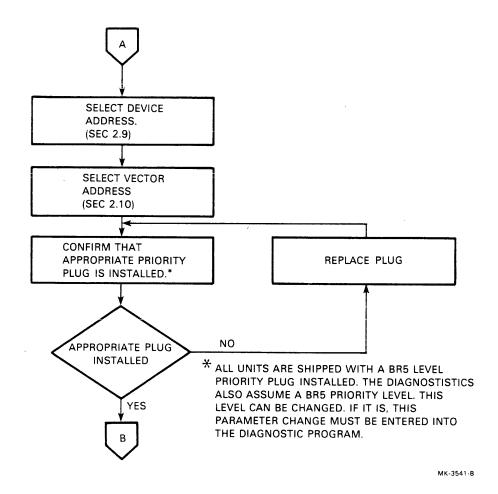

Before installing the DUP11 option, the following five steps must be performed.

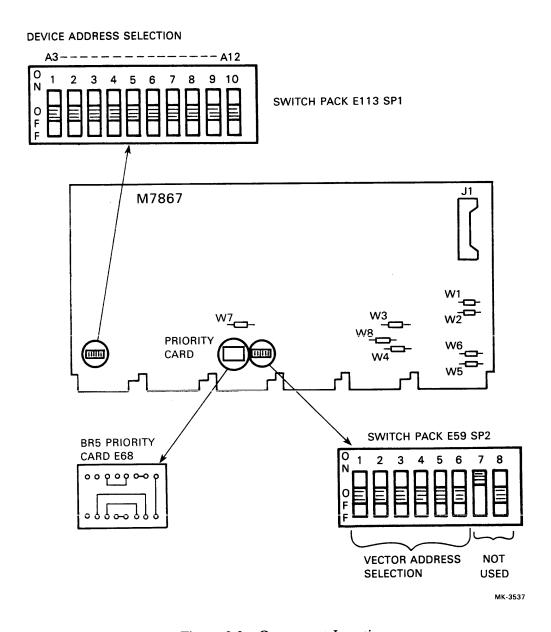

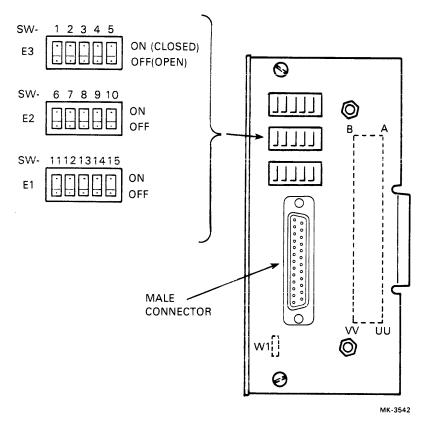

- 1. Examine the eight jumpers (W1 W8) on the M7867 module. Refer to Figure 2-2 to locate and identify the jumpers. All M7867 modules are shipped with the standard jumper configuration described in Table 2-1. All DUP11 diagnostics must be run on each M7867 utilizing the standard jumper configuration. After successfully completing the diagnostic testing in the shipped configuration, the M7867 may be reconfigured to meet the customer's requirements. MAINDEC CZDPE (DUP11 Quick Verify Test) should then be run to verify operation of the new configuration.

- 2. The DUP11 device address must be selected in accordance with Paragraph 2.9. For diagnostics, device address default = 760050.

- 3. The DUP11 vector address must be selected in accordance with Paragraph 2.10. For diagnostics, vector address default = 770.

<sup>\*</sup>Used in configurations not incorporating I/O bulkhead.

Figure 2-1 DUP11 Parts Diagram

Table 2-1 M7867 Jumper Configuration

| Jumper<br>Number | Standard<br>Configuration | Function                                                                                                                                                                                                                                                                                                                         |

|------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| W1               | Installed                 | Secondary Receive Enable – With this jumper installed, the state of the data set Secondary Received Data line is received by the DUP11. This jumper is used in conjunction with jumper W2. With this jumper removed, pin JJ of the Berg header is available for some other function.                                             |

| W2               | Removed                   | Secondary Receive Disable – This jumper must be removed when W1 is installed. Conversely, it must be installed when W1 is removed. When installed, the EIA SEC REC receiver input is grounded; however, this has no effect on the Berg header, cable, or data set.                                                               |

| W3               | Installed                 | Clear option – With this jumper removed, the following bits cannot be directly cleared by DEVICE RESET or BUS INIT.                                                                                                                                                                                                              |

|                  | 9                         | Secondary Transmit Data (RXCSR bit 3) Request to Send (RXCSR bit 2) Data Terminal Ready (RXCSR bit 1)                                                                                                                                                                                                                            |

|                  |                           | Some data sets may require that these connections be excluded from a device reset function.                                                                                                                                                                                                                                      |

| W4               | Installed                 | Secondary Transmit Enable – With this jumper installed, the state of the Secondary Transmit Data line is sent to the data set. With this jumper removed, this signal is disconnected at the output of the EIA driver. Some data sets do not use this signal.                                                                     |

| W5               | Removed                   | A Data Set Control – With this jumper removed, positive transitions on the Ring line and any transitions on the Clear to Send line set ADAT SET CH. This flag requests a receiver interrupt if the DSITEN bit has been set by the program. With this jumper installed, any transition on three additional lines set ADAT SET CH: |

|                  |                           | Carrier Data Set Ready Secondary Received Data                                                                                                                                                                                                                                                                                   |

| W6               | Installed                 | A and B Data Set Control – With this jumper installed, transitions on the Carrier, Data Set Ready, and Secondary Received Data lines set BDAT SET CH. This signal is a flag only and does not request interrupts. With this jumper removed, the BDAT SET CH flag (RXCSR bit 0) is inhibited.                                     |

| <b>W</b> 7       | Installed                 | NPR Latency Improvement – With this jumper installed, the NPR latency improvement circuit in the interrupt control logic is enabled. This jumper should be removed only if the DUP11 is installed in a system using a KA11 processor with no KH11 latency reduction option.                                                      |

| W8               | Installed                 | External Clock Enable - Remove for Bell 201A modem.                                                                                                                                                                                                                                                                              |

- 4. Confirm that a BR5 priority plug is installed in the module. The diagnostics assume a BR5 priority level (see Figure 2-2 to locate and identify the BR5 plug).

- 5. Set up the H3001 module in accordance with Paragraph 2.7.

#### 2.5 INSTALLATION

Installation of the DUP11 is treated in two paragraphs. Paragraph 2.5.1 contains instructions for installing the M7867 module. Paragraph 2.5.2 contains instructions for installing the H3001 distribution panel.

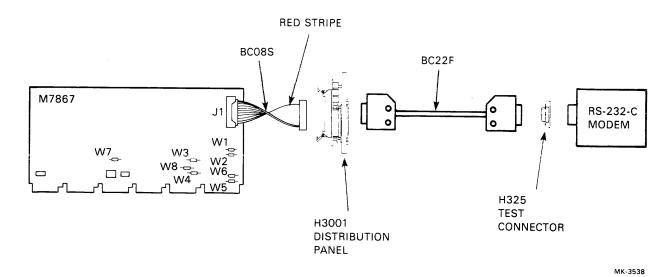

Examine Figure 2-3. This drawing shows the cabling configuration for the DUP11 installation.

Figure 2-2 Component Location

Figure 2-3 DUP11 Cabling

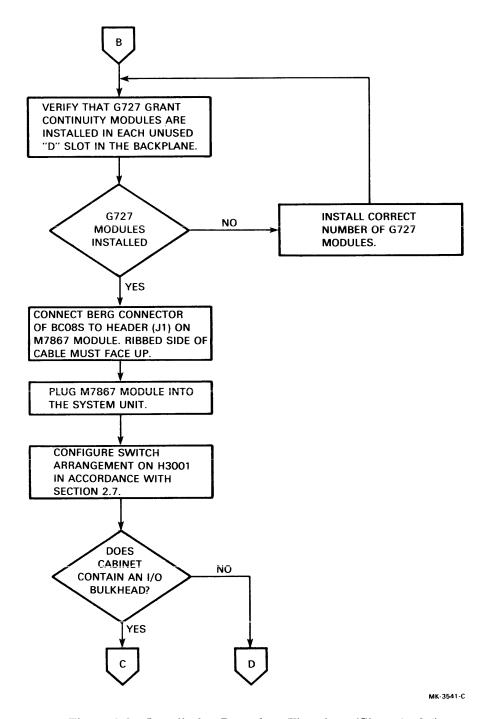

#### 2.5.1 M7867 Module Installation

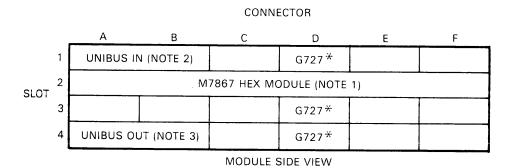

The DUP11 can be installed in any small peripheral controller (SPC) hex slot in the PDP-11 UNIBUS. Figure 2-4 shows the DD11-B system unit. This unit contains four slots but the DUP11 can only be installed in slots 2 and 3 because of the configuration of the prewired backplane.

## WARNING Turn all power OFF.

\*G727 GRANT CONTINUITY MODULE MUST BE INSTALLED IN EACH SLOT IN WHICH AN INTERFACE MODULE IS NOT INSTALLED.

#### NOTES

- 1. M7867 CAN BE MOUNTED ONLY IN SLOT 2 OR 3.

- 2. CAN BE M920 UNIBUS CONNECTOR OR BC11S UNIBUS CABLE.

- 3. CAN BE M920, BC11A, OR M930 UNIBUS TERMINATOR.

MK-3539

Figure 2-4 DUP11 (M7867 Module) Mounted in DD11-B

The M7867 installation procedure is as follows:

- 1. Connect the female Berg connector on the BC08S cable (ribbed side up) to the header on the M7867 module.

- 2. Plug the module into an SPC slot or into slot 2 or 3 of the DD11-B system unit.

#### 2.5.2 H3001 Distribution Panel Installation

Two different approaches to installing the H3001 distribution panel assembly are included in this manual.

FCC regulations necessitate the incorporation of I/O bulkheads in most new installations to limit electromagnetic interference (EMI) leakage. For installations utilizing an I/O bulkhead, follow the steps outlined in Paragraph 2.5.2.1.

Alternate instructions are included for non-FCC compliant cabinets that require a slightly modified installation procedure. If the system does not incorporate an I/O bulkhead, follow the procedures in Paragraph 2.5.2.2.

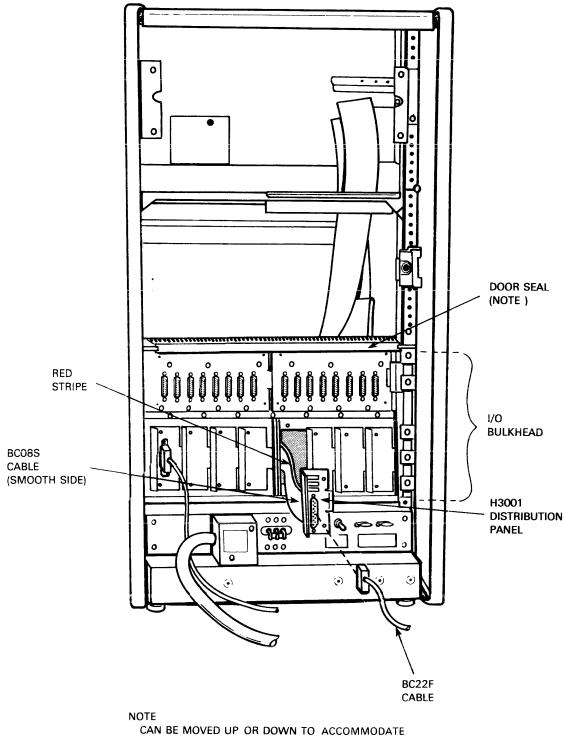

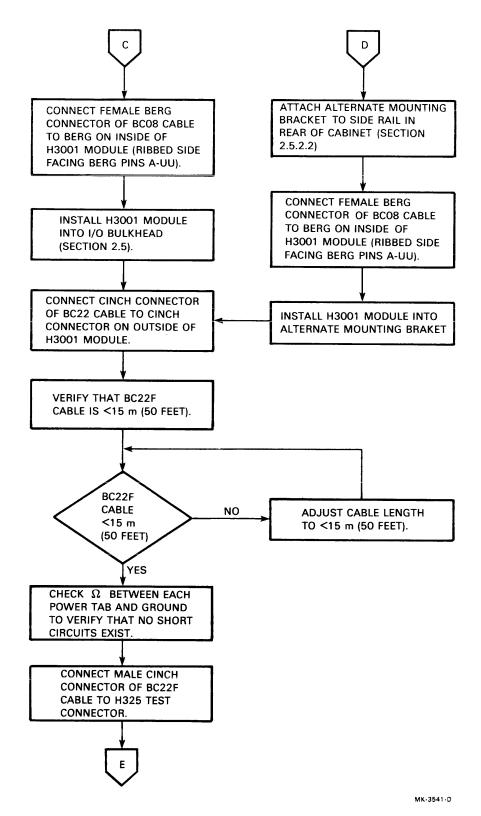

2.5.2.1 H3001 Installation In an I/O Bulkhead – The following instructions are for cabinets utilizing an I/O bulkhead. If a particular cabinet does not include an I/O bulkhead, omit these steps and follow the instructions in Paragraph 2.5.2.2.

Though there are differences in the orientation and positioning of I/O bulkheads of different levels of the PDP-11, the installation concept is the same. Once the H3001 distribution panel is installed, there should be no openings (panels omitted) left in the I/O frame on the rear of the cabinet which could permit EMI leakage. For this reason, it is important to tighten both mounting screws on the distribution panel. Figures 2-5 and 2-6 depict the various I/O bulkhead types and illustrate the correct approach to each.

- 1. Gain access to the I/O bulkhead through the door on the rear of the system cabinet and remove one of the 4.5 cm (2 in) wide panels on the bulkhead.

- 2. Route the remaining BC08S cable through the cabinet and through the opening in the I/O bulkhead at the rear of the cabinet. Keep in mind that the cable must be routed and dressed in a manner compatible with the existing cabinet cabling.

- 3. Plug the connector on the free end of the BC08S cable into the Berg connector on the rear of the H3001 distribution panel. Make sure that the ribbed side of the cable faces the pins lettered A to UU (not B to VV) of the Berg connector (see Figure 2-9). This assures pin to pin correspondence between the connectors of the M7867 and H3001 modules.

- 4. Install the panel into the opening of the I/O bulkhead in place of the 4.5 cm (2 in) panel that was removed in Step 1.

#### NOTE

It is imperative to maintain an interference-free environment outside the cabinet enclosure. Any additional panels that may have been removed to facilitate easier installation of the H3001 must be replaced in order to maintain the integrity of the I/O bulkhead.

ADDITION OF, OR REMOVAL OF I/O FRAMES.

MK-3875

Figure 2-5 H3001 Installation in a Horizontally Oriented I/O Bulkhead

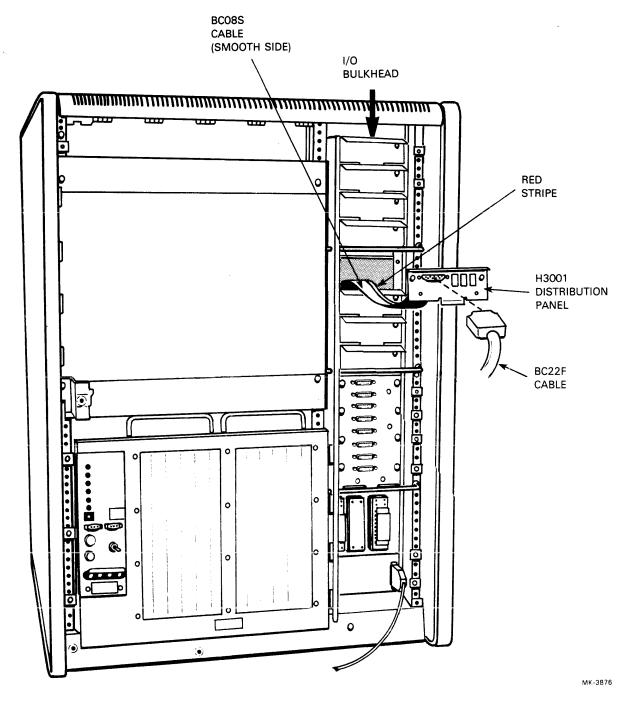

Figure 2-6 H3001 Installation in a Vertically Oriented I/O Bulkhead

5. Connect the female Cinch connector of the BC22F cable to the 25-pin Cinch connector on the rear of the H3001 module. The cable should exit the cabinet with the other signal cables.

#### **CAUTION**

BC22F cable lengths in excess of 7.62 meters (25 feet) may exceed the maximum load capacitance defined by the RS-232-C specification. Note, however, that up to 15 meters (50 feet) provides satisfactory DUP11 performance levels.

- 6. Connect the other end of the BC22F cable to the modem or to the H325 test connector which is the configuration assumed by the diagnostics.

- 7. Turn power ON.

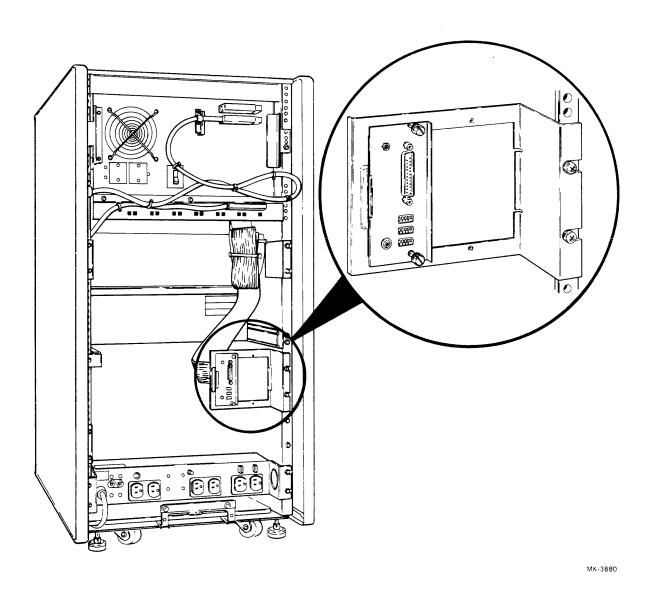

#### 2.5.2.2 H3001 Installation in Cabinets Without an I/O Bulkhead -

- 1. Gain access to the rear of the system cabinet and mount the bracket (Part No. 74-27292) to one of the rear side rails as shown in Figure 2-7. Mount the H3001 distribution panel into the bracket.

- 2. Route the remaining BC08S cable through the cabinet and to the bracket at the rear of the cabinet. Keep in mind that the cable must be routed and dressed in a manner compatible with the existing cabinet cabling.

- 3. Plug the connector on the free end of the BCO8S cable into the Berg connector on the rear of the H3001 distribution panel. Make sure that the ribbed side of the cable faces the pins lettered A to UU (not B to VV) of the Berg connector (see Figure 2-9). This assures pin to pin correspondence between the connectors of the M7867 and H3001 modules.

- 4. Connect the female Cinch connector of the BC22F cable to the 25-pin Cinch connector on the rear of the H3001 module. The cable should exit the cabinet with the other signal cables.

#### **CAUTION**

BC22F cable lengths in excess of 7.62 meters (25 feet) may exceed the maximum load capacitance defined by the RS-232-C specification. Note, however, that up to 15 meters (50 feet) provides satisfactory DUP11 performance levels.

- 5. Connect the other end of the BC22F cable to the modem or to the H325 test connector which is the configuration assumed by the diagnostics.

- 6. Configure the H3001 panel switches according to the chart in Table 2-2.

- 7. Turn power ON.

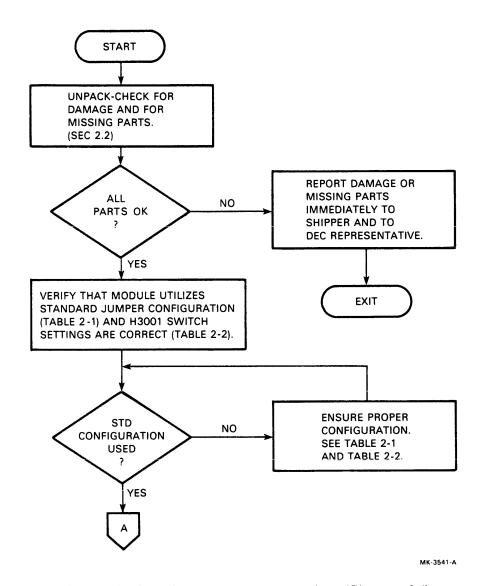

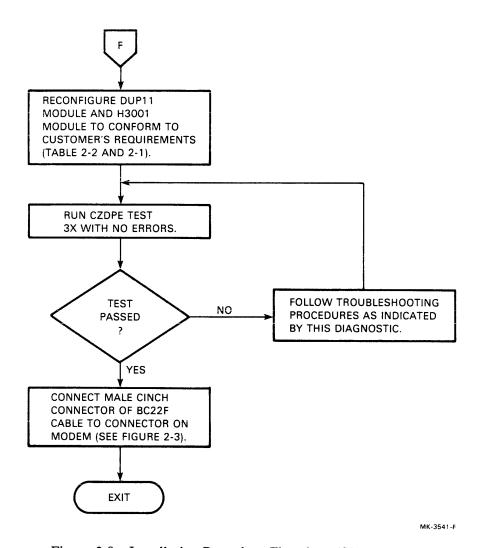

Figure 2-8 is included for convenience. Use this figure for quick reference when installing the DUP11 option.

Figure 2-7 Side Rail Installation of H3001 Distribution Panel

Table 2-2 H3001 Switch Settings

|     | SELL 3 | Series Solice | 880 / SELL 3 | \$60, 000, \$7.60 |  |

|-----|--------|---------------|--------------|-------------------|--|

| S1  |        |               |              | ON                |  |

| S2  |        |               |              |                   |  |

| S3  |        |               |              |                   |  |

| S4  |        |               |              |                   |  |

| S5  |        |               |              | ON                |  |

| S6  |        |               |              |                   |  |

| S7  |        |               |              |                   |  |

| S8  |        |               |              |                   |  |

| S9  |        |               |              |                   |  |

| S10 | *      |               |              |                   |  |

| S11 |        |               |              |                   |  |

| S12 |        |               |              |                   |  |

| S13 |        |               |              |                   |  |

| S14 |        |               |              |                   |  |

| S15 |        |               |              |                   |  |

SWITCHES ARE OFF UNLESS OTHERWISE INDICATED

MK-3838

$<sup>\</sup>stackrel{\textstyle \star}{\sim}$  ON IF NEW SYNC CONFIGURED ON M7867

Figure 2-8 Installation Procedure Flowchart (Sheet 1 of 6)

Figure 2-8 Installation Procedure Flowchart (Sheet 2 of 6)

Figure 2-8 Installation Procedure Flowchart (Sheet 3 of 6)

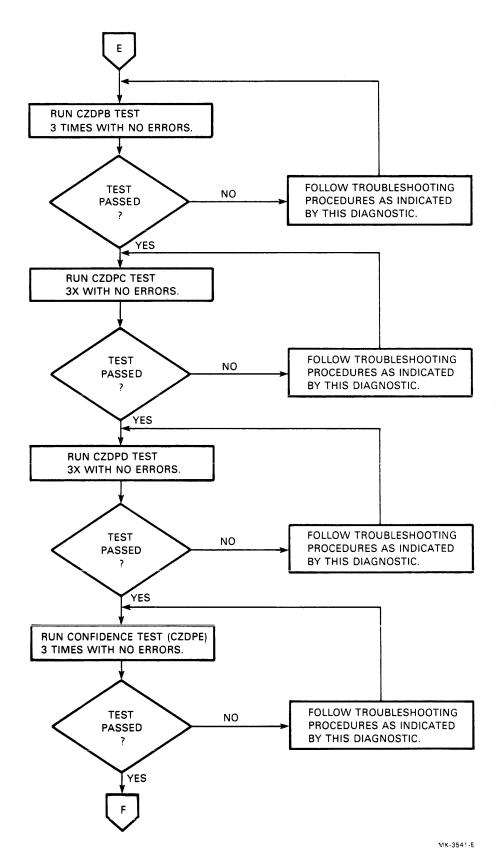

Figure 2-8 Installation Procedure Flowchart (Sheet 4 of 6)

Figure 2-8 Installation Procedure Flowchart (Sheet 5 of 6)

Figure 2-8 Installation Procedure Flowchart (Sheet 6 of 6)

#### 2.6 VERIFICATION OF HARDWARE OPERATION

Verification of proper DUP11 operation is performed by a series of diagnostic programs. A general description of the diagnostics is included in Chapter 5 of the technical manual. Details on the content and use of the diagnostics is contained in the diagnostic documentation package supplied with the DUP11.

Proceed as follows:

1. Run the following diagnostics in the following order:

CZDPB – Basic and Off-line Transmitter Tests

CZDPC - Off-line and SDLC Receiver Tests and Off-line Modem Control and Interrupt Tests

CZDPD – Off-line SDLC and DEC MODE Data and Function Tests

2. Run diagnostic CZDPE. This is a confidence test that requires a dialog with the user to ensure proper setting of the DUP11 and system parameters. It offers a quick test to verify that the DUP11 is operational.

Each diagnostic must make three passes without an error.

Reconfigure the H3001 and the DUP11 in accordance with the customer's requirements (Tables 2-1 and 2-2). Then run diagnostic CZDPE (DUP11 quick verify test) to check the final configuration.

System testing consists of running DECX11 module CXDPB to exercise all DUP11s in a system. Run DECX11 until three error-free passes of module CXDPB are obtained. Note that only four DUP11s can be tested with one DECX11 module.

#### 2.7 COMPATIBILITY

The DUP11 is compatible with the DF03 and Bell type  $201^{tm}$ ,  $208^{tm}$ , and  $209^{tm}$  modems or equivalent. In addition, compatibility with these and other modems is enhanced through the incorporation of the H3001 distribution panel.

Adjust the switches on the H3001 to correspond to the settings indicated in Table 2-2 for the particular modem used in your configuration. The H3001 switches are contained in three DIP switch packages grouped together on the H3001 modules. Refer to Figure 2-9 for the location of these switches. The switches are rocker or slide type and are pushed to the desired position.

A schematic of the H3001 distribution panel is included in Chapter 5 (Figure 5-1) of the technical manual. Use this figure as an aid in determining the proper switch settings and jumper configuration if the modem used is not listed in Table 2-2.

Jumper W1 (see Figure 2-9) is normally not installed. Install this jumper when RS-232 protective ground (pin 1 of Cinch connector) must be connected to enclosure ground. Note that this may introduce an undesirable ground loop.

Figure 2-9 H3001 Distribution Panel

#### **NOTE**

Due to the extensive variety of modems currently available, DIGITAL cannot guarantee that the DUP11 interface will fully support all features of every modem.

#### 2.8 POWER REQUIREMENTS

The DUP11 requires the following power:

+5 V at 3.6 A +15 V at 75 mA -15 V at 75 mA

#### 2.9 DEVICE ADDRESSES

#### 2.9.1 Introduction

Starting with the DJ11, new communications devices are to be assigned floating addresses. The addresses for current production devices are to be retained. The word *floating* means that addresses are not assigned absolutely for the maximum number of each communications device that can be used in a system.

#### 2.9.2 Floating Device Address Assignment

Floating device addresses are assigned as follows:

- 1. The floating address space starts at location 760010 and extends to location 764000 (octal designations).

- 2. The devices are assigned in order by type: DJ11, DH11, DQ11, DU11, and DUP11; then the next device is introduced into production. Multiple devices of the same type must be assigned contiguous addresses.

- 3. The first address of a new type device must start on a modulo 10<sub>8</sub> boundary, if it contains one to four bus-addressable registers. The starting address of the DH11 must be on a modulo 20<sub>8</sub> boundary because the DH11 has eight registers.

- 4. A gap of 10<sub>8</sub>, starting on a modulo 10<sub>8</sub> boundary, must be left between the last address of one type device and the first address of the next type device. A gap must be left for any device on the list that is not used if the device following it is used. The equivalent of a gap should be left after the last assigned device to indicate that nothing follows.

- 5. A new type device cannot be inserted ahead of a device on the list.

- 6. If additional devices on the list are to be added to a system, they must be assigned contiguously after the original devices of the same type. Reassignment of other type devices already in the system may be required to make room for the additions.

The following examples show typical floating device assignments for communications devices in a system:

#### EXAMPLE 1: No DJ11s, 2 DH11s, 2 DQ11s, and 1 DUP11

```

760010

DJ11 gap

DH11 #0 first address

760020

DH11 #1 first address

760040

760060

DH11 gap

DO11 #0 first address

760070

760110

DQ11 gap

760120

DU11 gap

760130

DUP11 #0 first address

Indicates no more DUP11s and no other devices follow.

760140

```

## EXAMPLE 2: 1 DJ11, 1 DH11, 2 DQ11s, and DUP11s

```

DJ11 #0 first address

760010

760020

DJ11 gap

DH11 #0 first address

760040

760060

DH11 gap

DQ11 #0 first address

760070

DQ11 #1 first address

760100

760110

DQ11 gap

DUP11 gap

760120

DUP11 #0 first address

760130

DUP11 #1 first address

760140

Indicates no more DUP11s and no other devices follow.

760150

```

#### **EXAMPLE 3: 1 DUP11**

| 760010 | DJ11 gap                                              |

|--------|-------------------------------------------------------|

| 760020 | DH11 gap                                              |

| 760030 | DQ11 gap                                              |

| 760040 | DU11 gap                                              |

| 760050 | DUP11 #0 first address                                |

| 760060 | Indicates no more DUP11s and no other devices follow. |

#### 2.9.3 Device Address Selection

In the floating address space (760010-764000), bits 13-17 are always 1s (function of PDP-11 processor). Appendix B of the technical manual shows the PDP-11 memory organization and addressing conventions. Bits 3-12 are selected by switches in the address decoding logic (Table 2-3). With the switch ON (closed), the decoder looks for a 0 on the associated UNIBUS address line; conversely, with the switch OFF (open), the decoder looks for a 1 on the associated UNIBUS address line. Bits 1 and 2 are decoded to select one of four registers. They determine the least significant digit (octal) of the device address because bit 0 is not used for address decoding. It is used to select the proper byte during byte transactions.

Table 2-3 Guide for Setting Switches to Select Device Address

| Switch No. | 10 | 9  | 8  | 7 | 6 | 5_ | 4 | 3 | 2 | 1 | Device  |

|------------|----|----|----|---|---|----|---|---|---|---|---------|

| Bit No.    | 12 | 11 | 10 | 9 | 8 | 7  | 6 | 5 | 4 | 3 | Address |

|            |    |    |    |   |   |    |   |   |   | X | 760010  |

|            |    |    |    |   |   |    |   |   | X |   | 760020  |

|            |    |    |    |   |   | 1  |   |   | X | X | 760030  |

|            |    |    |    |   |   |    |   | X | 1 |   | 760040  |

|            |    |    |    |   |   |    |   | X |   | X | 760050  |

|            |    |    |    |   |   |    |   | X | X |   | 760060  |

|            |    |    |    |   |   |    |   | X | X | X | 760070  |

|            |    |    |    |   |   |    | X |   |   |   | 760100  |

|            |    |    |    |   |   | Х  |   |   |   |   | 760200  |

|            |    |    |    |   |   | X  | x |   |   |   | 760300  |

|            |    |    |    |   | X |    |   |   |   |   | 760400  |

|            |    |    |    |   | X |    | x |   |   |   | 760500  |

|            |    |    |    |   | X | X  |   |   | - |   | 760600  |

|            |    |    |    |   | X | X  | Х |   |   |   | 760700  |

|            |    |    |    | X |   |    |   |   |   |   | 761000  |

|            |    |    | х  |   |   |    |   |   |   |   | 762000  |

|            |    |    | х  | x |   |    |   |   |   |   | 763000  |

|            |    | x  |    |   |   |    |   |   |   |   | 764000  |

Notes:

<sup>1.</sup> X means switch off (open) to respond to logical 1 on the Unibus.

<sup>2.</sup> Switch numbers are physical positions in switch package 1.

#### Switch Identification

The device address selection switches are contained in one DIP switch package (E113). Refer to Figure 2-2 for the location of the package. All ten switches in the package are used. The correlation between switch numbers and bit numbers is shown in Table 2-3. The ON and OFF positions and the switch numbers are marked on the package. The switches are rocker or slide type and are pushed to the desired position.

The DUP11 requires four addresses:

- 76XXX0 Receiver Control and Status Register

- 76XXX2 Receiver Data Buffer Register (Read Only) and Parameter Control and Status Register (Write Only)

- 76XXX4 Transmitter Control and Status Register

- 76XXX6 Transmitter Data Buffer Register

### 2.10 VECTOR ADDRESSES

### 2.10.1 Introduction

Communications devices are assigned floating vector addresses. This eliminates the necessity of assigning addresses absolutely for the maximum number of each device that can be used in the system.

### 2.10.2 Floating Vector Address Assignment

Floating vector addresses are assigned as follows:

- The floating address space starts at location 300 and proceeds upward to 777. Addresses 500-534 are reserved.

- The devices are assigned in order by type: DC11; KL11/DL11-A, -B; DP11; DM11-A; DN11; DM11-BB; DR11-A; DR11-C; PA611 Reader; PA611 Punch; DT11; DX11; DL11-C, -D -E; DJ11; DH11; GT40; LPS11; VT20; DQ11; KW11-W; DU11; DUP11; and DV11.

- If any type device is not used in a system, address assignments move up to fill the vacancies.

- If additional devices are to be added to the system, they must be assigned contiguously after the original devices of the same type. Reassignment of other type devices already in the system may be required.

### 2.10.3 Vector Address Selection

Each device interrupt vector requires four address locations (two words) which implies only even-numbered addresses. A further constraint is that all vector addresses must end in 0 or 4. The vector address is specified as a three-digit, binary-coded, octal number using UNIBUS data bits 0-8. Because the vector must end in 0 or 4, bits 1 or 0 are not specified (they are always 0) and bit 2 determines the least significant octal digit of the vector address (0 or 4). The interrupt control logic sends only seven bits (2-8) to the PDP-11 processor to represent the vector address.

The DUP11 is shipped with a BR5 priority selection plug installed in the interrupt control logic. This logic generates two vector addresses: receiver interrupts generate vector addresses of the form XX0, and transmitter interrupts generate vector addresses of the form XX4. For this method of operation, the state of bit 2 is selected by the logic, not by a switch. The two most significant octal digits of the vector address are determined by switches in lines 3-8 (Table 2-4). With the switch OFF (open), a 0 is generated on the associated UNIBUS data line; with the switch ON (closed), a 1 is generated on the associated UNIBUS data line. Also, the NPR jumper (W7) in this logic is left in to improve NPR latency time.

Table 2-4 Guide for Setting Switches to Select Vector Address

| Switch No. Bit No. | 1 8    | 7 | 3   | 4 5 | 5 4 | 6  | Vector<br>Address |

|--------------------|--------|---|-----|-----|-----|----|-------------------|

|                    | X      |   |     | X   | X   | X  | 300               |

|                    | X      |   | İ   | X   | X   | ^* | 310               |

|                    | X<br>X |   |     | X   | 1.  | X  | 320               |

|                    | X      |   |     | X   |     | ^  | 330               |

|                    | X      |   |     |     | X   | X  | 340               |

|                    | X      |   |     |     | X   | 1. | 350               |

|                    | X      |   | ŀ   |     |     | X  | 360               |

|                    | X      |   |     |     |     | 1. | 370               |

|                    |        | X | X   | X   | X   | X  | 400               |

|                    |        |   |     |     | **  | 1. |                   |

|                    |        | X |     | X   | X   | X  | 500               |

|                    |        |   |     | 1   | 1   | 1  |                   |

|                    |        |   | X   | X   | X   | X  | 600               |

|                    |        |   | - 1 | -1  | 1   | 1  |                   |

|                    |        |   |     | X   | Х   | X  | 700               |

#### Notes:

- 1. X means switch off (open) to produce a logical 0 on the Unibus.

- 2. Switch numbers are physical positions in switch package 2.

### **Switch Identification**

The vector address selection switches are contained in one DIP switch package (E59). Refer to Figure 2-2 for the location of the package. Only six of the eight switches in the package are used. The correlation between switch numbers and bit numbers is shown in Table 2-4. The ON and OFF positions and the switch numbers are marked on the package. The switches are rocker or slide type and are pushed to the desired position.

# **CHAPTER 3 REGISTER DESCRIPTIONS** AND OPERATING FEATURES

#### 3.1 INTRODUCTION

This chapter describes the bit assignments for the five DUP11 Registers.

#### 3.2 DUP11 REGISTERS AND DEVICE ADDRESS SELECTION

The five registers used in the DUP11 are shown in Table 3-1. There is no conflict in assigning the same address (76XXX2) to two registers because the RXDBUF is read-only and the PARCSR is write-only.

Communications devices are assigned floating device addresses in the range 760010 to 764000. Rules for assigning floating device addresses are contained in Chapter 2.

#### 3.3 INTERRUPT VECTORS

The DUP11 generates two vector addresses: receiver interrupts (REQ A) generate vector addresses of the form XX0, and transmitter interrupts (REQ B) generate vector addresses of the form XX4.

Communications devices are assigned floating vector addresses in the range 300-777 (500-534 are reserved). Rules for assigning floating vector addresses are contained in Chapter 2.

### 3.4 PRIORITY SELECTION

The priority selection (BR level) for receiver and transmitter interrupts is selectable on the module via a plug-in priority selection card. The DUP11 is shipped with a priority 5 card installed that establishes BR5 as the bus request level for interrupts.

### 3.5 REGISTER BIT ASSIGNMENTS

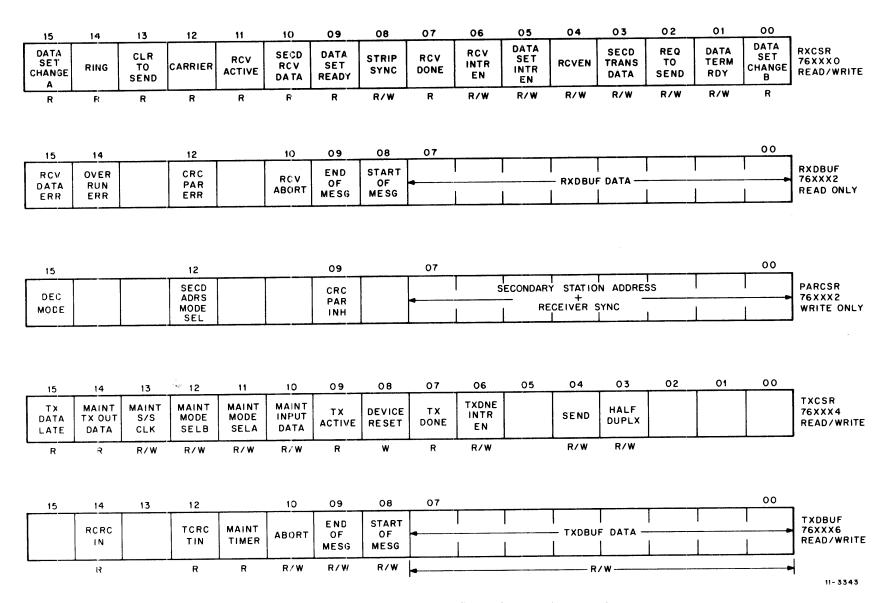

Bit assignments for the five DUP11 registers are shown in Figure 3-1. Each register is described by showing a bit assignment illustration and an accompanying table that discusses each bit in detail.

Table 3-1 DUP11 Registers

2.4

| Register Name                  | Mnemonic | Address | Comments                                   |

|--------------------------------|----------|---------|--------------------------------------------|

| Receiver Control and Status    | RXCSR    | 76XXX0  | Word- and byte-addressable.<br>Read/write. |

| Receiver Data Buffer           | RXDBUF   | 76XXX2  | Word-addressable. Read-only.               |

| Parameter Control and Status   | PARCSR   | 76XXX2  | Word-addressable. Write-only.              |

| Transmitter Control and Status | TXCSR    | 76XXX4  | Word- and byte-addressable.<br>Read/write. |

| Transmitter Data Buffer        | TXDBUF   | 76XXX6  | Word- and byte-addressable.<br>Read/write. |

Figure 3-1 DUP11 Register Configurations and Bit Assignments

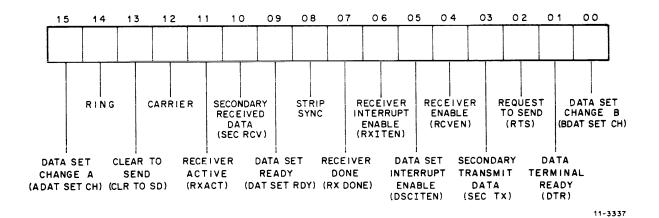

Figure 3-2 Receiver Control and Status Register Format

Table 3-2 Bit Descriptions for Receiver Control and Status Register (RXCSR) (Refer to Figure 3-2)

|     | (Refer to Figure 3-2)              |                                                                                                                                                                                                                                    |  |

|-----|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit | Name                               | Description                                                                                                                                                                                                                        |  |

| 15  | ADAT SET CH<br>(Data Set Change A) | This bit is set when any of the following transitions occur on the data set control lines.                                                                                                                                         |  |

|     |                                    | A positive transition on the Ring line greater than 10 ms.                                                                                                                                                                         |  |

|     |                                    | Any transition on the Clear to Send line.                                                                                                                                                                                          |  |

|     |                                    | An optional jumper modification allows this bit to be set by any of the following transitions. This modification is a field installation change supported by diagnostics.                                                          |  |

|     |                                    | Any transitions of the Carrier line                                                                                                                                                                                                |  |

|     |                                    | Any transitions of the Data Set Ready line                                                                                                                                                                                         |  |

|     |                                    | Any transitions of the Secondary Received Data line                                                                                                                                                                                |  |

|     |                                    | Normally these three transitions cause the Data Set Change B bit to be set in this register. If the jumper modification is made, this bit is disabled.                                                                             |  |

|     |                                    | If bit 05 (Data Set Interrupt Enable) of this register is set, the assertion of this bit causes an interrupt to the receiver vector. This bit is program read only and is cleared by INIT, device reset or when the RXCSR is read. |  |

| 14  | RING                               | This bit reflects the state of the modem Ring line. Any positive transition of this line greater than 10 ms causes the Data Set Change A bit to be set.                                                                            |  |

|     |                                    | This bit is program read-only.                                                                                                                                                                                                     |  |

Table 3-2 Bit Descriptions for Receiver Control and Status Register (RXCSR) (Cont) (Refer to Figure 3-2)

| Bit | Name                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13  | CLR TO SD<br>(Clear to Send) | This bit reflects the state of the Clear to Send line of the modem. Any transition of this line causes the Data Set Change A bit to be set.                                                                                                                                                                                                                                                                                                                                                   |

|     |                              | This bit is program read only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 12  | CARRIER                      | This bit is a direct reflection of the modem carrier. Any change in the state of this line causes Data Set Change B to be set unless the data set change jumper modification has been made. (Refer to bit 15 of this register.)                                                                                                                                                                                                                                                               |

|     |                              | This bit is program read only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11  | RXACT<br>(Receiver Active)   | The function of this bit is to reflect the current state of the receiver logic in accordance with the selected mode of operation as defined by the contents of the PARCSR.                                                                                                                                                                                                                                                                                                                    |

|     |                              | SDLC or ADCCP Protocol:                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |                              | In the SDLC or ADCCP mode of operation, (i.e., DEC MODE cleared) this bit is set by the DUP11 logic when the first character of a message frame is being received. CRC computation is performed for all data received, if not inhibited.                                                                                                                                                                                                                                                      |

|     |                              | If the SECD ADRS MS (Secondary Mode Address Select) bit in the PARCSR is cleared, the receiver's operating mode is that of a primary station. In this mode of operation, the RXACT bit stays asserted until the terminating flag character is received. At this time the RXACT bit is cleared and the REOM bit is asserted. The internal receiver CRC register is tested for an error condition and re-initialized at this time in preparation for the next message, if CRC is not inhibited. |

|     |                              | If an Abort sequence is not received prior to the terminating flag, the RXACT bit is re-asserted when the first data character of the next message is received. The RSOM bit will appear with this character. Any inter-message flag characters are ignored by the receiver.                                                                                                                                                                                                                  |

|     |                              | With the Secondary Address Mode Select bit asserted in the PARCSR, the receiving station operates as a secondary station. The major difference between the primary and secondary modes, as far as the DUP11 hardware is concerned, is the character subsequent to the last initial flag character. In secondary mode, this character must match the contents of the low byte of the PARCSR; if not, the RXACT will not be set and the receiver logic searches for the next flag sequence.     |

Table 3-2 Bit Descriptions for Receiver Control and Status Register (RXCSR) (Cont) (Refer to Figure 3-2)

| Bit | Name                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                                         | If extended secondary addressing is implemented in a system, (i.e., 16-bit addresses), the second byte of the address must be recognized by the software.                                                                                                                                                                                                                                                                                                                                                       |

|     |                                         | DDCMP or BISYNC Protocol:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |                                         | Setting the DEC MODE bit in the PARCSR causes the DUP11 to operate in a manner compatible to the DDCMP or BISYNC family protocols.                                                                                                                                                                                                                                                                                                                                                                              |

|     |                                         | The low byte of the PARCSR must be loaded with the SYNC character being utilized by the system. This regiter is used only by the receiver logic for comparison purposes. It is not utilized by the transmitter logic.                                                                                                                                                                                                                                                                                           |

|     |                                         | When the RCVEN bit is asserted, the receiver logic searches the received data stream for two consecutive SYNC characters. When two consecutive SYNC characters have been recognized, the receiver is to be considered synchronized to the transmitting station. At this time, all characters subsequent to the two SYNC characters that caused the synchronization are presented to the program (i.e., RXDONE is set) conditional on the character and the state of the STRIP SYNC bit asserted by the program. |

|     |                                         | The RXACT bit is normally asserted when the first character is received subsequent to the synchronization process, unless the STRIP SYNC bit is set. If STRIP SYNC is set, the assertion of RXACT by the DUP11 logic is delayed until the first non-sync character is received. Once RXACT is asserted, the CRC detection logic is activated, provided it is not inhibited in the PARCSR (bit 9) and the STRIP SYNC function is disabled internally.                                                            |

|     |                                         | When the completion of the message has been detected, the program must clear the RCVEN bit to re-initialize the receiver. Clearing the RCVEN bit causes the RXACT bit to be cleared also.                                                                                                                                                                                                                                                                                                                       |

|     |                                         | This bit is program read only and is cleared by INIT, device reset, an off transition of RCVEN, and an ABORT sequence is received in the SDLC or ADCCP mode.                                                                                                                                                                                                                                                                                                                                                    |

| 10  | SEC RCV<br>(Secondary Received<br>Data) | This bit reflects the state of the Secondary Received Data line from the modem. Any transition on this line causes the Data Set Change B bit to be set unless the data set change jumper modification has been installed. Refer to bit 15 of this register.                                                                                                                                                                                                                                                     |

|     |                                         | Used with certain modems only. This bit is program read only.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Table 3-2 Bit Descriptions for Receiver Control and Status Register (RXCSR) (Cont) (Refer to Figure 3-2)