# DUP11 Bit Synchronous Interface Maintenance Manual

# DUP11 Bit Synchronous Interface Maintenance Manual

# Copyright © 1975, 1976, 1982 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DIGITAL | DECsystem-10     | MASSBUS        |

|---------|------------------|----------------|

| DEC     | DECSYSTEM-20     | <b>OMNIBUS</b> |

| PDP     | DIBOL            | OS/8           |

| DECUS   | <b>EDUSYSTEM</b> | RSTS           |

| UNIBUS  | VAX              | RSX            |

|         | VMS              | IAS            |

# EDUCATIONAL SERVICES DEVELOPMENT AND PUBLISHING UPDATE NOTICE

# DUP11 BIT SYNCHRONOUS INTERFACE MAINTENANCE MANUAL EK-DUP11-MM-CN1 OCTOBER 1983

Insert this Update Notice Page in the manual, directly following the Title Page, as a means of maintaining an up-to-date record of changes to the manual.

Copyright © 1983 Digital Equipment Corporation

#### **INSTRUCTIONS**

The following appendix is to be placed as the final appendix in your manual.

### **CONTENTS**

|           |                                       | Page         |

|-----------|---------------------------------------|--------------|

| CHAPTER 1 | INTRODUCTION                          |              |

| 1.1       | SCOPE                                 | 1-1          |

| 1.2       | DUP11 GENERAL DESCRIPTION             |              |

| 1.3       | SDLC AND DDCMP PROTOCOLS              |              |

| 1.3.1     | Introduction                          |              |

| 1.3.2     | General Information                   |              |

| 1.3.3     | SDLC Protocol Description             |              |

| 1.3.3.1   | Message Format                        |              |

| 1.3.3.1   | Abort Sequence                        |              |

|           | DDCMP Protocol                        |              |

| 1.3.4     |                                       |              |

| 1.3.4.1   | Controlling Data Transfers            |              |

| 1.3.4.2   | Error Checking and Recovery           |              |

| 1.3.4.3   | Character Coding                      |              |

| 1.3.4.4   | Data Transparency                     |              |

| 1.3.4.5   | Data Channel Utilization              |              |

| 1.3.4.6   | Synchronization                       | 1-8          |

| 1.3.4.7   | Bootstrapping                         | 1-8          |

| 1.4       | BASICS OF CYCLE REDUNDANCY CHECKING   |              |

| 1.4.1     | Mathematical Background               |              |

| 1.4.2     | Hardware Implementation of CRC        | 1-9          |

| 1.4.3     | CRC Operation in DDCMP Protocol       | 1-9          |

| 1.4.4     | CRC Operation in SDLC Protocol        | 1-10         |

| CHAPTER 2 | INSTALLATION                          |              |

| 2.1       | SCOPE                                 | 2-1          |

| 2.2       | UNPACKING AND INSPECTION              |              |

| 2.3       | TOOLS REQUIRED FOR INSTALLATION       |              |

| 2.4       | PREINSTALLATION SET-UP PROCEDURES     | 2-1          |

| 2.5       | INSTALLATION                          |              |

| 2.5.1     | M7867 Module Installation             |              |

| 2.5.1     | H3001 Distribution Panel Installation |              |

| 2.5.2.1   | H2001 Installation in an I/O Bulkhead |              |

|           | H3001 Installation in an I/O Bulkhead | 2-0<br>2_0   |

| 2.5.2.2   | VERIFICATION OF HARDWARE OPERATION    | 2-5<br>2 1 S |

| 2.6       |                                       |              |

| 2.7       | COMPATIBILITYPOWER REQUIREMENTS       | Z-10         |

| 2.8       | POWER REQUIREMENTS                    | 2-17         |

| 2.9       | DEVICE ADDRESSES                      |              |

| 2.9.1     | Introduction                          | 2-19         |

| 2.9.2     | Floating Device Address Assignment    | 2-20         |

| 2.9.3     | Device Address Selection              |              |

| 2.10      | VECTOR ADDRESSES                      |              |

| 2.10.1    | Introduction                          | 2-22         |

| 2.10.2    | Floating Vector Address Assignment    | 2-22         |

| 2.10.3    | Vector Address Selection              | 2-22         |

## **CONTENTS (Cont)**

|           |                                                                    | Page |

|-----------|--------------------------------------------------------------------|------|

| CHAPTER 3 | REGISTER DESCRIPTIONS AND PROGRAMMING INFORMATION                  |      |

| 3.1       | INTRODUCTION                                                       | 3-1  |

| 3.2       | DUP11 REGISTERS AND DEVICE ADDRESS SELECTION                       | 3-1  |

| 3.3       | INTERRUPT VECTORS                                                  |      |

| 3.4       | PRIORITY SELECTION                                                 |      |

| 3.5       | REGISTER BIT ASSIGNMENTS                                           | 3-1  |

| 3.6       | TYPICAL TEST PROGRAMS                                              | 3-23 |

| CHAPTER 4 | THEORY OF OPERATION                                                |      |

| 4.1       | INTRODUCTION                                                       | 4-1  |

| 4.2       | FUNCTIONAL DESCRIPTION                                             | 4-1  |

| 4.2.1     | Logic Description                                                  |      |

| 4.2.1.1   | Registers                                                          |      |

| 4.2.1.2   | Device Reset Logic                                                 |      |

| 4.2.1.3   | Address Selection Logic                                            |      |

| 4.2.1.4   | Unibus Receivers and Drivers                                       | 4-3  |

| 4.2.1.5   | Transmitter Logic                                                  |      |

| 4.2.1.6   | Receiver Logic                                                     | 4-4  |

| 4.2.1.7   | CRC Logic                                                          | 4-5  |

| 4.2.1.8   | Interrupt Control Logic                                            |      |

| 4.2.1.9   | Data Set Interface Logic                                           | 4-6  |

| 4.2.2     | Major Operating Features                                           | 4-7  |

| 4.2.2.1   | Introduction                                                       |      |

| 4.2.2.2   | Modem Control                                                      | 4-7  |

| 4.2.2.3   | Transmitter Section                                                | 4-8  |

| 4.2.2.4   | Receiver Section                                                   |      |

| 4.3       | DETAILED DESCRIPTION                                               | 4-14 |

| 4.3.1     | Introduction                                                       | 4-14 |

| 4.3.2     | Registers                                                          |      |

| 4.3.2.1   | Receiver Control and Status Register (RXCSR)                       |      |

| 4.3.2.2   | Receiver Data Buffer Register (RXDBUF)                             | 4-15 |

| 4.3.2.3   | Parameter Control and Status Register (PARCSR)                     | 4-16 |

| 4.3.2.4   | Transmitter Control and Status Register (TXCSR)                    |      |

| 4.3.2.5   | Transmitter Data Buffer Register (TXDBUF)                          |      |

| 4.3.3     | Device Reset Logic (Logic Sheet BSI1)                              | 4-21 |

| 4.3.4     | Address Selection Logic (Logic Sheet BSI6)                         |      |

| 4.3.4.1   | Address Assignments and Format                                     |      |

| 4.3.4.2   | Address Decoding                                                   |      |

| 4.3.5     | Unibus Receivers and Multiplexed Unibus Drivers (Logic Sheet BSI8) | 4-27 |

| 4.3.6     | Transmitter Logic (Logic Sheet BSI2)                               |      |

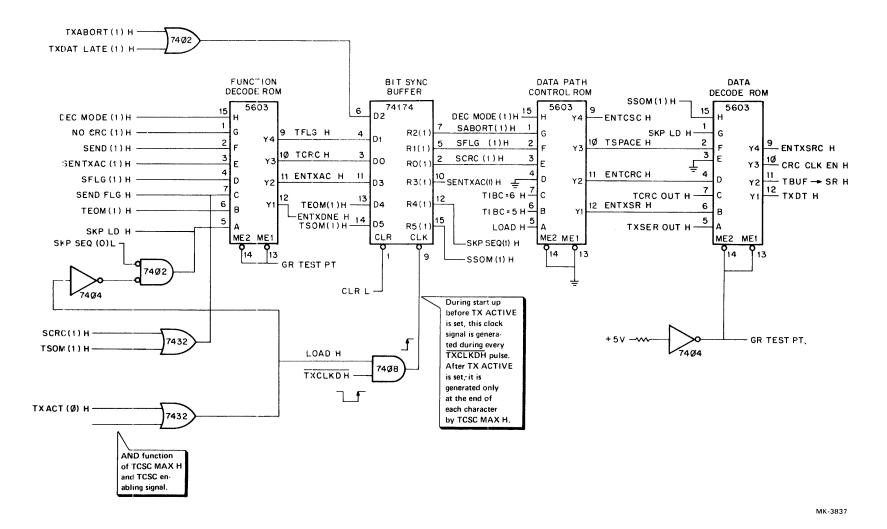

| 4.3.6.1   | ROMs and Bit Sync Buffer                                           | 4-28 |

| 4.3.6.2   | Clock Logic                                                        | 4-32 |

## CONTENTS (Cont)

|           |                                                           | Page         |

|-----------|-----------------------------------------------------------|--------------|

| 4.3.6.3   | TXDAT Flip-Flop and T1BC Counter                          | 1 26         |

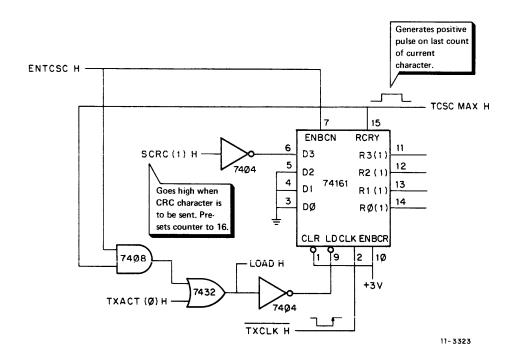

| 4.3.6.4   | Transmitter Character Serialization Counter (TCSC)        |              |

| 4.3.6.5   | Transmitter Character Schanzation Counter (TCSC)          |              |

| 4.3.7     |                                                           |              |

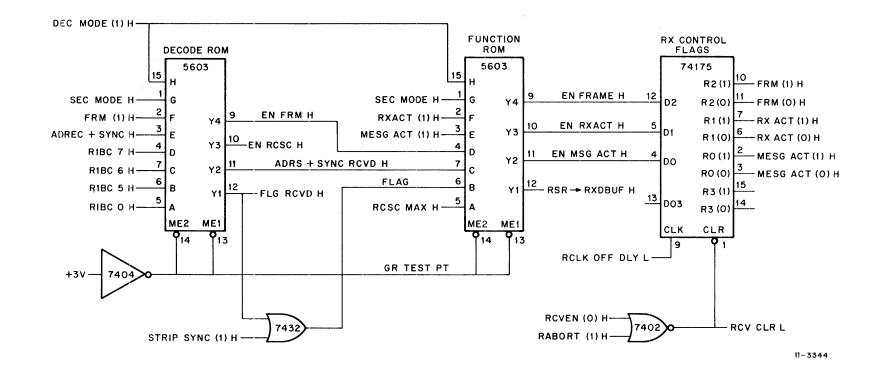

| 4.3.7.1   | Receiver LogicROMs and RX Control Flags                   | 4-42<br>4 42 |

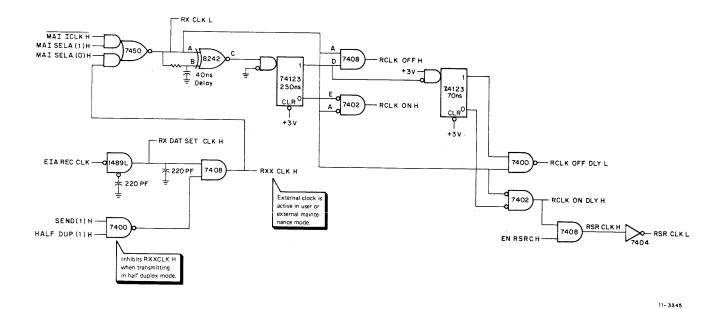

| 4.3.7.2   | Clock Logic                                               |              |

| 4.3.7.3   | EN R1BC Flip-Flop and R1BC Counter                        |              |

| 4.3.7.4   | Character Serialization Counter                           |              |

| 4.3.7.5   | Receiver Shift Register and Data Buffer                   |              |

|           |                                                           |              |

| 4.3.8     | CRC Logic                                                 |              |

| 4.3.8.1   | General                                                   |              |

| 4.3.8.2   | Error Detection Logic                                     |              |

| 4.3.8.3   | Transmitter CRC Register                                  |              |

| 4.3.8.4   | Receiver CRC Register                                     |              |

| 4.3.8.5   | Typical CRC Accumulation                                  |              |

| 4.3.9     | Interrupt Control Logic                                   |              |

| 4.3.9.1   | General                                                   |              |

| 4.3.9.2   |                                                           |              |

| 4.3.9.3   | BR Priority Selector Card                                 |              |

| 4.3.9.4   | Typical Interrupt Transaction                             |              |

| 4.3.9.5   | NPR Latency Improvement Circuit                           |              |

| 4.3.10    | Data Set Interface Logic                                  |              |

| 4.3.10.1  | General                                                   |              |

| 4.3.10.2  | Logic for Signals from Data Set                           |              |

| 4.3.10.3  | Logic for Signals to Data Set                             |              |

| 4.3.10.4  | Logic for Transmitted Data and External Maintenance Clock |              |

| 4.3.11    | Typical Operations                                        |              |

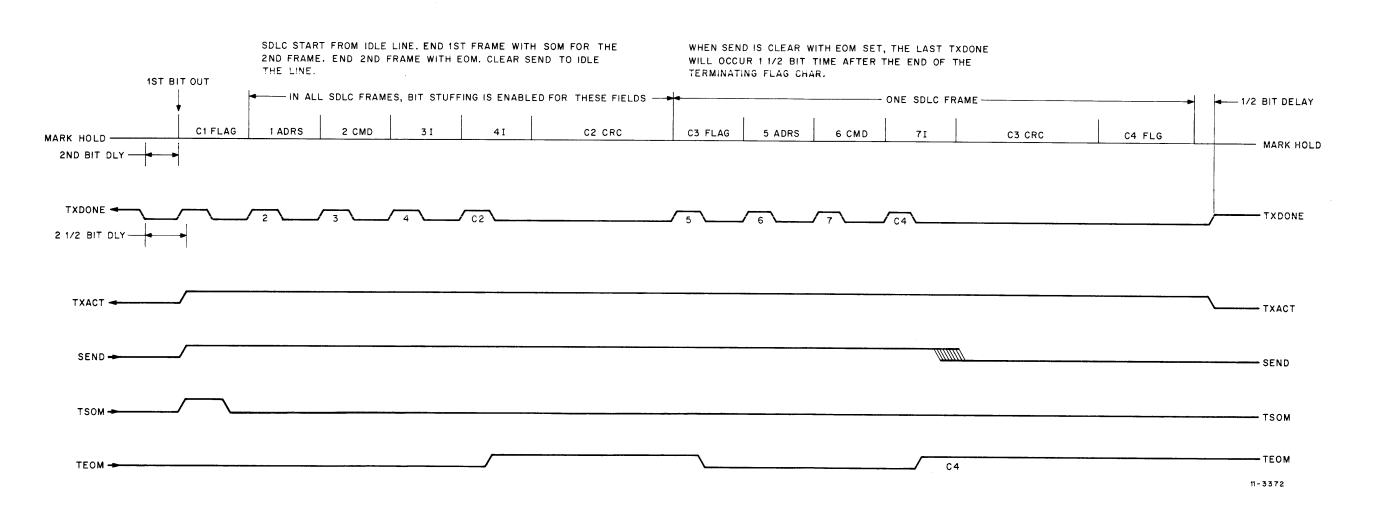

| 4.3.11.1  | Introduction(SDLC)                                        | 4-73<br>175  |

| 4.3.11.2  | Typical Transmit Operation (SDLC)                         | 4-13<br>192  |

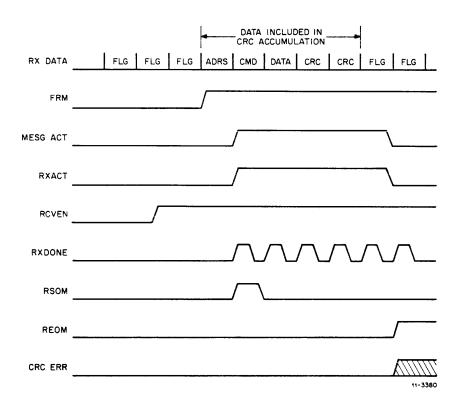

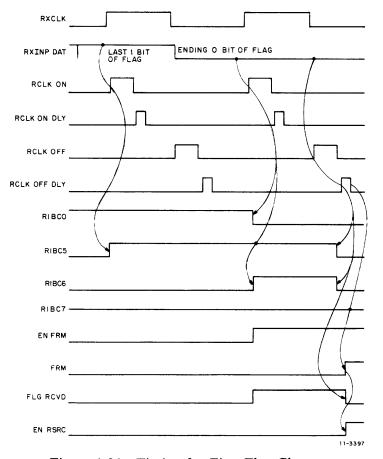

| 4.3.11.3  | Typical Receive Operation (SDLC)                          | 4-80         |

| CHAPTER 5 | MAINTENANCE                                               |              |

| 5.1       | SCOPE                                                     |              |

| 5.2       | MAINTENANCE PHILOSOPHY                                    |              |

| 5.3       | PREVENTIVE MAINTENANCE                                    |              |

| 5.4       | TEST EQUIPMENT REQUIRED                                   |              |

| 5.5       | CORRECTIVE MAINTENANCE                                    |              |

| 5.5.1     | Maintenance Modes                                         |              |

| 5.5.1.1   | Internal Maintenance                                      |              |

| 5.5.1.2   | System Test                                               |              |

| 5.5.1.3   | External Maintenance                                      |              |

| 5.5.2     | Diagnostics                                               | 5-3          |

## **CONTENTS (Cont)**

Page

| APPENDIX A  | PDP-11 MEMORY ORGANIZATION AND ADDRESSING CONVENT                                    | TIONS                    |

|-------------|--------------------------------------------------------------------------------------|--------------------------|

| APPENDIX B  | LOGIC SYMBOLOGY                                                                      |                          |

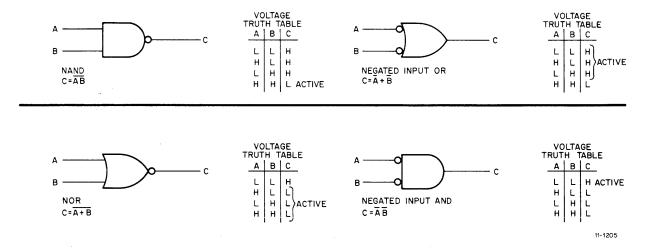

| B.1         | INTRODUCTION                                                                         | B-1                      |

| B.2         | UNIBUS SIGNAL LEVELS                                                                 |                          |

| B.3         | EQUIVALENT GATE SYMBOLS                                                              |                          |

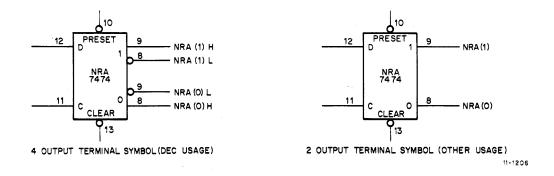

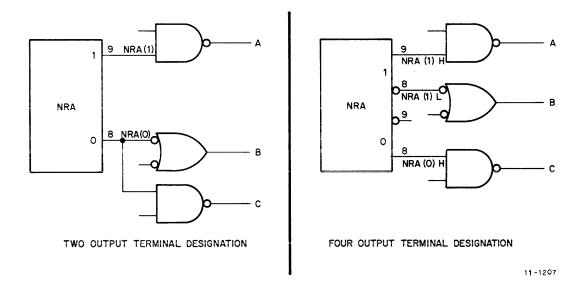

| B.4         | 4-OUTPUT TERMINAL FLIP-FLOP SYMBOLOGY                                                | B-2                      |

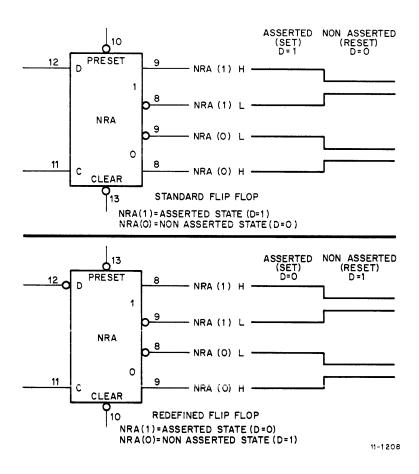

| B.5         | REDEFINED 4-OUTPUT TERMINAL FLIP-FLOPS                                               | B-4                      |

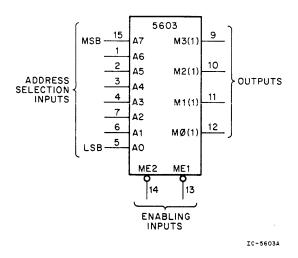

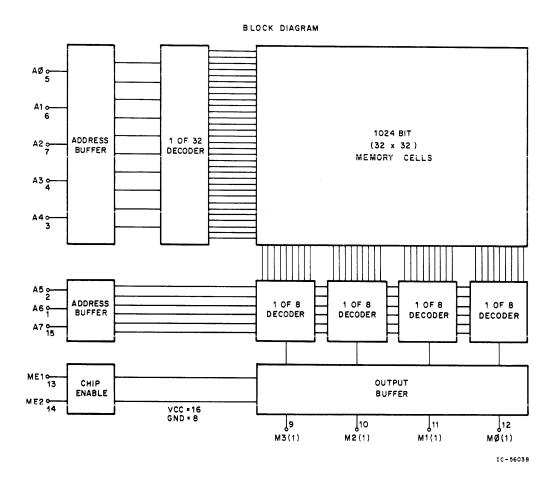

| APPENDIX C  | INTEGRATED CIRCUIT DESCRIPTIONS                                                      |                          |

|             | FIGURES                                                                              |                          |

| Figure No.  | Title                                                                                | Page                     |

| 1-1         | SDLC Message Format                                                                  | 1-3                      |

| 1-2         | DDCMP Data Message Format                                                            | 1-5                      |

| 1-3         | DDCMP Sample Handshaking Procedure                                                   | 1-6                      |

| 2-1         | DUP11 Parts Diagram                                                                  |                          |

| 2-2         | Component Location                                                                   |                          |

| 2-3         | DUP11 Cabling                                                                        | 2-5                      |

| 2-4         | DUP11 (M7867 Module) Mounted in DD11-B                                               |                          |

| 2-5         | H3001 Installation in a Horizontally Oriented I/O Bulkhead                           |                          |

| 2-6         | H3001 Installation in a Vertically Oriented I/O Bulkhead                             | 2-8                      |

| 2-7<br>2-8  | Side Rail Installation of H3001 Distribution Panel  Installation Procedure Flowchart | 2-10                     |

| 2-8<br>2-9  | H3001 Distribution Panel                                                             |                          |

| 3-1         | DUP11 Register Configurations and Bit Assignments                                    |                          |

| 3-2         | Receiver Control and Status Register Format                                          | 2 2                      |

| 3-3         | Receiver Data Buffer Register Format                                                 |                          |

| 3-4         | Parameter Control and Status Register Format                                         | ر-ر<br>11 <sub>-</sub> 2 |

| 3-5         | Transmitter Control and Status Register Format                                       | 3-13                     |

| 3-6         | Transmitter Data Buffer Register Format                                              |                          |

| <b>4-</b> 1 | DUP11 Simplified Block Diagram                                                       |                          |

| 4-2         | PARCSR Bits 7-0                                                                      |                          |

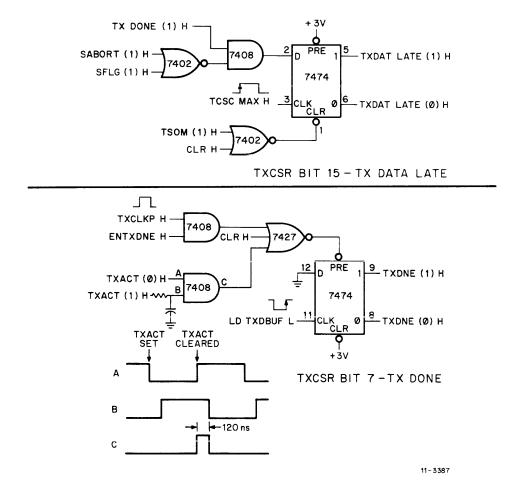

| 4-3         | TXCSR Bits 15 and 7                                                                  |                          |

| 4-4         | TXDBUF Register Bits 12 and 14                                                       |                          |

| 4-5         | Device Reset Logic                                                                   |                          |

| 16          | Address Ward Format                                                                  | 4 22                     |

## FIGURES (Cont)

| Figure No. | Title                                                                     |      |  |  |  |

|------------|---------------------------------------------------------------------------|------|--|--|--|

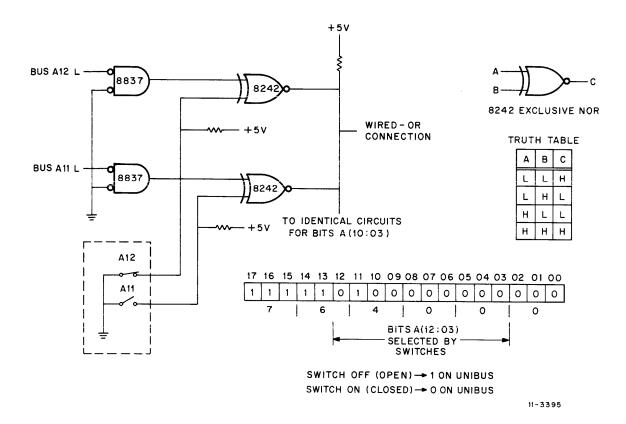

| 4-7        | Typical Operation of an 8242 Comparator                                   | 4-25 |  |  |  |

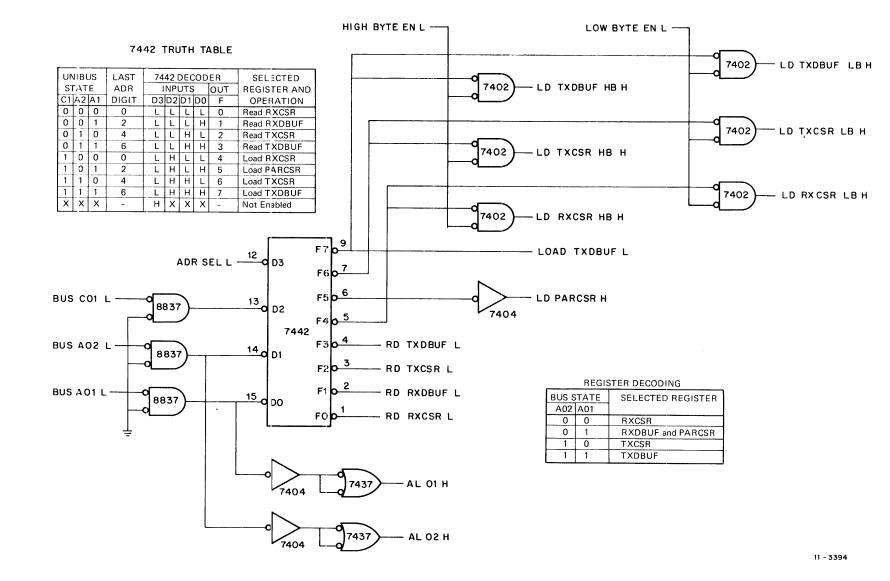

| 4-8        | Register Decoding Logic                                                   |      |  |  |  |

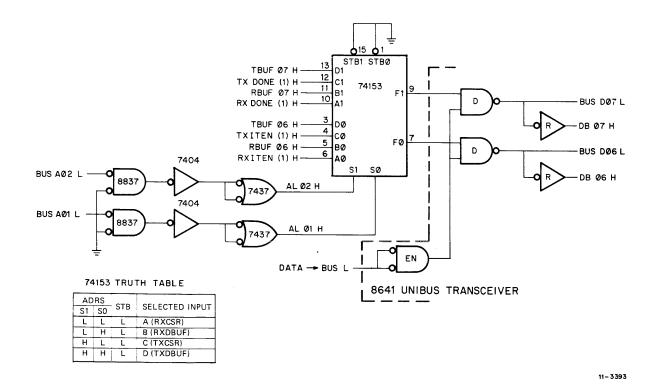

| 4-9        | Typical 2-Bit Slice of Unibus Multiplexer Logic                           |      |  |  |  |

| 4-10       | Transmitter ROMs and Associated Logic                                     |      |  |  |  |

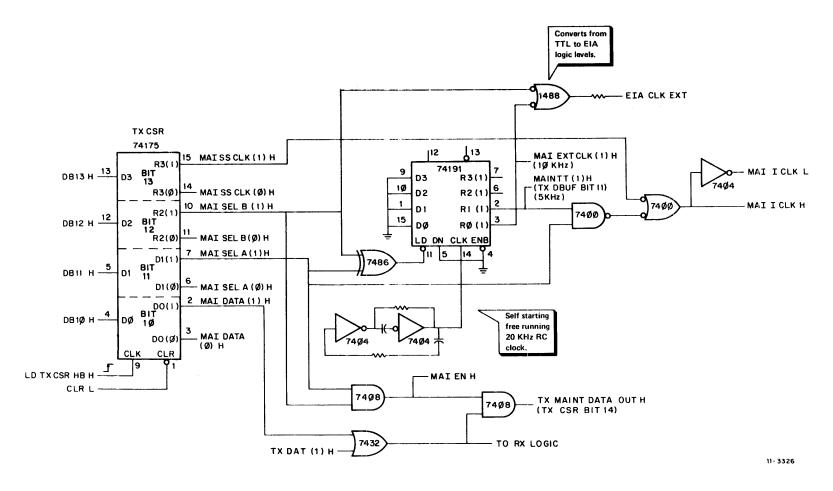

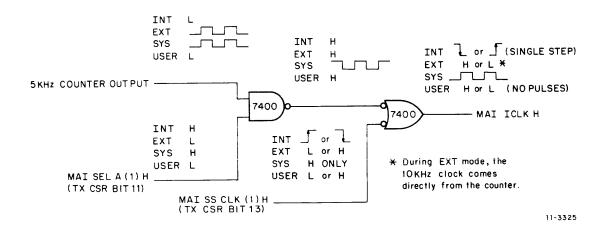

| 4-11       | Internal Clock Logic                                                      | 4-33 |  |  |  |

| 4-12       | Signal States for Maintenance Clock                                       |      |  |  |  |

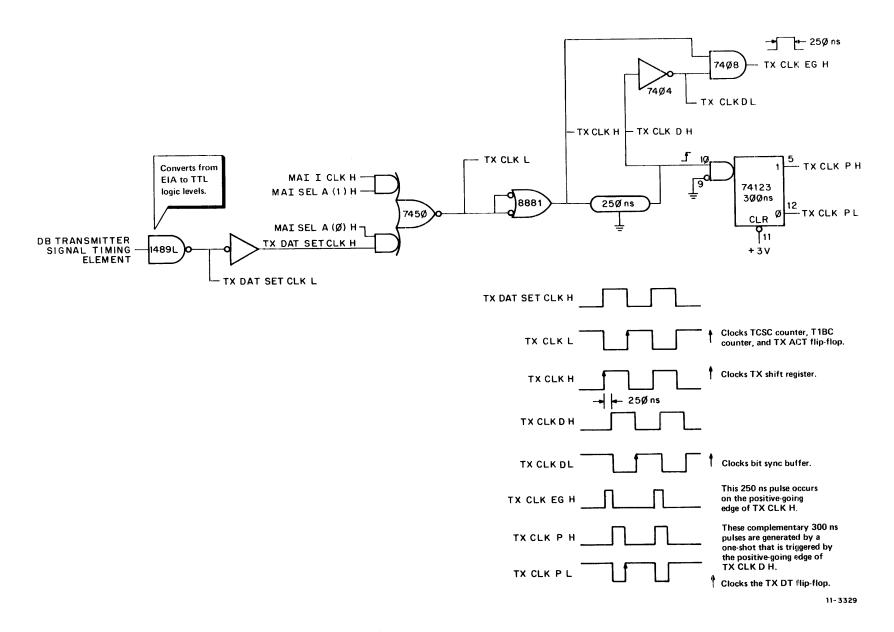

| 4-13       | Transmitter Clock Logic and Timing Diagram                                | 4-37 |  |  |  |

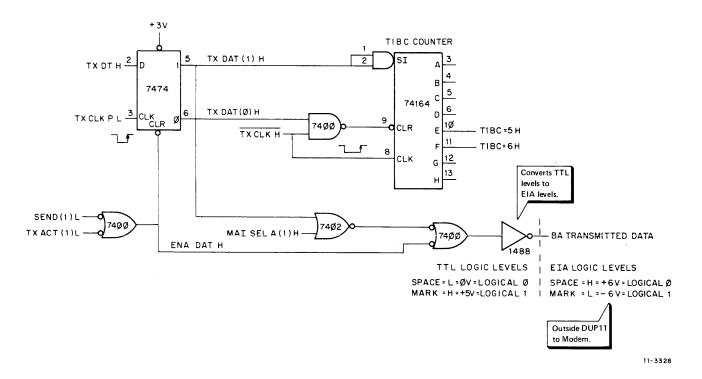

| 4-14       | TXDAT Flip-Flop and T1BC Counter                                          | 4-38 |  |  |  |

| 4-15       | TCSC Counter                                                              |      |  |  |  |

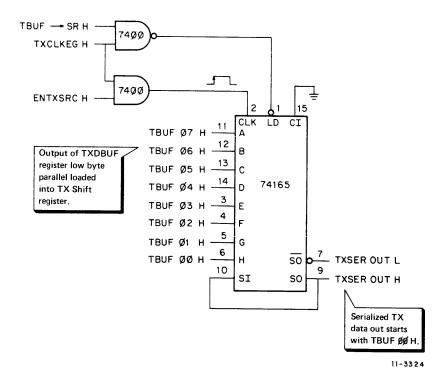

| 4-16       | Transmitter Shift Register                                                | 4-42 |  |  |  |

| 4-17       | Receiver ROMs and Associated Logic                                        | 4-44 |  |  |  |

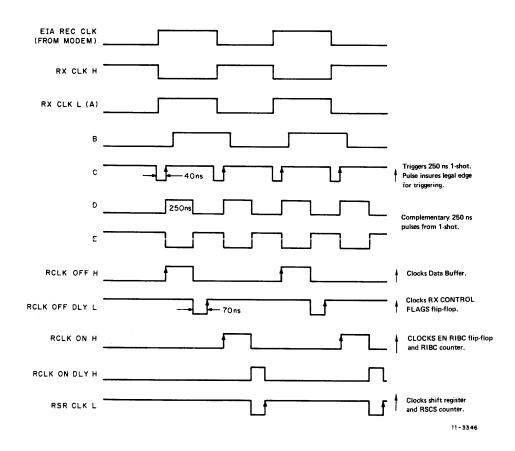

| 4-18       | Receiver Clock Logic and Timing Diagram                                   | 4-46 |  |  |  |

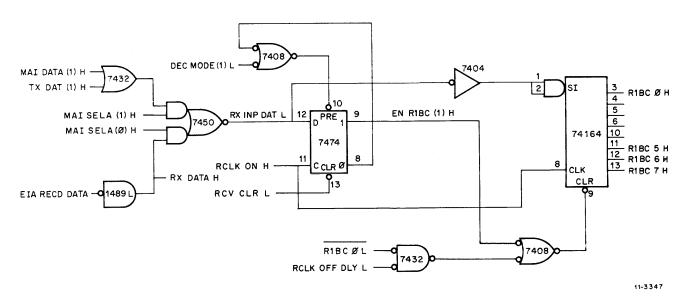

| 4-19       | EN R1BC Flip-Flop and R1BC Counter                                        | 4-47 |  |  |  |

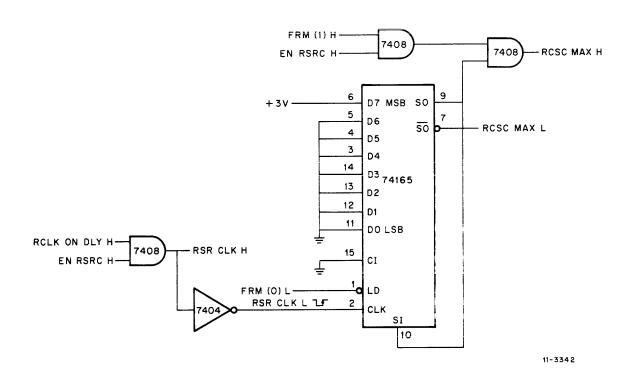

| 4-20       | Received Character Serialization Counter                                  | 4-49 |  |  |  |

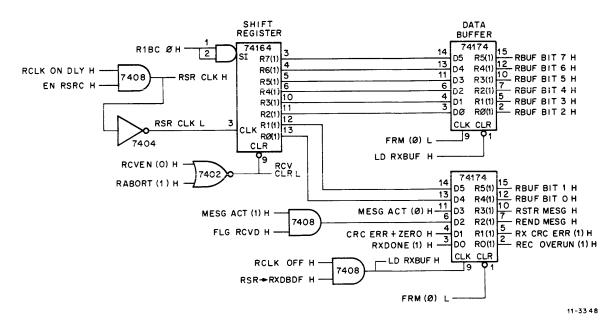

| 4-21       | Receiver Shift Register and Data Buffer                                   | 4-51 |  |  |  |

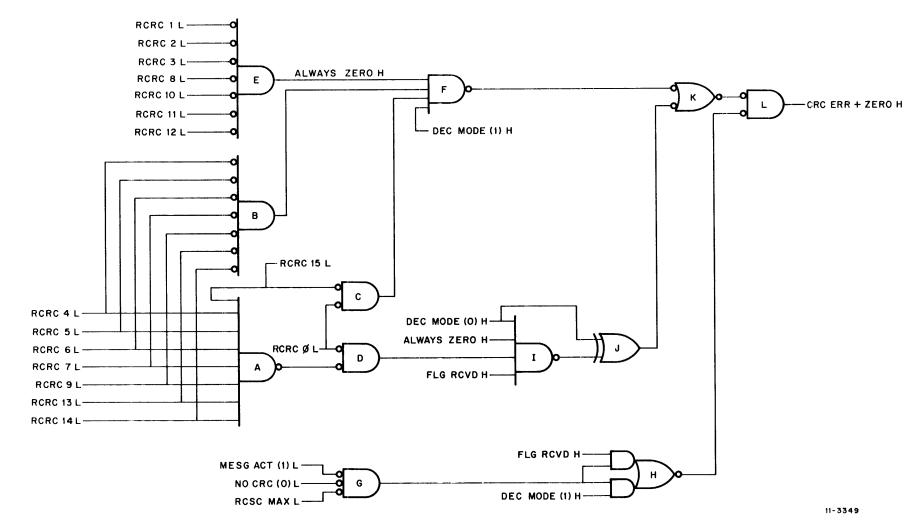

| 4-22       | CRC Error Detection Logic                                                 | 4-53 |  |  |  |

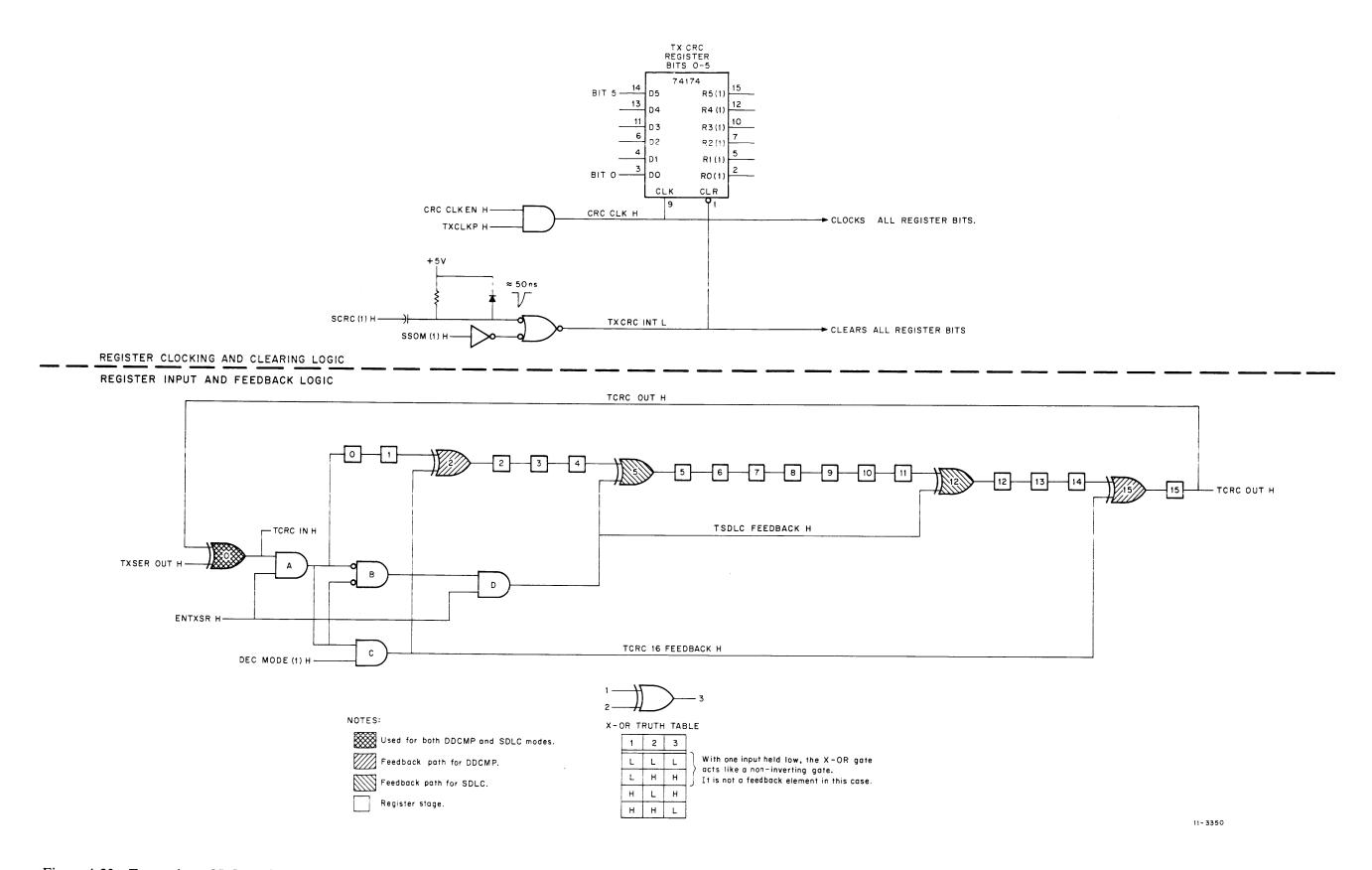

| 4-23       | Transmitter CRC Register                                                  | 4-56 |  |  |  |

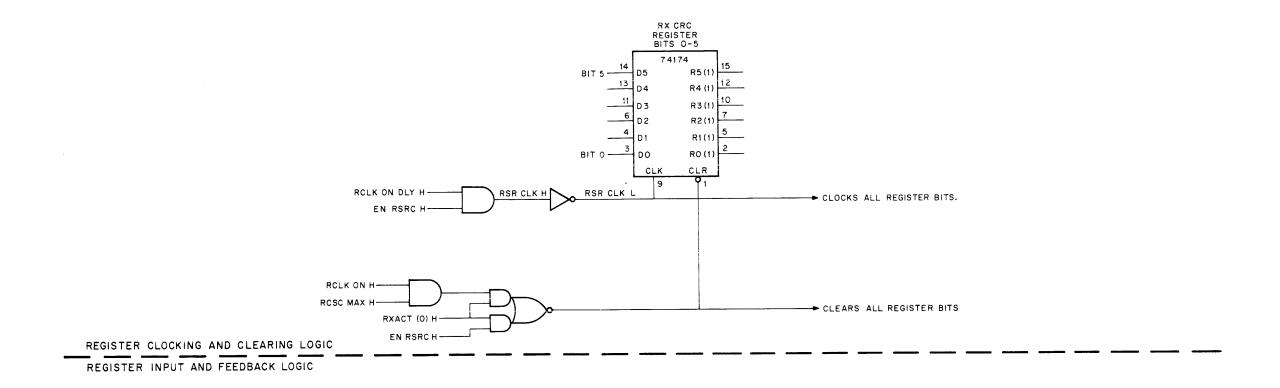

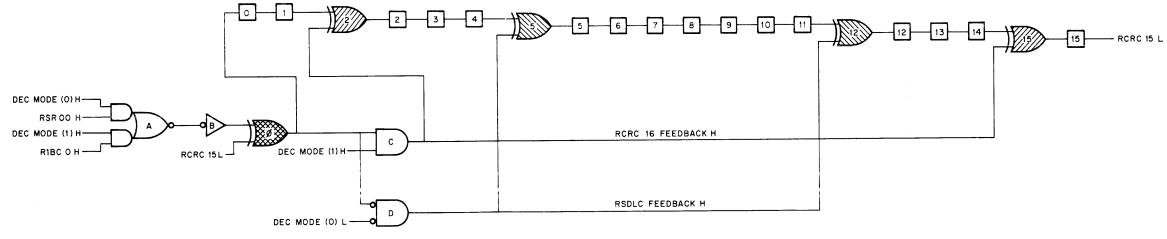

| 4-24       | Receive CRC Register                                                      | 4-59 |  |  |  |

| 4-25       | Typical Transmit and Receive CRC Accumulation                             |      |  |  |  |

| 4-26       | Selecting State of Vector Address Bits                                    | 4-63 |  |  |  |

| 4-27       | Selecting Vector Addresses                                                | 4-64 |  |  |  |

| 4-28       | Configuration of the BR4 Priority Card                                    | 4-65 |  |  |  |

| 4-29       | REQ A, REQ B and V2 Flip-Flops and Associated Interrupt Control Logic     | 4-69 |  |  |  |

| 4-30       | Pulse Generator for SEC RCV, DSR, CARRIER and CLR TO SD Lines             | 4-73 |  |  |  |

| 4-31       | Pulse Generator for RING Line                                             | 4-74 |  |  |  |

| 4-32       | Typical SDLC Transmit Operation                                           | 4-76 |  |  |  |

| 4-33       | Typical SDLC Receive Operation                                            |      |  |  |  |

| 4-34       | Timing for First Flag Character                                           | 4-87 |  |  |  |

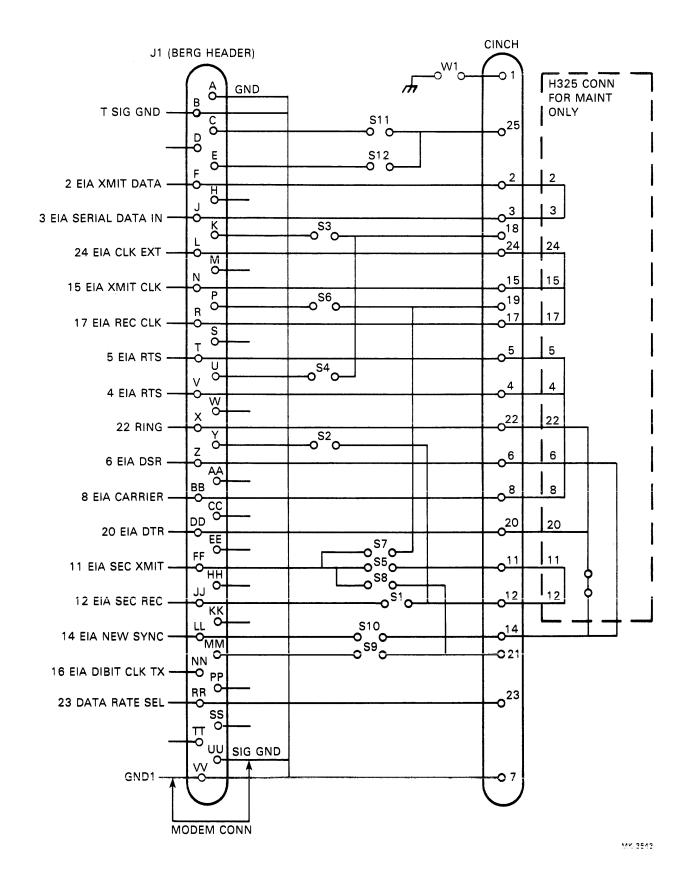

| 5-1        | Schematic of H3001 Distribution Panel with H325 Test Connector            |      |  |  |  |

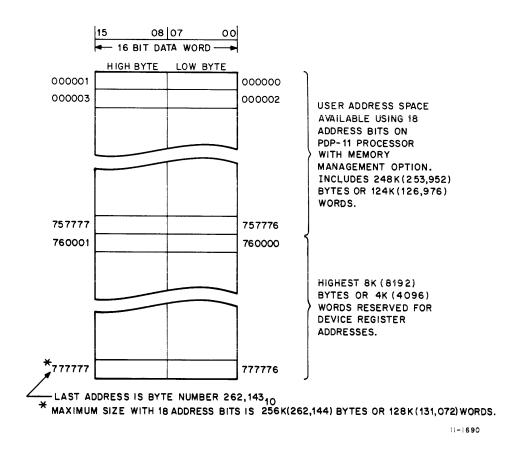

| A-1        | Memory Organization for Maximum Size Using 18 Address Bits                | A-2  |  |  |  |

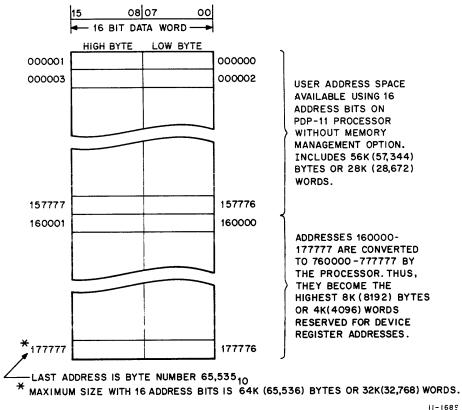

| A-2        | Memory Organization for Maximum Size Using 16 Address Bits                |      |  |  |  |

| B-1        | Logically Equivalent Gates                                                | B-2  |  |  |  |

| B-2        | Flip-Flop Logic Symbology                                                 |      |  |  |  |

| B-3        | Electrical Connections to Outputs of 2-Terminal and 4-Terminal Flip-Flops |      |  |  |  |

| B-4        | Standard and Redefined 4-Terminal Flip-Flops                              | B-4  |  |  |  |

## **TABLES**

| Table No. | Title                                                                |      |  |

|-----------|----------------------------------------------------------------------|------|--|

| 2-1       | M7867 Jumper Configuration                                           | 2-3  |  |

| 2-2       | H3001 Switch Settings                                                | 2-11 |  |

| 2-3       | Guide for Setting Switches to Select Device Address                  | 2-21 |  |

| 2-4       | Guide for Setting Switches to Select Vector Address                  |      |  |

| 3-1       | DUP11 Registers                                                      |      |  |

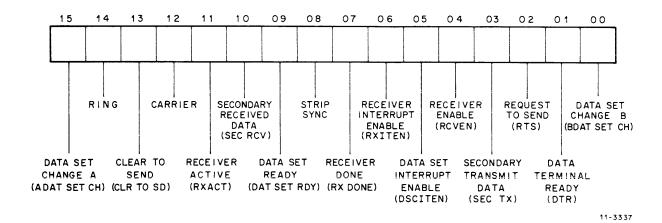

| 3-2       | Bit Descriptions for Receiver Control and Status Register (RXCSR)    |      |  |

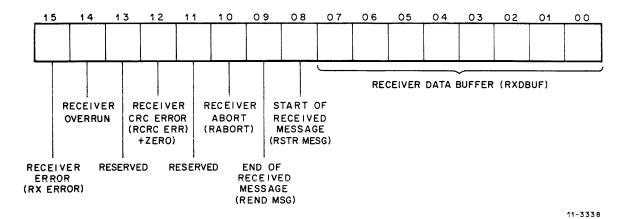

| 3-3       | Bit Descriptions for Receiver Data Buffer Register (RXDBUF)          |      |  |

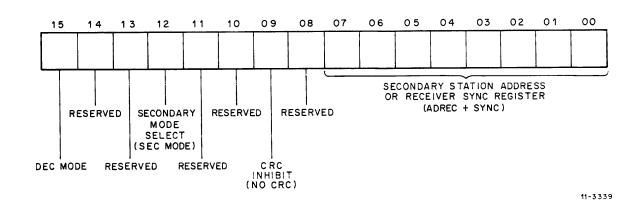

| 3-4       | Bit Descriptions for Parameter Control and Status Register (PARCSR)  |      |  |

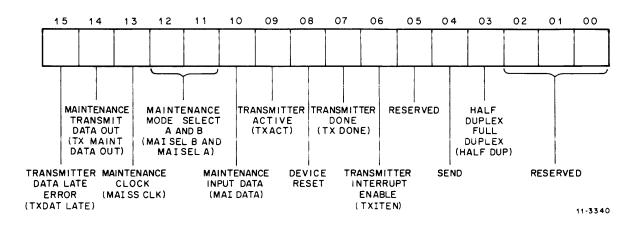

| 3-5       | Bit Descriptions for Transmitter Control and Status Register (TXCSR) |      |  |

| 3-6       | Bit Descriptions for Transmitter Data Buffer Register (TXDBUF)       |      |  |

| 4-1       | Unibus Transactions for DUP11                                        | 4-23 |  |

| 4-2       | Clock Signal Selection for Maintenance Modes                         | 4-34 |  |

| 5-1       | Test Equipment Required                                              | 5-2  |  |

| C-1       | Integrated Circuits                                                  |      |  |

#### CHAPTER 1 INTRODUCTION

#### 1.1 SCOPE

This manual provides the user with the information necessary to install, operate and maintain the DUP11 Synchronous Line Interface. The manual is organized into five chapters and three appendices:

Chapter 1 – Introduction

Chapter 2 - Installation

Chapter 3 - Register Description

Chapter 4 – Theory of Operation

Chapter 5 - Maintenance

Appendix A - PDP-11 Memory Organization and Addressing Conventions

Appendix B - Logic Symbology

Appendix C - Integrated Circuit Descriptions

This chapter provides a general description of the DUP11 and a general discussion of the Synchronous Data Link Control (SDLC) protocol and Digital Data Communications Message Protocol (DDCMP). Some background material on Cyclic Redundancy Checking (CRC) methods is provided also.

#### 1.2 DUP11 GENERAL DESCRIPTION

The DUP11 provides a data path between a synchronous modem and the Unibus. It operates under the discipline of SDLC, ADCCP, DDCMP, and other similar protocols. Protocols of the BISYNC family can be used with some loss of efficiency due to the additional software decisions required.

The DUP11 provides parallel-to-serial conversion of data to be transmitted and serial-to-parallel conversion of received data. Logic is provided to create a transparent data stream and to compute a CRC check character during transmission. All information is handled in 8-bit bytes and VRC parity is not provided. CRC error detection is provided during reception. Modem control and level conversion logic is provided also.

Interrupt control logic is used to generate requests for the transfer of data between the DUP11 and the PDP-11 system memory via the Unibus. No direct memory access (DMA) logic is contained in the DUP11.

The DUP11 contains logic to perform the following functions:

- 1. Program control of secondary station address recognition. Primary station operation is used as the default condition (SDLC protocol family only).

- 2. Programmable SYN character recognition (DDCMP and BISYNC protocol families).

- 3. CRC characters computation and error detection (SDLC and DDCMP protocol families).

- 4. Automatic transmission of flag characters initiated by the program (SDLC protocol family only).

- 5. Program control of transmission of abort sequence and 16 zero sequence (SDLC protocol family only).

- 6. Hardware detection of received flags and abort sequences (SDLC protocol family only).

The DUP11, including level conversion, is contained on a hex module. The DUP11 is connected to the modem via a BC05C cable and BC02 cable that support RS232-C specifications only. Current mode operation is not supported by the DUP11 and it is not compatible with the DF11 series options.

The modem control logic is compatible with Bell 201, 208, and 209 series modems. There is no interlock between the transfer of data and modem control. The program controls handshaking with the modem, if it is required. Once the handshaking has been completed, the program can initiate the transfer of data. The modem control logic includes secondary receive and transmit leads. These leads can be redefined by the Field Service engineer at the user's request.

#### 1.3 SDLC AND DDCMP PROTOCOLS

#### 1.3.1 Introduction

This discussion provides a general description of the SDLC and DDCMP protocols. It is the prerequisite to a thorough understanding of the operation of the DUP11. Details of the SDLC, DDCMP, ADCCP and BISYNC protocols are found in the following documents:

Digital Data Communications Message Protocol (Digital Equipment 130-959-007-02) IBM Binary Synchronous Communications General Information (GA27-3004-2) ADCCP ANSI X3S34/475 DR7 ADCCP ANSI X3S34/584 DR1

#### 1.3.2 General Information

Although the mentioned protocols are not identical, they are similar enough to operate with the DUP11. The program directly controls the DUP11 operation through the use of control and status registers. The program must provide a continuous flow of data to be transmitted. No intra-message fill characters are allowed. The program must also service the receiver data buffer within the prescribed time.

When transmitting in the SDLC or DDCMP family of protocols, the program must form the address and command fields plus any other header information that is required. The program must maintain the transmitter data buffer and set marker bits to delimit the transmitted message. When receiving in the SDLC or DDCMP family of protocols, the program must interpret the header information, service the receiver data buffer, and monitor the status bits associated with the received data.

Protocols such as BISYNC that achieve transparency by using special control characters are less efficient than SDLC and DDCMP when used with the DUP11. This occurs because of the increased program involvement required to maintain transparency and compute the CRC character. The CRC control logic in the DUP11 is not suited to protocols in which special control characters appear within the body of the message. For these protocols, the CRC logic should be disabled by setting the NO CRC bit (PARCSR bit 9).

#### 1.3.3 SDLC Protocol Description

1.3.3.1 Message Format – The SDLC message format is shown in Figure 1-1. This format is called a frame and is the standard structure for all transmissions.

| FLAG     | ADDRESS | CONTROL | INFORMATION     | FRAME CHECK SEQUENCE | FLAG     |

|----------|---------|---------|-----------------|----------------------|----------|

| 01111110 | 8 BITS  | 8 BITS  | VARIABLE LENGTH | 16 BITS              | 01111110 |

11-3430

Figure 1-1 SDLC Message Format

The frame starts with the 8-bit Flag sequence, 01111110, followed in order by the Address sequence, Control sequence, Information sequence (if present), Frame Check sequence, and ends with another Flag sequence. In some applications, the Flag is preceded by a sequence of 16 zeros.

Each sequence in the frame is discussed below with emphasis on related operational features of the DUP11, if applicable.

#### Flag Character

The flag character is a unique 8-bit character of the form 01111110. Flag characters are used to delimit the message. They can be used to fill in between messages but cannot be used as fillers within messages. When the transmitter initiates the start of a message by asserting the TSOM (transmitter start of message) bit, the initial flag character is automatically transmitted. If the TSOM bit is still asserted at the end of the first flag character, another flag character is transmitted. When the TXDONE (transmitter done bit) is asserted by the DUP11 subsequent to the program's asserting of the TSOM bit, the program may respond by loading data into the TXDBUF (transmitter data buffer) low byte, or leave the TSOM bit asserted and send another flag.

In some applications, the TSOM and TEOM bits are used to initiate a sequence of 16 zeros. This sequence can be initiated only from the idle state. To transmit this sequence, SEND must be asserted and TXACT must be cleared. With these requirements met, the program simultaneously sets TSOM and TEOM and the 16 zeros are transmitted. When the first zero bit is presented to the serial output, TXDONE is set. Now, the program should clear TEOM and on the next transition of TXDONE the program should clear TSOM. The first data character can be loaded now. This point marks the start of the initial flag character, the first data character is transmitted subsequent to the current flag character.

When the last character of a message has been loaded into the TXDBUF, that character is then transmitted. Subsequent to loading the last character, the TXDONE bit is asserted again by the DUP11. This marks the start of the transmission of the last character. At this time, the TEOM (transmitter end of message) may be asserted in the upper byte of the TXDBUF. The character currently being serialized (i.e., the last character of the message) is transmitted and followed by a CRC check character and the terminating flag character. This concludes the message.

When the receiver logic is enabled by the software, it searches for flag characters. If the basic SDLC or ADCCP message format is followed and the receiver is programmed to operate in the secondary mode, the following actions occur.

The eight bits after the last received flag are compared to the secondary station address. If a match is not found, the receiver continues to hunt for a flag. When the next flag character is located, this comparison of addresses is reiterated.

If the character subsequent to the flag character matches the secondary station address, characters received subsequent to the address character cause the RXDONE (receiver done) bit to be asserted. The RSOM (receiver start of message) bit is presented to the program along with the first data character.

When the secondary station receiver is actively transferring data, the following events occur when a terminating flag character is detected. The receiver logic automatically resumes the address search as cited earlier. Also, a status entry is made into the receiver data buffer, the REOM bit is asserted and the CRC error bit is set if an error was detected. The lower byte of data in this entry is invalid.

When the receiver logic is programmed to operate as a primary station, all characters subsequent to the last received flag character cause the RXDONE bit to be asserted. The first character of the frame is accompanied by the RSOM bit.

When the terminating flag character of a message is received, primary station operation is the same as cited above for secondary station operation. When the next data character is received, the receiver logic again sets the RSOM and RXDONE bits. The last two bytes preceding the flag were the receiver CRC bytes.

#### **Address Character**

The address character appears subsequent to the flag character and is eight bits long. This format supports a maximum of 256 addresses. The protocol has provisions for the recursive expansion of the number of addresses. This feature is not supported by the DUP11 hardware. It must be maintained by the program. In the secondary station mode, the program must load the address of the receiving station into the low byte of the PARCSR.

#### Control Field

The 8-bit control field follows the address character. This field is controlled by the program and is encoded to indicate the commands and responses to control the data link. This field has three formats as described below.

- 1. Nonsequenced Format used by the primary station primarily for data link management. Such duties include activating and initializing secondary stations, controlling the response mode of secondary stations, and reporting procedural errors.

- 2. Supervisory Format does not contain an information field but it is an adjunct to the information format. It is used by the primary station to poll the secondary stations. The secondary stations use this format to provide acknowledgment to the primary station.

- 3. Information Format used by primary and secondary stations for the transfer of information fields.

#### Information Field

This field is used for the transmission of data or status information. This field contains an arbitrary number of characters as specified by the documents covering the protocols. The DUP11 handles the data in this field as eight bit characters.

When one character is transmitted from the transmitter shift register, another character is taken from the data buffer. If the data buffer is empty, the transmitted data lead goes to a mark hold state. Also, a status bit is asserted to indicate the data underrun condition in SDLC or ADCCP and an Abort character is automatically transmitted.

There are no restrictions on bit patterns that appear between flags in an SDLC frame. Therefore, the transmitted data may contain six or more contiguous 1s and this pattern could be interpreted as a flag which would inadvertently terminate an incomplete frame. To prevent this action and to maintain data

transparency, the DUP11 contains 0 insertion and 0 removal logic that is active on all characters between the flags. During transmission, when five contiguous 1s occur, the transmitter automatically inserts a 0 after the fifth 1. During reception, the 0 after five contiguous 1s is automatically removed. This applies to all fields except the Flag.

#### Frame Check Sequence (FCS) Field

This 16-bit field follows the information field and is also referred to as the Block Check Character (BCC) or CRC check character. It is used in all SDLC frames to detect errors.

Logic to compute CRC check characters is included in the transmitter logic. Similarly, logic is included in the receiver logic to check the results when the check character is received. This operation of computing and verifying the CRC check is transparent to the program. Any error in the computation of the received check character in SDLC type protocol operation is indicated by a status bit in the receiver data buffer. If DDCMP operation is selected, the program must monitor a status bit to detect the desired accumulated results.

Two CRC polynomials are supported by the DUP11: CRC 16 and CCITT. When the SDLC or ADCCP mode of operation is selected, the CCITT polynomial is used and the internal CRC registers are effectively initialized to all 1s. During transmission, the complement of the accumulated CRC character is sent. If the SDLC or ADCCP mode is not selected, the CRC 16 polynomial is used providing CRC checking is not inhibited.

1.3.3.2 Abort Sequence – An abort is the premature termination of a data line by the transmitting station. An abort is detected by the reception of more than seven contiguous 1s. When the abort sequence is received, the message in progress is terminated. A flag (RXERROR) is set and RXDONE is set also. If the program has set RXITEN, an a interrupt request is generated when RXDONE is set. A transmitting station can send abort sequences under program control by setting the TXABORT bit. If the program response time to the TXDONE bit is excessive, the TXDATLAT bit is set and the transmitter idles abort characters.

#### 1.3.4 DDCMP Protocol

DDCMP (Digital Data Communications Message Protocol) was developed to provide full-duplex message transfer over standard existing hardware.

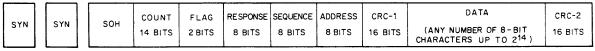

1.3.4.1 Controlling Data Transfers – The DDCMP message format is shown in Figure 1-2. A single control character is used in a DDCMP message, and is the first character in the message. Three control characters are provided in DDCMP to differentiate between the three possible types of messages:

SOH - data message follows

ENQ - control message follows

DLE - bootstrap message follows.

Note that the use of a fixed-length header and message-size declaration obviates the BSC requirement for extensive message and header delimiter codes.

Figure 1-3 shows a simple example of data exchange between the DUP11/PDP-11 and a data terminal. More efficient procedures can be derived after a study of DDCMP.

11-2897

Figure 1-2 DDCMP Data Message Format

DUP11/PDP-11 **TERMINAL** Sends a STRT (START) message which means: "I want to begin sending data to you and the sequence number of my first message will be 1."\_ Receives STRT message. Sends a STACK (Start Acknowledge) message which means: "OK with me; here is the first sequence number (5) I will use in sending data messages to you." Receives STACK Sends Data Messages with a response field set to 4 and the sequence field set to 1, which means: "I am looking for your message 1." Other messages may be sent at this time (i.e., messages 2, 3, etc.) without waiting for a response. Receives Data Message 1 and checks it for sequence and CRC errors. If there is a sequence error, go to 12. If there is no error, go to 9. A CRC error was detected. Computer B sends a NAK message with the response field set to 0, which means: "All messages up to 0 (Modulo 256) have been accepted and message 1 is in error." Computer A receives NAK, retransmits Message 1 and any other messages sent since (i.e., 2, 3, etc.) if already sent. Sends ACK response of 1 either in a separate ACK message or in the response field of a data message. Receives ACK and releases Message 1 Continues sending messages. Discard message and wait for proper Message 2. Times out because of lack of response for Message 2. Sends a reply for Message 2. Send NACK response of 1 in the response field. Retransmits Message 2 and

Figure 1-3 DDCMP Sample Handshaking Procedure

following messages.

1.3.4.2 Error Checking and Recovery - DDCMP uses CRC-16 for detecting transmission errors. When an error occurs, DDCMP sends a separate NAK message. DDCMP does not require an acknowledgment message for all data messages. The number in the response field of a normal header, or in either the special NAK or ACK message, specifies the sequence number of the last good message received. For example, if messages 4, 5, and 6 have been received since the last time an acknowledgment was sent and message 6 is bad, the NAK message specifies number 5 which says "messages 4 and 5 are good and 6 is bad." When DDCMP operates in full-duplex mode, the line does not have to be turned around - the NAK is simply added to the sequence of messages for the transmitter.

When a sequence error occurs in DDCMP, the receiving station does not respond to the message. The transmitting station detects from the response field of the messages it receives (or via time-out) that the receiving station is still looking for a certain message and sends it again. For example, if the next message the receiver expects to receive is 5, but 6 is received, the receiver will not change the response field of its data messages, which contains 4. This says: "I accept all messages up through message 4 and I'm still looking for message 5."

- 1.3.4.3 Character Coding DDCMP uses ASCII control characters for SYN, SOH, ENQ and DLE. The remainder of the message, including the header, is transparent.

- 1.3.4.4 Data Transparency DDCMP defines transparency by use of a count field in the header. The header is of fixed length. The count in the header determines the length of the transparent information field, which can be 0 to 16,383 bytes long. To validate the header and count field, it is followed by a 16-bit CRC-16 field; all header characters are included in the CRC calculation. Once validated, the count is used to receive the data and to locate the second CRC-16 which is calculated on the datafield. Thus, character stuffing is avoided.

- 1.3.4.5 Data Channel Utilization DDCMP uses either full- or half-duplex circuits at optimum efficiency. In the full-duplex mode, DDCMP operates as two dependent one-way channels, each containing its own data stream. The acknowledgments are the only dependency which must be sent in the data stream in the opposite direction.

Separate ACK messages are unnecessary and reduce control overhead. Acknowledgments are simply placed in the response field of the next message for the opposite direction. If several messages are received correctly before the terminal is able to send a message, all of them can be acknowledged by one response. Only when a transmission error occurs, or when traffic in the opposite direction is light (no data message to send) is it necessary to send a special NAK or ACK message, respectively.

In summary, DDCMP data channel utilization features include:

- 1. Low control character overhead

- 2. No "character stuffing"

- 3. No separate ACKs when traffic is heavy saving on extra SYN characters and inter-message gaps

- 4. Multiple acknowledgments (up to 255) with one ACK

- 5. The ability to support point-to-point and multipoint lines.

- 1.3.4.6 Synchronization DDCMP achieves synchronization through the use of two ASCII SYN characters preceding the SOH, ENQ, or DLE. It is not necessary to synchronize between messages as long as no gap exists. Gaps are filled with SYN characters. Two sync characters are required but more are usually transmitted. If synchronization between messages is deliberately lost by sending PAD (all 1s) characters, the inter-message interval must be at least 14 character times in length.

- 1.3.4.7 Bootstrapping DDCMP has a bootstrap message as part of the protocol. It begins with the ASCII control character DLE. The information field contains the system reload programs and is totally transparent.

#### 1.4 BASICS OF CYCLIC REDUNDANCY CHECKING

#### 1.4.1 Mathematical Background

A cyclic code message consists of a specific number of data bits and a Block Check Character (BCC) that is computed by the CRC logic. Let n equal the total number of bits in the message and k equal the number of data bits; then n-k equals the number of bits in the BCC.

The code message is derived from two polynomials which are algebraic representations of two binary words: the generator polynomial P(X) and the message polynomial G(X). The generator polynomial is the type of code used (CRC-12, CRC-16, CRC-CCITT etc.); the message polynomial is the string of serial data bits. The polynomials are usually represented algebraically by a string of terms in powers of X, such as  $X^n \dots + X^3 + X^2 + X + X^0$  (or 1). In binary form, a 1 is placed in each position that contains a term; absence of a term is indicated by a 0. The convention followed in this manual is to place the least significant bit ( $X^0$ ) at the right. For example, if a polynomial is given as  $X^4 + X + 1$ , its binary representation is 10011 (third and second degree terms are not present).

Given a message polynomial G(X) and a generator polynomial P(X), the objective is to construct a code message polynomial F(X) that is evenly divisible by P(X). It is accomplished as follows:

- 1. Multiply the message G(X) by  $X^{n-k}$  where n-k is the number of bits in the BCC.

- 2. The resulting product  $X^{n-k}$  [G(X)] is divided by the generator polynomial P(X).

- 3. The quotient is disregarded and the remainder C(X) is added to the product to yield the code message polynomial F(X), which is represented as  $X^{n-k}[G(X)] + C(X)$ .

The division is performed in binary without carries or borrows. In this case, the remainder is always one bit less than the divisor. The remainder is the BCC and the divisor is the generator polynomial; therefore, the bit length of the BCC is always one less than the number of bits in the generator polynomial.

A simple example is explained below.

1. Given:

Message polynomial

$$G(X) = 110011 (X^5 + X^4 + X + X^0)$$

Generator polynomial  $P(X) = 11001 (X^4 + X^3 + 1)$

$G(X)$  contains 6 data bits

$P(X)$  contains 5 bits and will yield a BCC with 4 bits; therefore, n-k = 4.

2. Multiplying the message G(X) by  $X^{n-k}$  gives:

$$X^{n-k}[G(X)] = X^4(X^5 + X^4 + X + X^0) = X^9 + X^8 + X^5 + X^4$$

The binary equivalent of this product contains 10 bits and is 1100110000.

3. This product is divided by P(X)

4. The remainder C(X) is added to  $X^{n-k}[G(X)]$  to give F(X) = 1100111001.

The code message polynomial is transmitted. The receiving station divides it by the same generator polynomial. If there is no error, the division will produce no remainder and it is assumed that the message is correct. A remainder indicates an error. The division is shown below.

P(X) → 11001

$$100001$$

← F(X)

$11001$   $1001$   $1001$   $1001$   $1001$   $1001$   $1000$  ← no remainder

#### 1.4.2 Hardware Implementation of CRC

The BCC is computed and accumulated in a shift register during transmission. Another shift register is used during reception to examine the received data and BCC. In each register, the number of stages is equal to the degree of the generating polynomial. In the DUP11, the registers have 16 stages because 16-degree generating polynomials are used. SDLC uses code CRC-CCITT whose generator polynomial is  $X^{16} + X^{12} + X^5 + 1$ . DDCMP uses code CRC-16 whose generator polynomial is  $X^{16} + X^{15} + X^2 + 1$ . Both the transmitter and receiver CRC registers have control logic that allows the registers to be configured for the selected CRC code.

When a message and accompanying BCC character have been received, the CRC logic only indicates whether the message is in error or not. It does not correct errors nor does it even enumerate or locate errors. Under protocol discipline, the sending station is requested to re-transmit the message.

#### 1.4.3 CRC Operation in DDCMP Protocol

Under DDCMP protocol control, CRC operation is exactly like that described in Paragraph 1.4.1, Mathematical Background.

The transmitter and receiver CRC registers are initialized to all 0s. At the sending station, the transmitter CRC register processes the information being transmitted and accumulates the BCC. When the last bit of information has been transmitted, the contents of the transmitter CRC register are transmitted.

At the receiving station, the information plus the 16-bit BCC is examined by the receiver CRC register. At the end of the message (information plus BCC), the contents of the receiver CRC register should read 0 if the message is error-free. The CRC error detection logic asserts a flag if the register reads 0. If an error is present, the register reads non 0 and the flag is not asserted. The DUP11 does not count characters so it is the program's responsibility to look for the CRC error flag at the proper time.

#### 1.4.4 CRC Operation in SDLC Protocol

Under SDLC protocol control, CRC operation is slightly different than that described in Paragraph 1.4.1, Mathematical Background. The differences are:

- 1. The factor  $X^k$  ( $X^{15} + X^{14}$  .... + X + 1) is added to  $X^{n-k}$  [G(X)] which corresponds to initializing the transmitter CRC register to all 1s. This function protects against the obliteration of leading flags, which may not be detected if the register is 0.

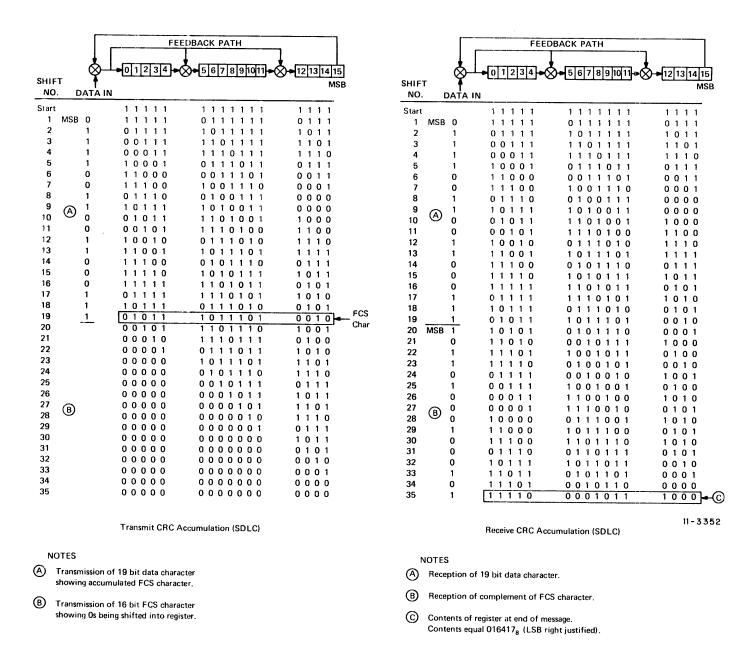

- 2. The accumulated BCC, which is called Frame Check Sequence (FCS) in the SDLC mode, is complemented before being transmitted. This results in a unique non-0 remainder (0164178) at the receiver. This protects against obliteration of terminating flags which may not be detected if the remainder is 0.

- 3. At the receiving station, the receiver CRC register is initialized to all 1s. The information plus the FCS constitutes the message and it is added to  $X^k$  ( $X^{15} + X^{14} \dots + X + 1$ ) and divided by P(X) to give 016417<sub>8</sub>, if the transmission is error-free. If an error is present, the flag is asserted. This CRC check is performed only when the flag is received.

# CHAPTER 2 INSTALLATION

#### 2.1 SCOPE

This chapter provides information for installing and checking out a DUP11 Synchronous Line Interface.

#### 2.2 UNPACKING AND INSPECTION

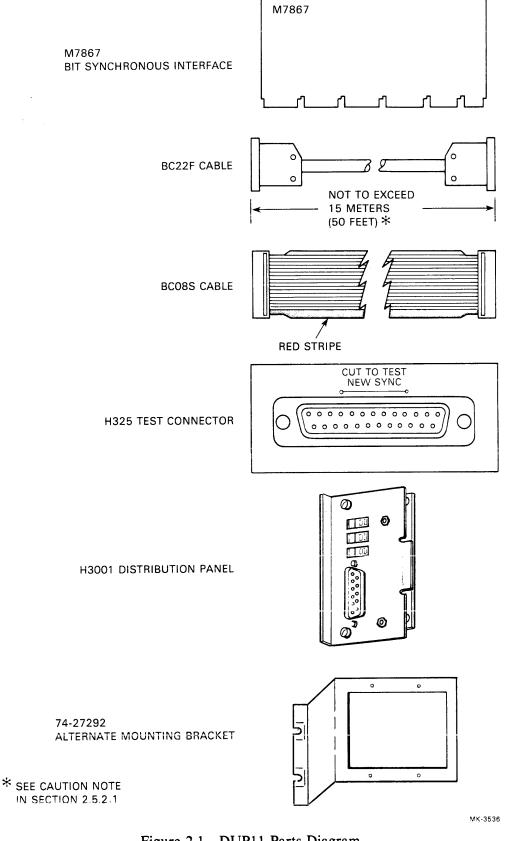

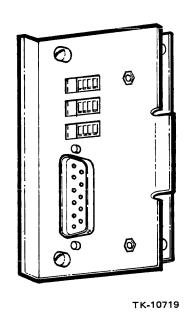

There is only one version of the DUP11 - the DUP11-DA; it consists of six items (refer to Figure 2-1).

M7867 Bit Synchronous Interface BC22F-25 Cable BC08S-10 Cable H325 Test Connector H3001 Distribution Panel 74-27292 Bracket\*

Inspect these parts for visible damage. Report any damage or shortage immediately to the shipper and the DIGITAL representative.

#### 2.3 TOOLS REQUIRED FOR INSTALLATION

The standard field service tool kit contains all the required tools for the installation of the DUP11.

#### 2.4 PREINSTALLATION SET-UP PROCEDURES

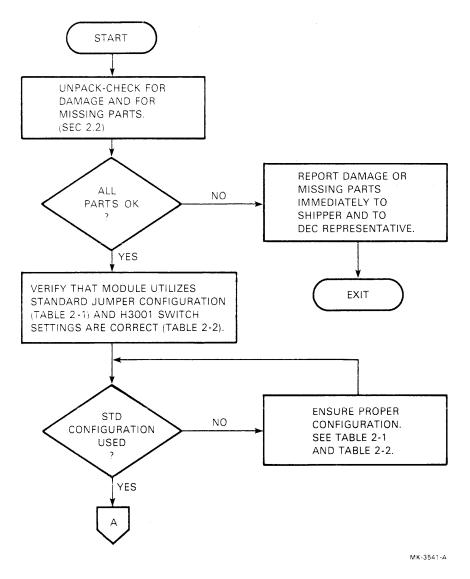

Before installing the DUP11 option, the following five steps must be performed.

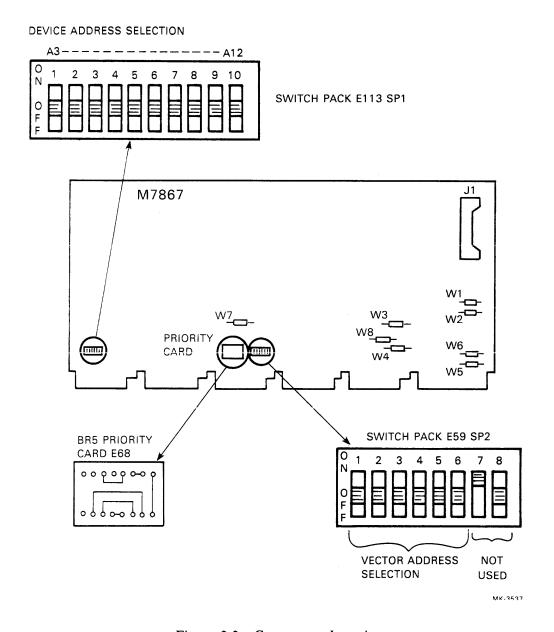

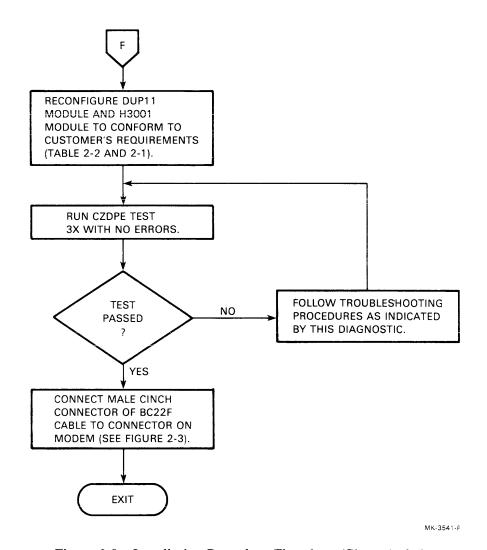

- 1. Examine the eight jumpers (W1 W8) on the M7867 module. Refer to Figure 2-2 to locate and identify the jumpers. All M7867 modules are shipped with the standard jumper configuration described in Table 2-1. All DUP11 diagnostics must be run on each M7867 utilizing the standard jumper configuration. After successfully completing the diagnostic testing in the shipped configuration, the M7867 may be reconfigured to meet the customer's requirements. MAINDEC CZDPE (DUP11 Quick Verify Test) should then be run to verify operation of the new configuration.

- 2. The DUP11 device address must be selected in accordance with Paragraph 2.9. For diagnostics, device address default = 760050.

- 3. The DUP11 vector address must be selected in accordance with Paragraph 2.10. For diagnostics, vector address default = 770.

<sup>\*</sup>Used in configurations not incorporating I/O bulkhead.

Figure 2-1 DUP11 Parts Diagram

Table 2-1 M7867 Jumper Configuration

| Jumper<br>Number | Standard<br>Configuration | Function                                                                                                                                                                                                                                                                                                             |  |  |

|------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <b>W</b> 1       | Installed                 | Secondary Receive Enable – With this jumper installed, the state of the data set Secondary Received Data line is received by the DUP11. This jumper is used in conjunction with jumper W2. With this jumper removed, pin JJ of the Berg header is available for some other function.                                 |  |  |

| W2               | Removed                   | Secondary Receive Disable – This jumper must be removed when W1 is installed. Conversely, it must be installed when W1 is removed. When installed, the EIA SEC REC receiver input is grounded; however, this has no effect on the Berg header, cable, or data set.                                                   |  |  |

| W3               | Installed                 | Clear option – With this jumper removed, the following bits cannot be directly cleared by DEVICE RESET or BUS INIT.                                                                                                                                                                                                  |  |  |

|                  |                           | Secondary Transmit Data (RXCSR bit 3) Request to Send (RXCSR bit 2) Data Terminal Ready (RXCSR bit 1)                                                                                                                                                                                                                |  |  |

|                  |                           | Some data sets may require that these connections be excluded from a device reset function.                                                                                                                                                                                                                          |  |  |

| W4               | Installed                 | Secondary Transmit Enable – With this jumper installed, the state of the Secondary Transmit Data line is sent to the data set. With this jumper removed, this signal is disconnected at the output of the EIA driver. Some data sets do not use this signal.                                                         |  |  |

| <b>W</b> 5       | Removed                   | A Data Set Control – With this jumper removed, positive transitions the Ring line and any transitions on the Clear to Send line set AD SET CH. This flag requests a receiver interrupt if the DSITEN bit been set by the program. With this jumper installed, any transition three additional lines set ADAT SET CH: |  |  |

|                  |                           | Carrier Data Set Ready Secondary Received Data                                                                                                                                                                                                                                                                       |  |  |

| W6               | Installed                 | A and B Data Set Control – With this jumper installed, transitions of the Carrier, Data Set Ready, and Secondary Received Data lines so BDAT SET CH. This signal is a flag only and does not request interupts. With this jumper removed, the BDAT SET CH flag (RXCS) bit 0) is inhibited.                           |  |  |

| W7               | Installed                 | NPR Latency Improvement With this jumper installed, the NPR latency improvement circuit in the interrupt control logic is enabled. This jumper should be removed only if the DUP11 is installed in a system using a KA11 processor with no KH11 latency reduction option.                                            |  |  |

| <b>W</b> 8       | Installed                 | External Clock Enable – Remove for Bell 201A modem.                                                                                                                                                                                                                                                                  |  |  |

- 4. Confirm that a BR5 priority plug is installed in the module. The diagnostics assume a BR5 priority level (see Figure 2-2 to locate and identify the BR5 plug).

- 5. Set up the H3001 module in accordance with Paragraph 2.7.

#### 2.5 INSTALLATION

Installation of the DUP11 is treated in two paragraphs. Paragraph 2.5.1 contains instructions for installing the M7867 module. Paragraph 2.5.2 contains instructions for installing the H3001 distribution panel

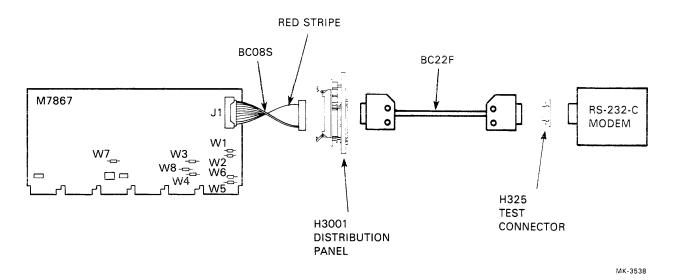

Examine Figure 2-3. This drawing shows the cabling configuration for the DUP11 installation.

Figure 2-2 Component Location

Figure 2-3 DUP11 Cabling

#### 2.5.1 M7867 Module Installation

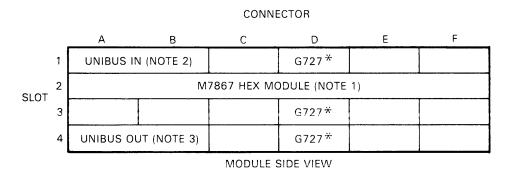

The DUP11 can be installed in any small peripheral controller (SPC) hex slot in the PDP-11 UNIBUS. Figure 2-4 shows the DD11-B system unit. This unit contains four slots but the DUP11 can only be installed in slots 2 and 3 because of the configuration of the prewired backplane.

# WARNING Turn all power OFF.

\*G727 GRANT CONTINUITY MODULE MUST BE INSTALLED IN EACH SLOT IN WHICH AN INTERFACE MODULE IS NOT INSTALLED.

#### NOTES

- 1. M7867 CAN BE MOUNTED ONLY IN SLOT 2 OR 3.

- 2. CAN BE M920 UNIBUS CONNECTOR OR BC11S UNIBUS CABLE.

- 3. CAN BE M920, BC11A, OR M930 UNIBUS TERMINATOR.

MK-3539

Figure 2-4 DUP11 (M7867 Module) Mounted in DD11-B

The M7867 installation procedure is as follows:

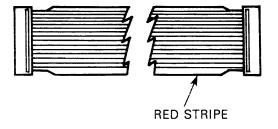

- 1. Connect the female Berg connector on the BC08S cable (ribbed side up) to the header on the M7867 module.

- 2. Plug the module into an SPC slot or into slot 2 or 3 of the DD11-B system unit.

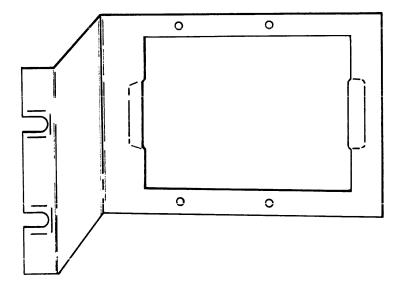

#### 2.5.2 H3001 Distribution Panel Installation

Two different approaches to installing the H3001 distribution panel assembly are included in this manual.

FCC regulations necessitate the incorporation of I/O bulkheads in most new installations to limit electromagnetic interference (EMI) leakage. For installations utilizing an I/O bulkhead, follow the steps outlined in Paragraph 2.5.2.1.

Alternate instructions are included for non-FCC compliant cabinets that require a slightly modified installation procedure. If the system does not incorporate an I/O bulkhead, follow the procedures in Paragraph 2.5.2.2.

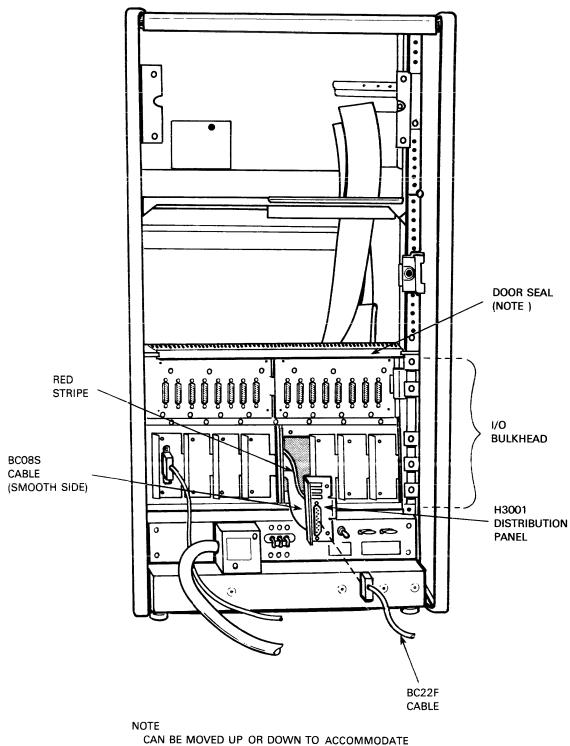

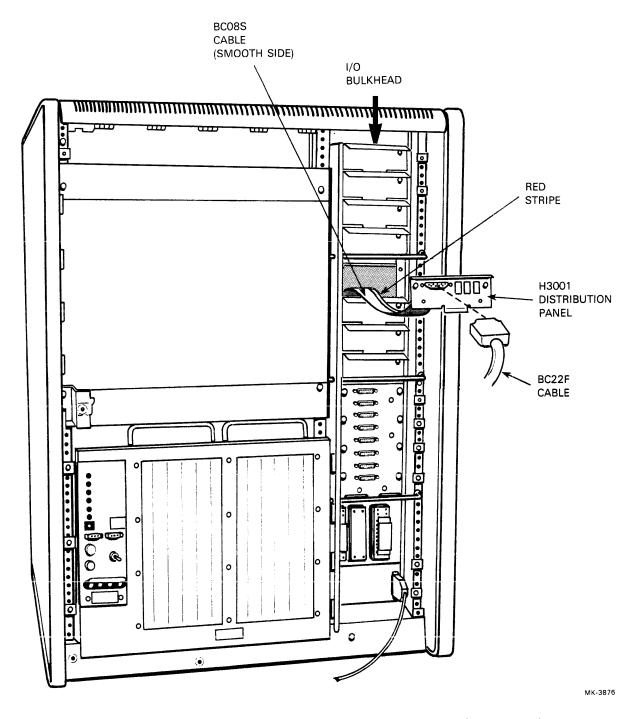

2.5.2.1 H3001 Installation In an I/O Bulkhead – The following instructions are for cabinets utilizing an I/O bulkhead. If a particular cabinet does not include an I/O bulkhead, omit these steps and follow the instructions in Paragraph 2.5.2.2.

Though there are differences in the orientation and positioning of I/O bulkheads of different levels of the PDP-11, the installation concept is the same. Once the H3001 distribution panel is installed, there should be no openings (panels omitted) left in the I/O frame on the rear of the cabinet which could permit EMI leakage. For this reason, it is important to tighten both mounting screws on the distribution panel. Figures 2-5 and 2-6 depict the various I/O bulkhead types and illustrate the correct approach to each.

- 1. Gain access to the I/O bulkhead through the door on the rear of the system cabinet and remove one of the 4.5 cm (2 in) wide panels on the bulkhead.

- 2. Route the remaining BC08S cable through the cabinet and through the opening in the I/O bulkhead at the rear of the cabinet. Keep in mind that the cable must be routed and dressed in a manner compatible with the existing cabinet cabling.

- 3. Plug the connector on the free end of the BC08S cable into the Berg connector on the rear of the H3001 distribution panel. Make sure that the ribbed side of the cable faces the pins lettered A to UU (not B to VV) of the Berg connector (see Figure 2-9). This assures pin to pin correspondence between the connectors of the M7867 and H3001 modules.

- 4. Install the panel into the opening of the I/O bulkhead in place of the 4.5 cm (2 in) panel that was removed in Step 1.

#### NOTE

It is imperative to maintain an interference-free environment outside the cabinet enclosure. Any additional panels that may have been removed to facilitate easier installation of the H3001 must be replaced in order to maintain the integrity of the I/O hulkhead.

CAN BE MOVED UP OR DOWN TO ACCOMMODATE ADDITION OF, OR REMOVAL OF I/O FRAMES.

MK-3875

Figure 2-5 H3001 Installation in a Horizontally Oriented I/O Bulkhead

Figure 2-6 H3001 Installation in a Vertically Oriented I/O Bulkhead

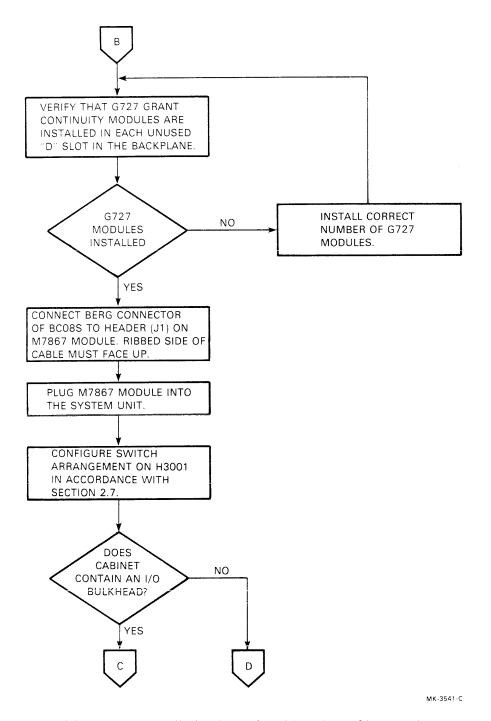

5. Connect the female Cinch connector of the BC22F cable to the 25-pin Cinch connector on the rear of the H3001 module. The cable should exit the cabinet with the other signal cables.

#### CAUTION

BC22F cable lengths in excess of 7.62 meters (25 feet) may exceed the maximum load capacitance defined by the RS-232-C specification. Note, however, that up to 15 meters (50 feet) provides satisfactory DUP11 performance levels.

- 6. Connect the other end of the BC22F cable to the modem or to the H325 test connector which is the configuration assumed by the diagnostics.

- 7. Turn power ON.

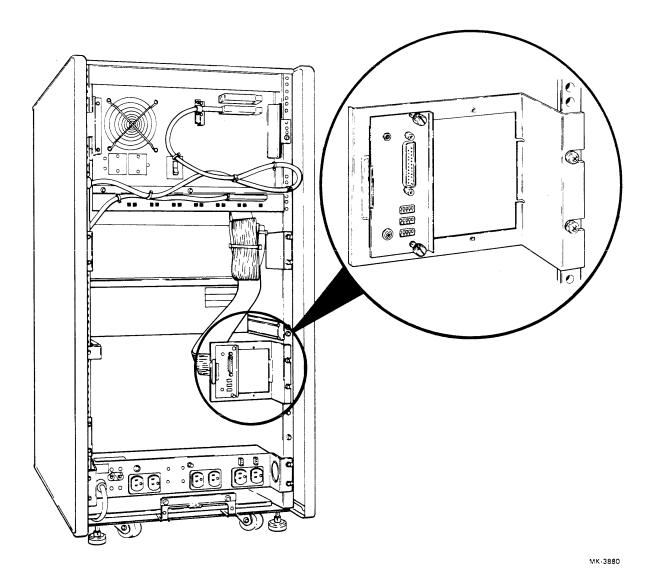

#### 2.5.2.2 H3001 Installation in Cabinets Without an I/O Bulkhead –

- 1. Gain access to the rear of the system cabinet and mount the bracket (Part No. 74-27292) to one of the rear side rails as shown in Figure 2-7. Mount the H3001 distribution panel into the bracket.

- 2. Route the remaining BC08S cable through the cabinet and to the bracket at the rear of the cabinet. Keep in mind that the cable must be routed and dressed in a manner compatible with the existing cabinet cabling.

- 3. Plug the connector on the free end of the BCO8S cable into the Berg connector on the rear of the H3001 distribution panel. Make sure that the ribbed side of the cable faces the pins lettered A to UU (not B to VV) of the Berg connector (see Figure 2-9). This assures pin to pin correspondence between the connectors of the M7867 and H3001 modules.

- 4. Connect the female Cinch connector of the BC22F cable to the 25-pin Cinch connector on the rear of the H3001 module. The cable should exit the cabinet with the other signal cables.

#### **CAUTION**

BC22F cable lengths in excess of 7.62 meters (25 feet) may exceed the maximum load capacitance defined by the RS-232-C specification. Note, however, that up to 15 meters (50 feet) provides satisfactory DUP11 performance levels.

- 5. Connect the other end of the BC22F cable to the modem or to the H325 test connector which is the configuration assumed by the diagnostics.

- 6. Configure the H3001 panel switches according to the chart in Table 2-2.

- 7. Turn power ON.

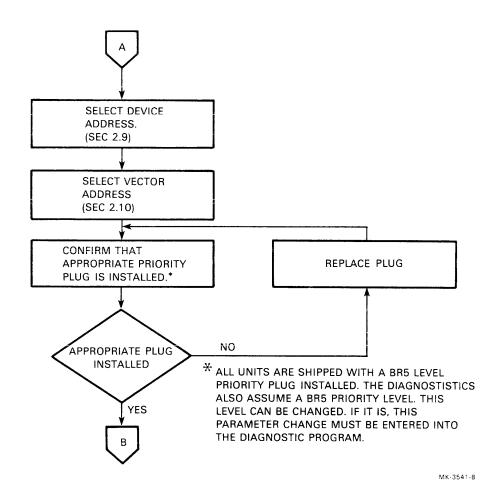

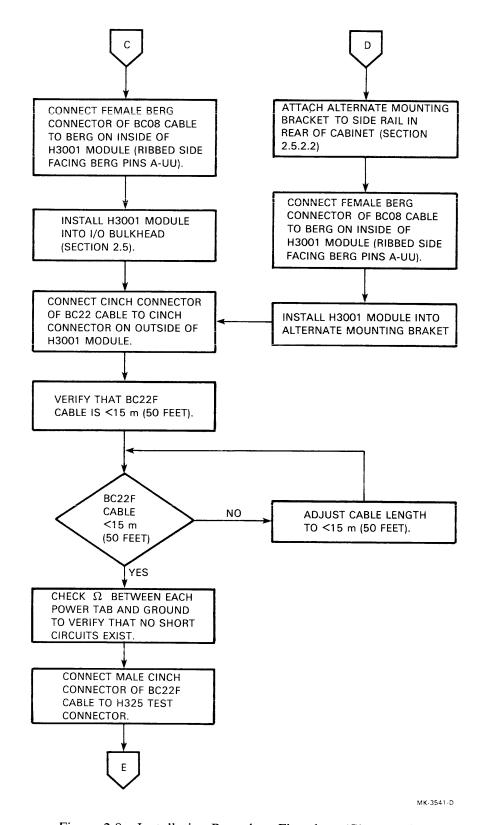

Figure 2-8 is included for convenience. Use this figure for quick reference when installing the DUP11 option.

Figure 2-7 Side Rail Installation of H3001 Distribution Panel

Table 2-2 H3001 Switch Settings

|   |     | Brill 3. | PELL 3 | \$\$\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | \$ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ | \$ /<br>\$ / |

|---|-----|----------|--------|------------------------------------------|-------------------------------------------|--------------|

|   | S1  |          |        |                                          | ON                                        |              |

|   | S2  |          |        |                                          |                                           |              |

|   | S3  |          |        |                                          |                                           | :            |

|   | S4  |          |        |                                          |                                           |              |

|   | S5  |          |        |                                          | ON                                        |              |

|   | S6  |          |        |                                          |                                           |              |

|   | S7  |          |        |                                          |                                           |              |

| • | S8  |          |        |                                          |                                           |              |

|   | S9  |          |        |                                          |                                           |              |

|   | S10 | *        |        |                                          |                                           |              |

|   | S11 |          |        |                                          |                                           |              |

|   | S12 |          |        |                                          |                                           |              |

| ^ | S13 |          |        |                                          |                                           |              |

|   | S14 |          |        |                                          |                                           |              |

|   | S15 |          |        |                                          |                                           |              |

SWITCHES ARE OFF UNLESS OTHERWISE INDICATED

MK-3838

$<sup>^{</sup> imes}$  ON IF NEW SYNC CONFIGURED ON M7867

Figure 2-8 Installation Procedure Flowchart (Sheet 1 of 6)

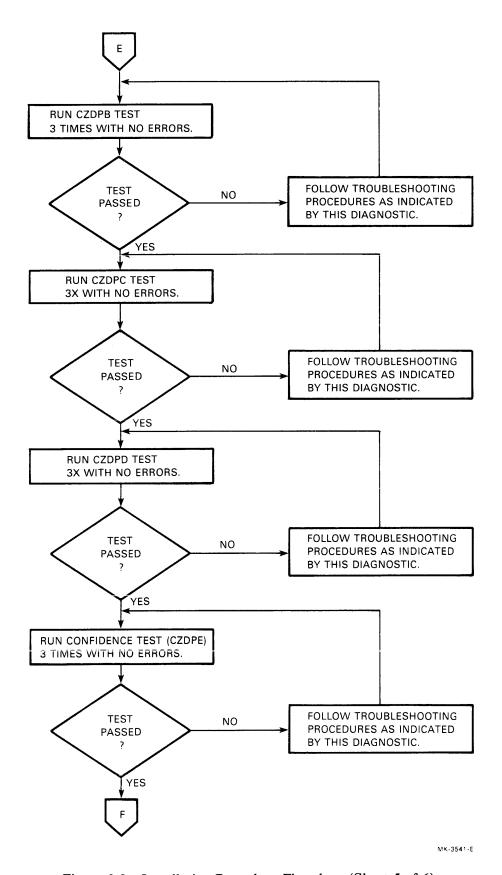

Figure 2-8 Installation Procedure Flowchart (Sheet 2 of 6)

Figure 2-8 Installation Procedure Flowchart (Sheet 3 of 6)

Figure 2-8 Installation Procedure Flowchart (Sheet 4 of 6)

Figure 2-8 Installation Procedure Flowchart (Sheet 5 of 6)

Figure 2-8 Installation Procedure Flowchart (Sheet 6 of 6)

#### 2.6 VERIFICATION OF HARDWARE OPERATION

Verification of proper DUP11 operation is performed by a series of diagnostic programs. A general description of the diagnostics is included in Chapter 5, Maintenance. Details on the content and use of the diagnostics is contained in the diagnostic documentation package supplied with the DUP11.

Proceed as follows:

1. Run the following diagnostics in the following order:

CZDPB - Basic and Off-line Transmitter Tests

CZDPC - Off-line and SDLC Receiver Tests and Off-line Modem Control and Interrupt Tests

CZDPD – Off-line SDLC and DEC MODE Data and Function Tests

2. Run diagnostic CZDPE. This is a confidence test that requires a dialog with the user to ensure proper setting of the DUP11 and system parameters. It offers a quick test to verify that the DUP11 is operational.

Each diagnostic must make three passes without an error.

Reconfigure the H3001 and the DUP11 in accordance with the customer's requirements (Tables 2-1 and 2-2). Then run diagnostic CZDPE (DUP11 quick verify test) to check the final configuration.

System testing consists of running DECX11 module CXDPB to exercise all DUP11s in a system. Run DECX11 until three error-free passes of module CXDPB are obtained. Note that only four DUP11s can be tested with one DECX11 module.

#### 2.7 COMPATIBILITY

The DUP11 is compatible with the DF03 and Bell type 201<sup>tm</sup>, 208<sup>tm</sup>, and 209<sup>tm</sup> modems or equivalent. In addition, compatibility with these and other modems is enhanced through the incorporation of the H3001 distribution panel.

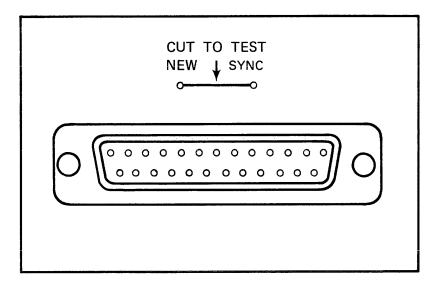

Adjust the switches on the H3001 to correspond to the settings indicated in Table 2-2 for the particular modem used in your configuration. The H3001 switches are contained in three DIP switch packages grouped together on the H3001 modules. Refer to Figure 2-9 for the location of these switches. The switches are rocker or slide type and are pushed to the desired position.

A schematic of the H3001 distribution panel is included in Chapter 5 (Figure 5-1). Use this figure as an aid in determining the proper switch settings and jumper configuration if the modem used is not listed in Table 2-2.

Jumper W1 (see Figure 2-9) is normally not installed. Install this jumper when RS-232 protective ground (pin 1 of Cinch connector) must be connected to enclosure ground. Note that this may introduce an undesirable ground loop.

Figure 2-9 H3001 Distribution Panel

# **NOTE**

Due to the extensive variety of modems currently available, DIGITAL cannot guarantee that the DUP11 interface will fully support all features of every modem.

# 2.8 POWER REQUIREMENTS

The DUP11 requires the following power:

- +5 V at 3.6 A

- +15 V at 75 mA

- -15 V at 75 mA

# 2.9 DEVICE ADDRESSES

#### 2.9.1 Introduction

Starting with the DJ11, new communications devices are to be assigned floating addresses. The addresses for current production devices are to be retained. The word *floating* means that addresses are not assigned absolutely for the maximum number of each communications device that can be used in a system.

#### 2.9.2 Floating Device Address Assignment

Floating device addresses are assigned as follows:

- 1. The floating address space starts at location 760010 and extends to location 764000 (octal designations).

- 2. The devices are assigned in order by type: DJ11, DH11, DQ11, DU11, and DUP11; then the next device is introduced into production. Multiple devices of the same type must be assigned contiguous addresses.

- 3. The first address of a new type device must start on a modulo 10<sub>8</sub> boundary, if it contains one to four bus-addressable registers. The starting address of the DH11 must be on a modulo 20<sub>8</sub> boundary because the DH11 has eight registers.

- 4. A gap of 10<sub>8</sub>, starting on a modulo 10<sub>8</sub> boundary, must be left between the last address of one type device and the first address of the next type device. A gap must be left for any device on the list that is not used if the device following it is used. The equivalent of a gap should be left after the last assigned device to indicate that nothing follows.

- 5. A new type device cannot be inserted ahead of a device on the list.

- 6. If additional devices on the list are to be added to a system, they must be assigned contiguously after the original devices of the same type. Reassignment of other type devices already in the system may be required to make room for the additions.

The following examples show typical floating device assignments for communications devices in a system:

# EXAMPLE 1: No DJ11s, 2 DH11s, 2 DQ11s, and 1 DUP11

```

760010

DJ11 gap

DH11 #0 first address

760020

760040

DH11 #1 first address

760060

DH11 gap

DQ11 #0 first address

760070

760110

DQ11 gap

760120

DU11 gap

760130

DUP11 #0 first address

Indicates no more DUP11s and no other devices follow.

760140

```

#### **EXAMPLE 2: 1 DJ11, 1 DH11, 2 DQ11s, and DUP11s**

```

760010

DJ11 #0 first address

760020

DJ11 gap

760040

DH11 #0 first address

760060

DH11 gap

760070

DQ11 #0 first address

DQ11 #1 first address

760100

760110

DQ11 gap

DUP11 gap

760120

DUP11 #0 first address

760130

DUP11 #1 first address

760140

Indicates no more DUP11s and no other devices follow.

760150

```

#### **EXAMPLE 3: 1 DUP11**

| 760010 | DJ11 gap               |

|--------|------------------------|

| 760020 | DH11 gap               |

| 760030 | DQ11 gap               |

| 760040 | DU11 gap               |

| 760050 | DUP11 #0 first address |

760060 Indicates no more DUP11s and no other devices follow.

#### 2.9.3 Device Address Selection

In the floating address space (760010-764000), bits 13-17 are always 1s (function of PDP-11 processor). Appendix B shows the PDP-11 memory organization and addressing conventions. Bits 3-12 are selected by switches in the address decoding logic (Table 2-3). With the switch ON (closed), the decoder looks for a 0 on the associated UNIBUS address line; conversely, with the switch OFF (open), the decoder looks for a 1 on the associated UNIBUS address line. Bits 1 and 2 are decoded to select one of four registers. They determine the least significant digit (octal) of the device address because bit 0 is not used for address decoding. It is used to select the proper byte during byte transactions.

Table 2-3 Guide for Setting Switches to Select Device Address

| Switch No. | 10<br>12 | 9<br>11    | 8<br>10 | 7<br>9 | 6<br>8 | 5 | 4  | 3 | 2 | 1 3 | Device<br>Address |

|------------|----------|------------|---------|--------|--------|---|----|---|---|-----|-------------------|

| Bit No.    | 12       | 11         | 10      | 9      | 0      |   | 0  | 3 | 4 | 3   | Address           |

|            |          |            |         |        |        |   |    |   |   | X   | 760010            |

|            |          |            |         |        |        |   |    |   | X |     | 760020            |

|            |          |            |         |        |        |   |    |   | X | X   | 760030            |

|            |          |            |         |        |        |   |    | X |   |     | 760040            |

|            |          |            |         |        |        |   |    | X |   | X   | 760050            |

|            |          |            |         |        |        |   |    | X | X |     | 760060            |

| 1          |          |            |         |        |        |   | ** | X | X | X   | 760070            |

|            |          |            |         |        |        |   | X  |   |   |     | 760100            |

|            | :        |            |         |        |        | X |    |   |   |     | 760200            |

|            |          |            |         |        |        | X | X  |   |   |     | 760300            |

|            |          |            |         |        | X      |   |    |   |   |     | 760400            |

|            |          | - American |         |        | X      |   | X  |   |   |     | 760500            |

|            |          |            |         |        | X      | X |    |   |   |     | 760600            |

|            |          |            |         |        | X      | X | X  |   |   |     | 760700            |

|            |          |            |         | X      |        |   |    |   |   |     | 761000            |

|            |          |            | x       |        |        |   |    |   |   |     | 762000            |

|            |          |            | х       | X      |        |   |    |   |   |     | 763000            |

|            |          | X          |         |        |        |   |    |   |   |     | 764000            |

Notes:

<sup>1.</sup> X means switch off (open) to respond to logical 1 on the Unibus.

<sup>2.</sup> Switch numbers are physical positions in switch package 1.

#### **Switch Identification**

The device address selection switches are contained in one DIP switch package (E113). Refer to Figure 2-2 for the location of the package. All ten switches in the package are used. The correlation between switch numbers and bit numbers is shown in Table 2-3. The ON and OFF positions and the switch numbers are marked on the package. The switches are rocker or slide type and are pushed to the desired position.

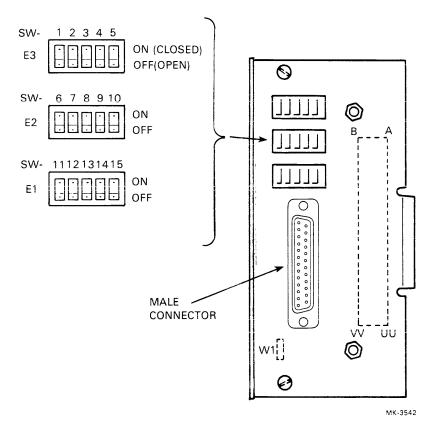

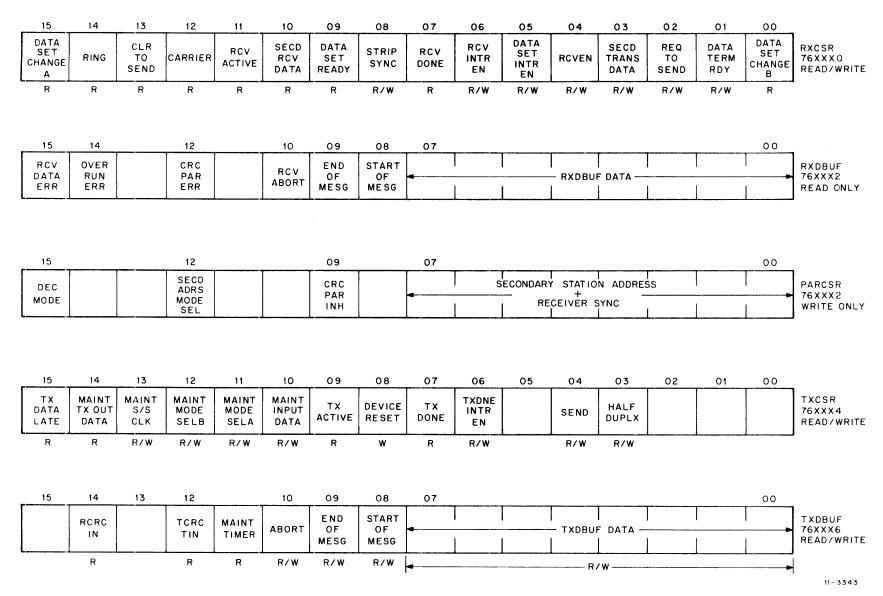

The DUP11 requires four addresses:

- 76XXX0 Receiver Control and Status Register

- 76XXX2 Receiver Data Buffer Register (Read Only) and Parameter Control and Status Register (Write Only)

- 76XXX4 Transmitter Control and Status Register

- 76XXX6 Transmitter Data Buffer Register

#### 2.10 VECTOR ADDRESSES

#### 2.10.1 Introduction

Communications devices are assigned floating vector addresses. This eliminates the necessity of assigning addresses absolutely for the maximum number of each device that can be used in the system.

# 2.10.2 Floating Vector Address Assignment

Floating vector addresses are assigned as follows:

- 1. The floating address space starts at location 300 and proceeds upward to 777. Addresses 500-534 are reserved.

- 2. The devices are assigned in order by type: DC11; KL11/DL11-A, -B; DP11; DM11-A: DN11; DM11-BB; DR11-A; DR11-C; PA611 Reader; PA611 Punch; DT11; DX11; DL11-C, -D -E; DJ11; DH11; GT40; LPS11; VT20; DQ11; KW11-W; DU11; DUP11; and DV11.

- 3. If any type device is not used in a system, address assignments move up to fill the vacancies.

- 4. If additional devices are to be added to the system, they must be assigned contiguously after the original devices of the same type. Reassignment of other type devices already in the system may be required.

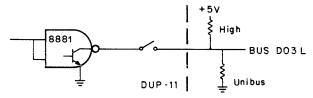

## 2.10.3 Vector Address Selection

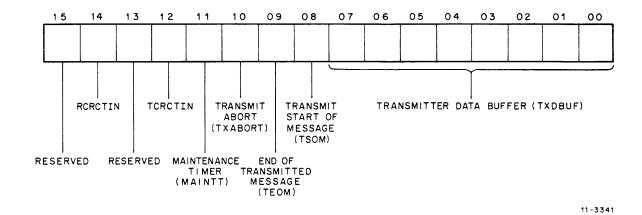

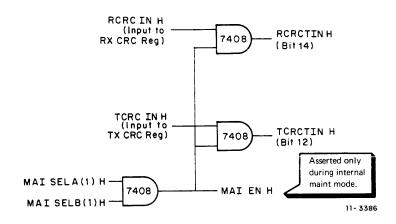

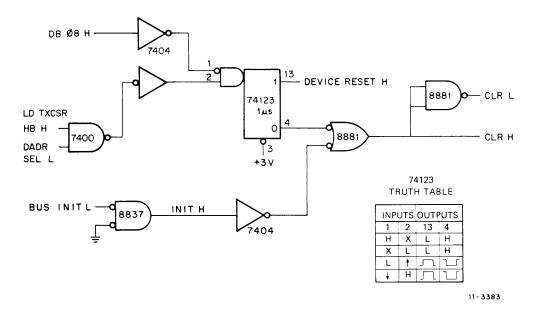

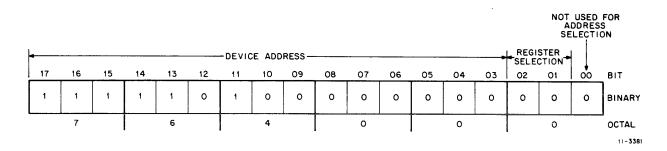

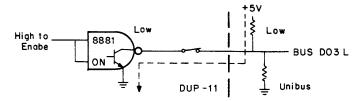

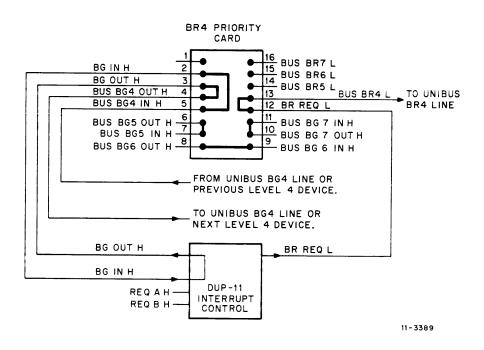

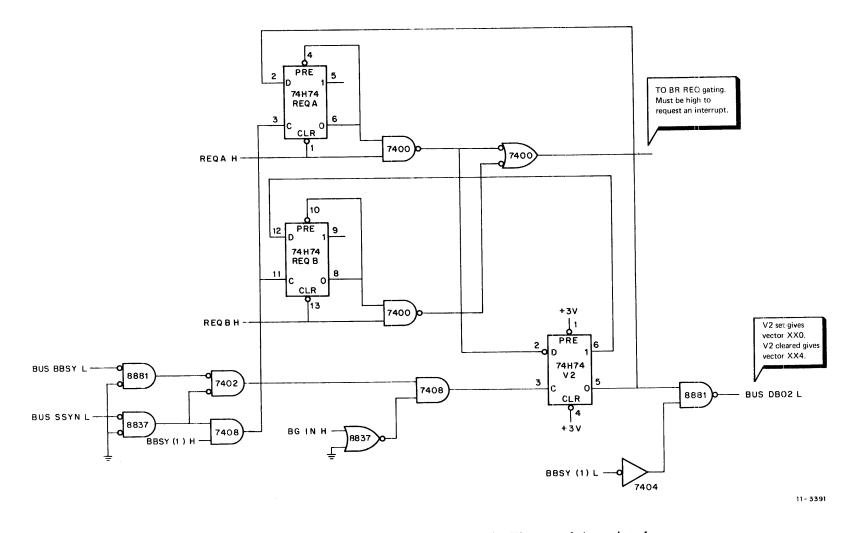

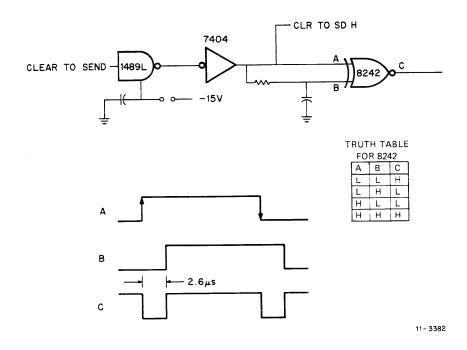

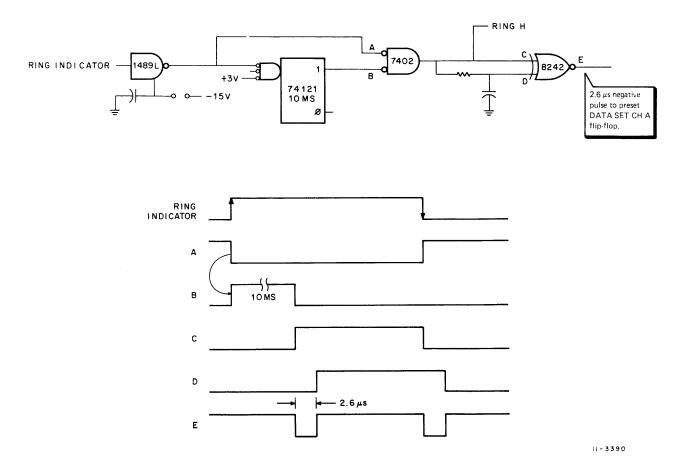

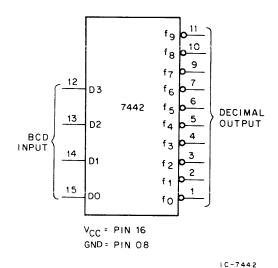

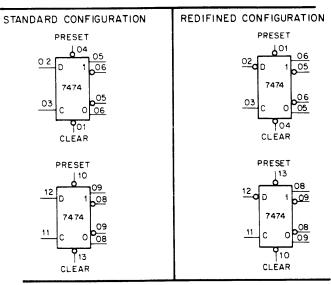

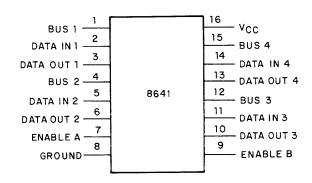

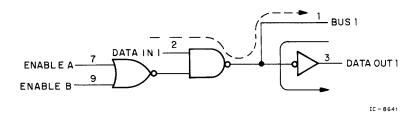

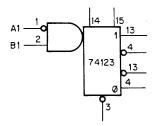

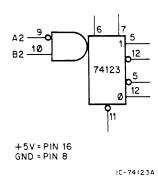

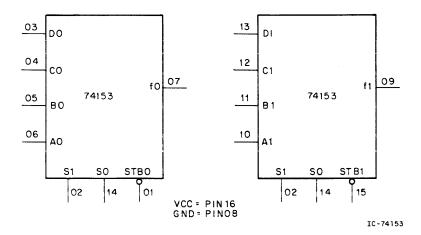

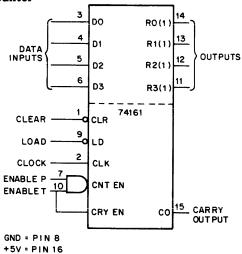

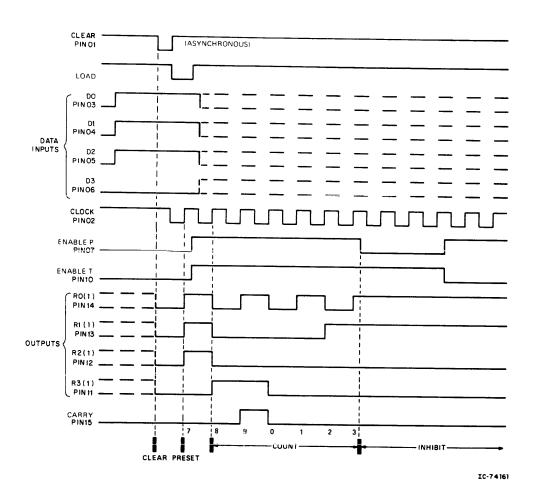

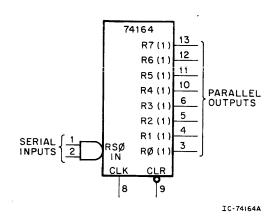

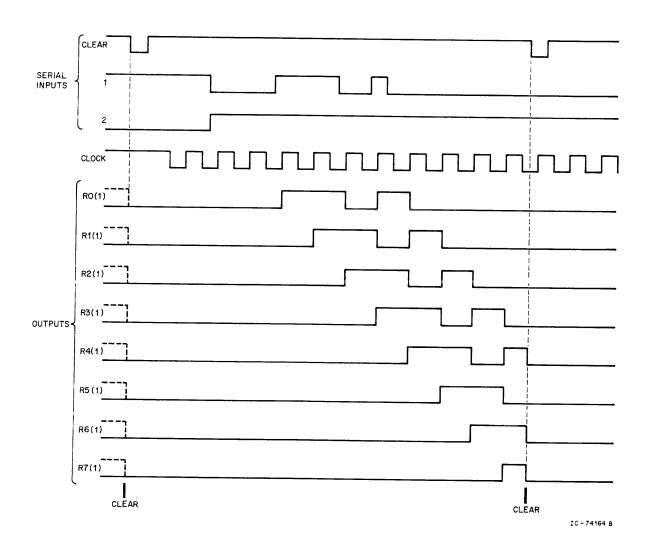

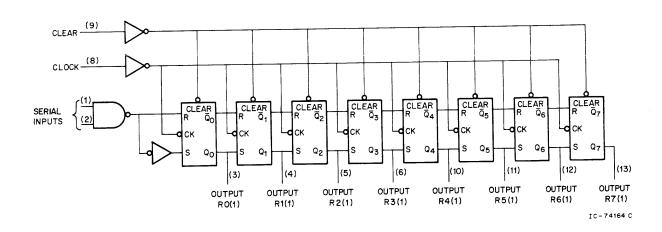

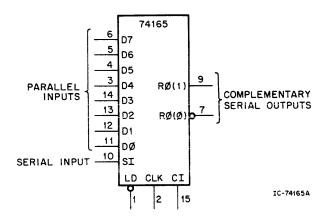

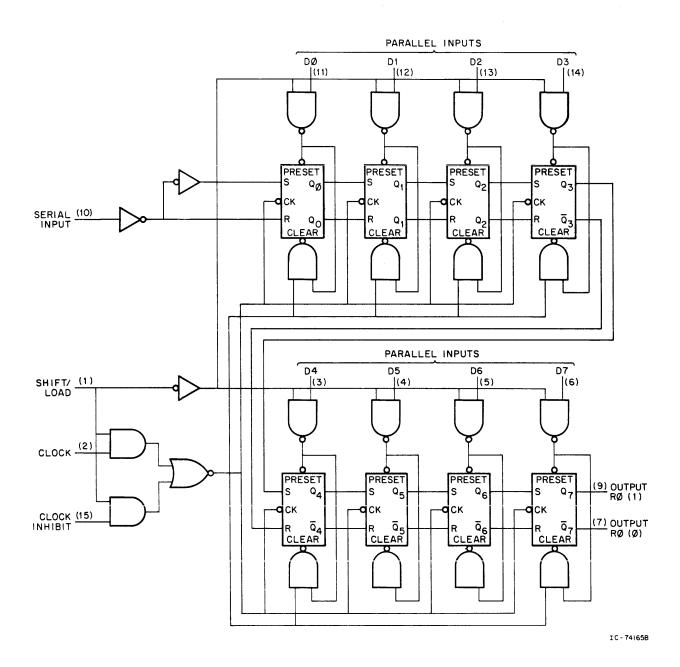

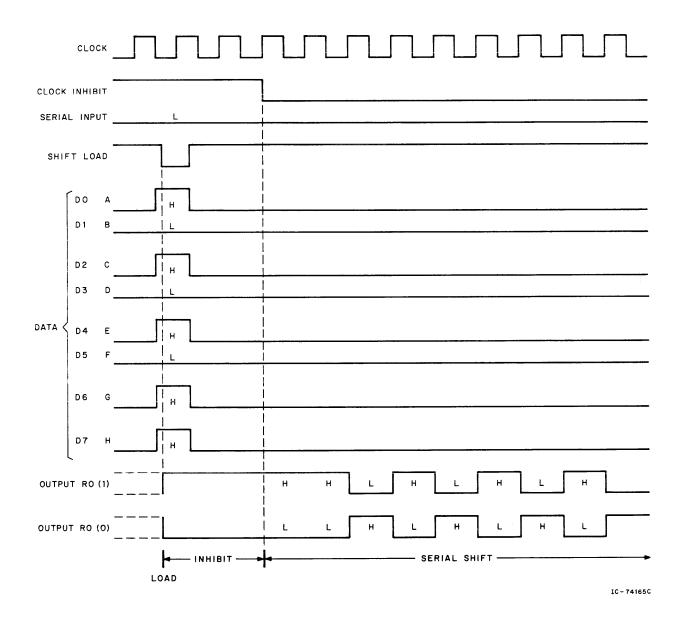

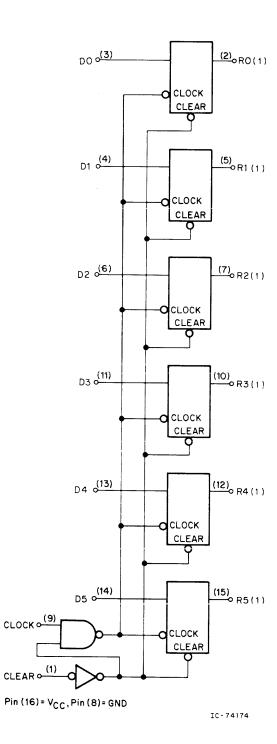

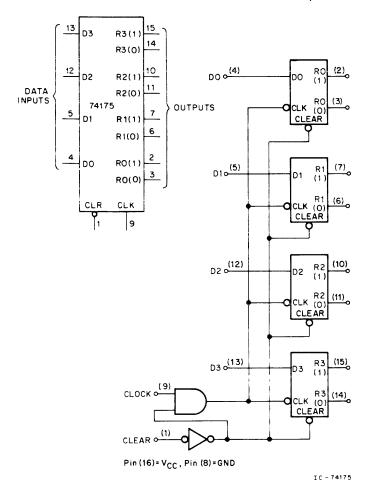

Each device interrupt vector requires four address locations (two words) which implies only even-numbered addresses. A further constraint is that all vector addresses must end in 0 or 4. The vector address is specified as a three-digit, binary-coded, octal number using UNIBUS data bits 0-8. Because the vector must end in 0 or 4, bits 1 or 0 are not specified (they are always 0) and bit 2 determines the least significant octal digit of the vector address (0 or 4). The interrupt control logic sends only seven bits (2-8) to the PDP-11 processor to represent the vector address.