DU11 single line programmable synchronous interface maintenance manual

### EK-DU11-MM-001

DU11 single line programmable synchronous interface maintenance manual

digital equipment corporation · maynard, massachusetts

Preliminary Edition, October 1973 1st Edition, January 1974 2nd Printing, March 1974 3rd Printing, December 1974

#### Copyright © 1973, 1974 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

> DEC FLIP CHIP DIGITAL UNIBUS

PDP FOCÁL COMPUTER LAB

## CONTENTS

a

| CHAPTER 1 | INTRODUCTION                              |

|-----------|-------------------------------------------|

| 1.1       | SCOPE                                     |

| 1.2       | DATA COMMUNICATION TECHNIQUES AND SYSTEMS |

| 1.2.1     | Data Communication Techniques             |

| 1.2.1.1   | Pulse Coding                              |

| 1.2.1.2   | Pulse Code Transmission                   |

| 1.2.2     | Data Communication Systems                |

| 1.2.2.1   | Synchronous Systems                       |

| 1.2.2.1   |                                           |

|           | Computer Application 1-5                  |

| 1.3       | GENERAL DESCRIPTION                       |

| 1.4       | PHYSICAL DESCRIPTION 1-5                  |

| 1.5       | SPECIFICATIONS 1-6                        |

| 1.5.1     | Environmental                             |

| 1.5.2     | Electrical                                |

| 1.5.3     | Performance                               |

| 1.5.3.1   | Baud Rates for Synchronous Communications |

| 1.5.3.2   | Baud Rates for Isochronous Communications |

| 1.6       | ENGINEERING DRAWINGS 1-6                  |

| 1.6.1     | Basic Signal Names                        |

| 1.6.2     | Flip-Flop Signal Names 1-8                |

| 1.0.2     | 1、1、1、1、1、1、1、1、1、1、1、1、1、1、1、1、1、1、1、    |

| CHAPTER 2 | INSTALLATION                              |

| 2.1       | INSTALLATION                              |

| 2.1.1     | Mounting the DU11 in the Computer         |

| 2.1.1.1   | Standard Configuration                    |

| 2.1.1.2   | Current Mode Configuration                |

| 2.1.2     | Installing the Modem Cable Harness        |

| 2.1.2     |                                           |

| 2.1.3     | 1 0                                       |

|           | Jumper Assignments                        |

| 2.1.5     | Priority Assignment                       |

| 2.2       | INITIAL TESTING                           |

| CHAPTER 3 | DEVICE REGISTERS AND INTERRUPT REQUESTS   |

|           |                                           |

| 3.1       | SCOPE                                     |

| 3.2       | DEVICE REGISTERS                          |

| 3.2.1     | Register Address Assignments 3-1          |

| 3.2.2     | Register Title and Bit Assignments        |

| 3.2.2.1   | Title Assignments    3-1                  |

| 3.2.2.2   | Bit Assignments                           |

| 3.3       | INTERRUPT REQUESTS                        |

| CUADTED 4 | THEORY OF ODER ATION                      |

| CHAPTER 4 | THEORY OF OPERATION                       |

| 4.1       | <b>SCOPE .</b>                            |

| 4.2       | FUNCTIONAL DESCRIPTION 4-1                |

| 4.2.1     | Initialization and Programming            |

| 4.2.2     | Handshaking Sequence                      |

| 4.2.3     | Basic Operation                           |

| 4.2.4     | Data Flow Analysis 4-7                    |

## **CONTENTS** (Cont)

Page

e,

| 4.2.4.1   | Data Source and Destination                                                                                 |

|-----------|-------------------------------------------------------------------------------------------------------------|

| 4.2.4.2   | Data Flow                                                                                                   |

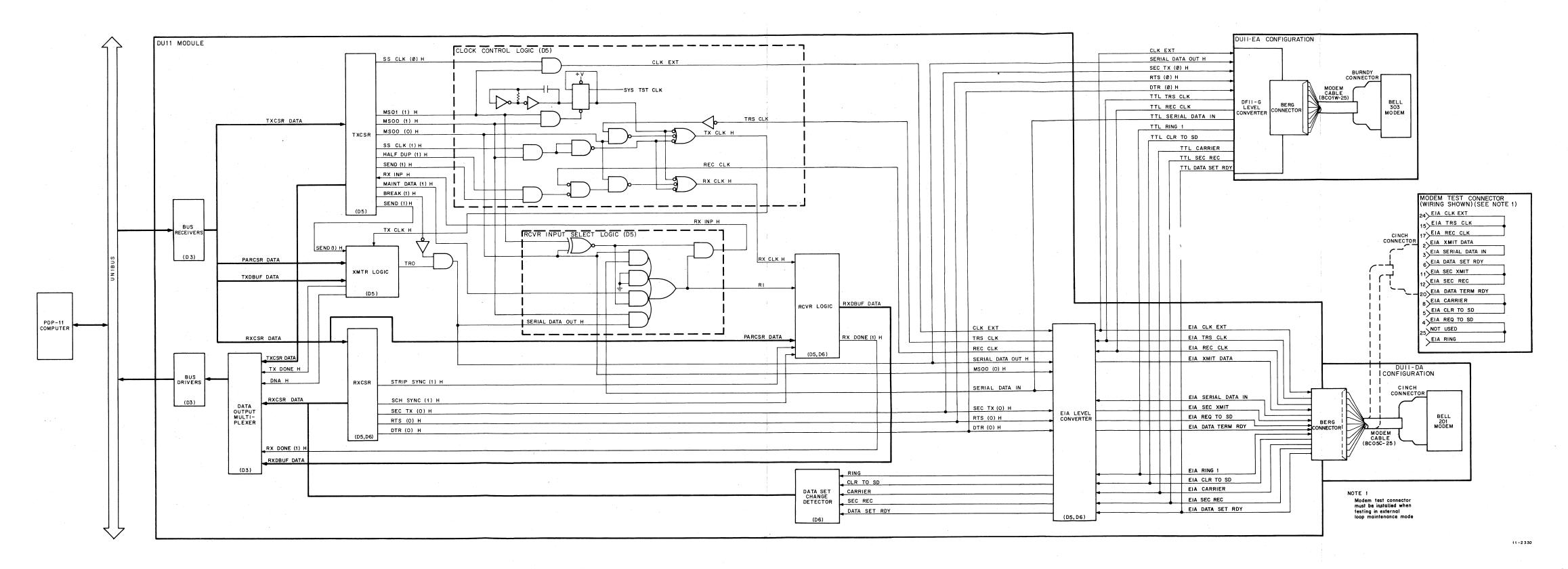

| 4.2.5     | Functional Block Diagram Description                                                                        |

| 4.2.5.1   | Clear Logic                                                                                                 |

| 4.2.5.2   | Address Selection and Mode Control Logic                                                                    |

| 4.2.5.3   | Receiver Status Register (RXCSR) 4-11                                                                       |

| 4.2.5.4   | Transmitter Status Register (TXCSR)                                                                         |

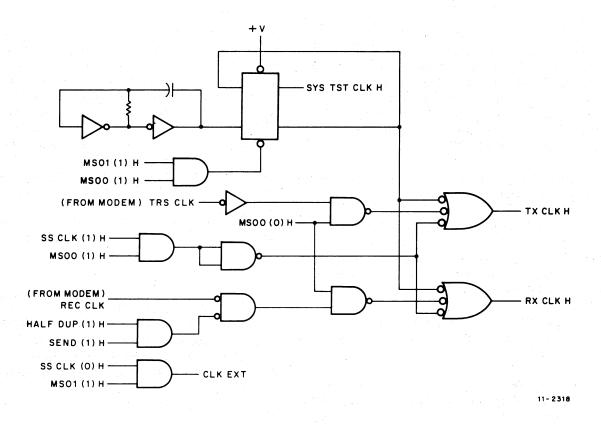

| 4.2.5.5   | Clock Control Logic                                                                                         |

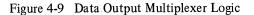

| 4.2.5.6   | RCVR Input Select Logic                                                                                     |

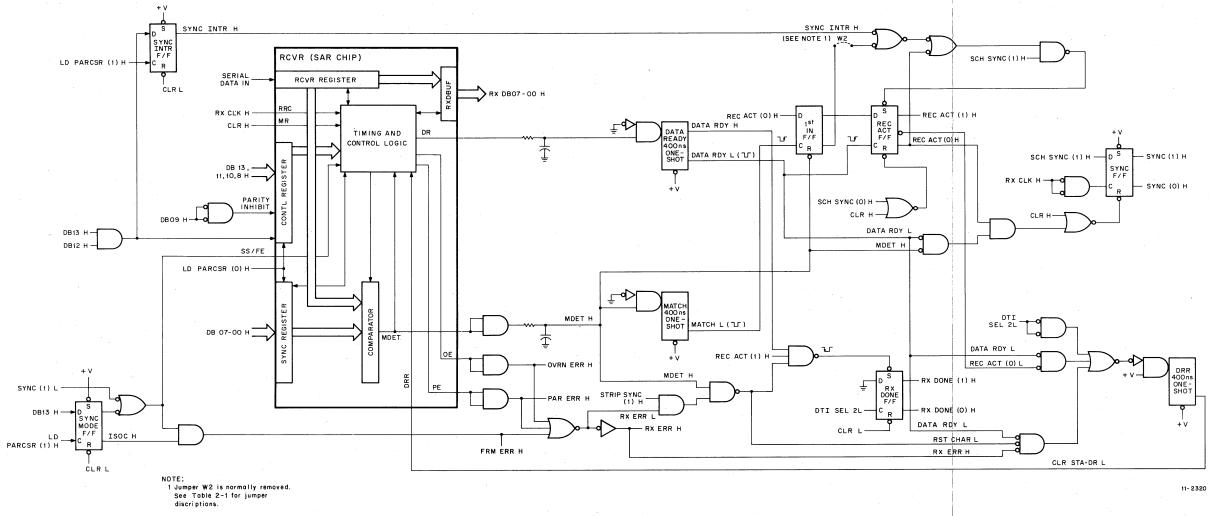

| 4.2.5.7   | $\mathbf{RCVR} \ Logic \ \ldots \ $ |

| 4.2.5.8   | XMTR Logic                                                                                                  |

| 4.2.5.9   | Data Set Change Detector                                                                                    |

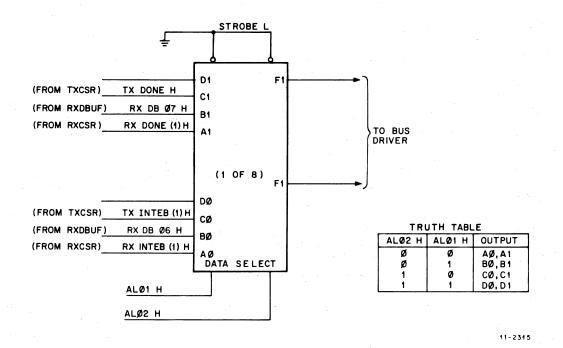

| 4.2.5.10  | Data Output Multiplexer                                                                                     |

| 4.2.5.11  | Bus Drivers                                                                                                 |

| 4.2.5.12  | Interrupt Control Logic                                                                                     |

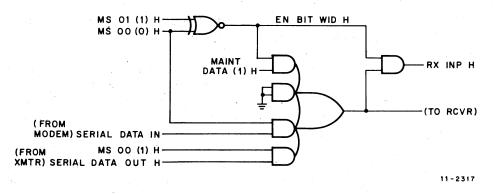

| 4.2.5.13  | EIA Level Converters                                                                                        |

| 4.3       | DETAILED DESCRIPTION                                                                                        |

|           | Clear Logic                                                                                                 |

| 4.3.1     | Address Selection and Mode Control Logic                                                                    |

| 4.3.2     |                                                                                                             |

| 4.3.2.1   | Typical DATI Logic Operation                                                                                |

| 4.3.2.2   | Typical DATOB Logic Operation                                                                               |

| 4.3.2.3   | Typical DATO Logic Operation                                                                                |

| 4.3.3     | Data Output Multiplexer Logic                                                                               |

| 4.3.4     | RCVR Input Select Logic                                                                                     |

| 4.3.5     | Clock Control Logic                                                                                         |

| 4.3.6     | RCVR Logic                                                                                                  |

| 4.3.6.1   | RCVR Logic Initialization and Programming                                                                   |

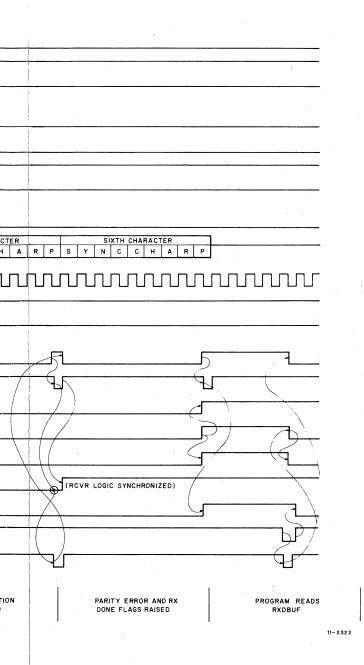

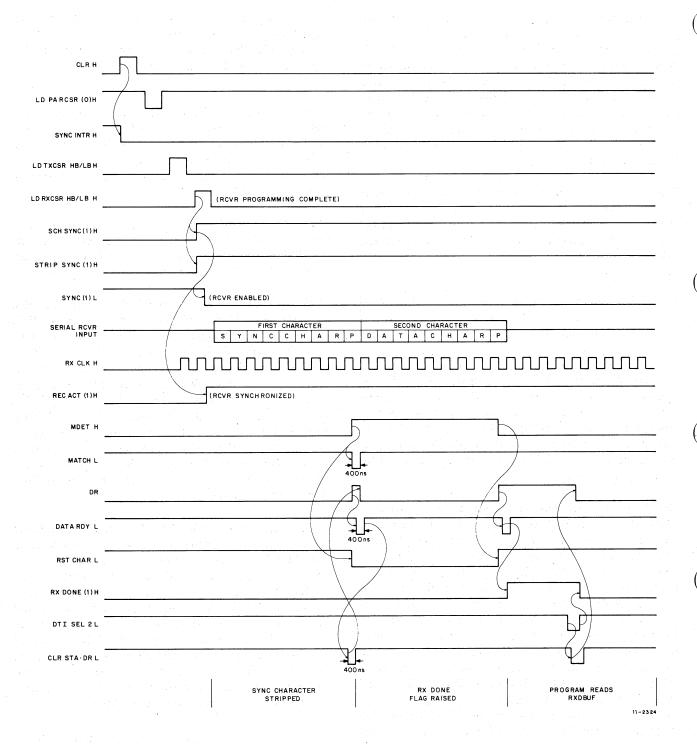

| 4.3.6.2   | RCVR Logic Operation                                                                                        |

| 4.3.7     | XMTR Logic                                                                                                  |

| 4.3.7.1   | XMTR Logic Initialization and Programming                                                                   |

| 4.3.7.2   | XMTR Logic Operation                                                                                        |

| 4.3.8     | Data Set Change Detector Logic                                                                              |

| 4.3.9     | Interrupt Control Logic                                                                                     |

|           |                                                                                                             |

| CHAPTER 5 | PROGRAMMING REQUIREMENTS AND RECOMMENDATIONS                                                                |

| 5.1       | INTRODUCTION                                                                                                |

| 5.2       | PROGRAMMING THE TRANSMITTER IN THE SYNCHRONOUS MODE 5-1                                                     |

| 5.2.1     | Loading the PARCSR 5-1                                                                                      |

| 5.2.2     | Enabling the Transmitter                                                                                    |

| 5.2.3     | Detecting the Last Character of the Message                                                                 |

| 5.2.4     | Transmitting Initial Sync Characters to Establish Synchronization                                           |

| 5.2.5     | Transmitting Sync Characters to Maintain Synchronization                                                    |

| 5.3       | PROGRAMMING THE RCVR IN THE INTERNAL SYNCHRONOUS MODE                                                       |

| 5.4       | PROGRAMMING THE RCVR IN THE EXTERNAL SYNCHRONOUS MODE                                                       |

| 5.5       | PROGRAMMING THE XMTR IN THE ISOCHRONOUS MODE                                                                |

| 5.5.1     | Loading the PARCSR                                                                                          |

| 5.5.2     | Enabling the XMTR                                                                                           |

| 5.6       | PROGRAMMING THE RCVR IN THE ISOCHRONOUS MODE                                                                |

| 5.0       |                                                                                                             |

## CONTENTS (Cont)

| CHAPTER 6 | MAINTENANCE                |

|-----------|----------------------------|

| 6.1       | SCOPE                      |

| 6.2       | MAINTENANCE PHILOSOPHY     |

| 6.3       | PREVENTIVE MAINTENANCE     |

| 6.4       | TEST EQUIPMENT REQUIRED 6- |

| 6.5       | CORRECTIVE MAINTENANCE     |

| 6.5.1     | Maintenance Modes          |

| 6.5.1.1   | System Test Mode           |

| 6.5.1.2   | Internal Loop Mode         |

| 6.5.1.3   | External Loop Mode 6-      |

|           |                            |

## APPENDIX A REPRESENTATIVE MODEM FACILITIES AVAILABLE

| APPENDIX B | ADDRESS | ASSIGNMENTS |

|------------|---------|-------------|

|------------|---------|-------------|

| B.1 | FLOATING VECTORS        | <br>        |                 | <br>B- | 1 |

|-----|-------------------------|-------------|-----------------|--------|---|

| B.2 | FLOATING DEVICE ADDRESS | <br>• • • • | • • • • • • • • | <br>B- | 1 |

APPENDIX C IC SCHEMATICS

## ILLUSTRATIONS

### Figure No.

## Title

Page

Page

| 1-1 | Asynchronous Technique Format                                      | -2 |

|-----|--------------------------------------------------------------------|----|

| 1-2 | Synchronous Format                                                 | -3 |

| 1-3 | Typical Communication System Using the DU11 Interface              | -6 |

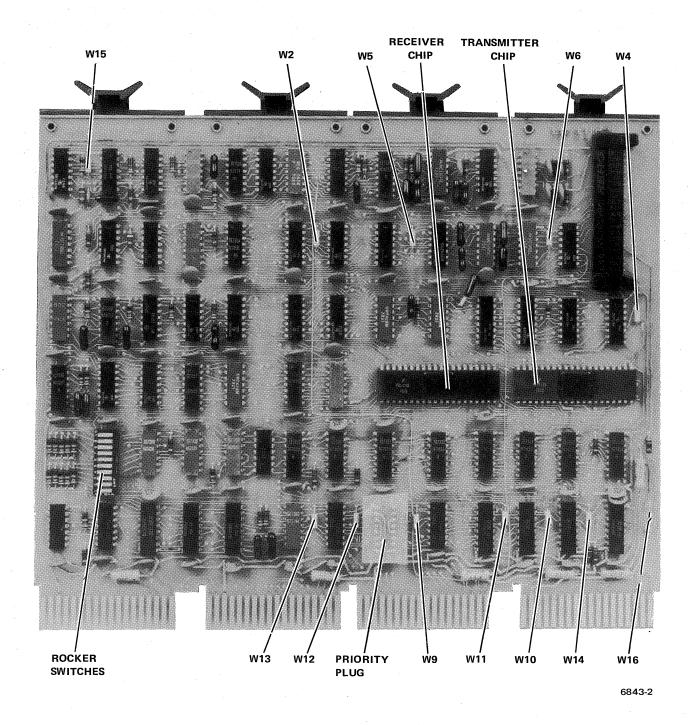

| 1-4 | DU11 Major Components                                              | -7 |

| 1-5 | Flip-Flop Signal Names 1                                           |    |

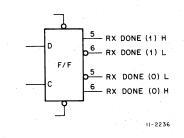

| 2-1 |                                                                    | -2 |

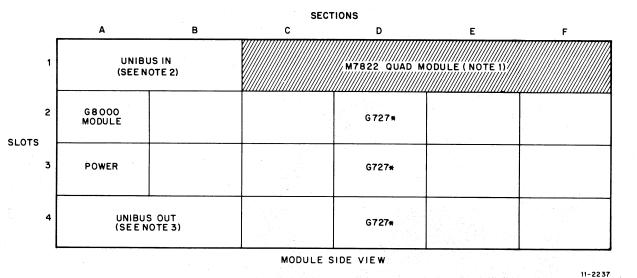

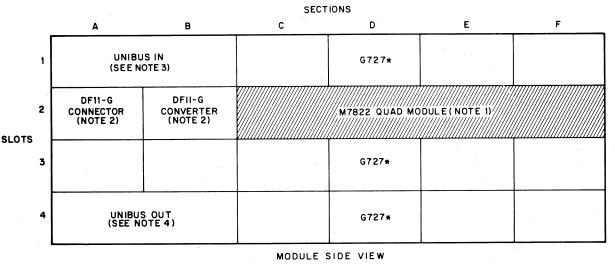

| 2-2 | DU11-DA (M7822 Module) Mounted in DD11-A                           | -3 |

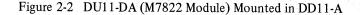

| 2-3 | DU11-DA (M7822 Module) Mounted in DD11-B                           | -3 |

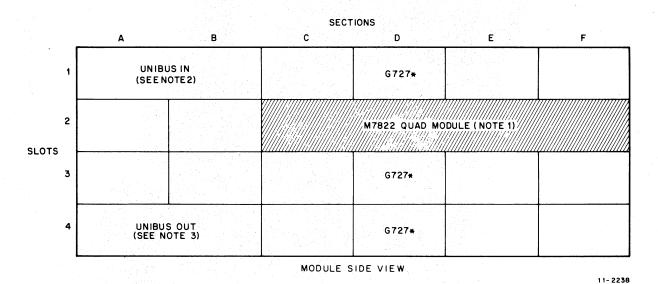

| 2-4 | Current Mode Configuration (DU11-EA) Using DD11-B Mounting Panel 2 | -4 |

| 2-5 | DU11-EA (M7822 Module and DF11-G Converter) Mounted in DD11-B      | -5 |

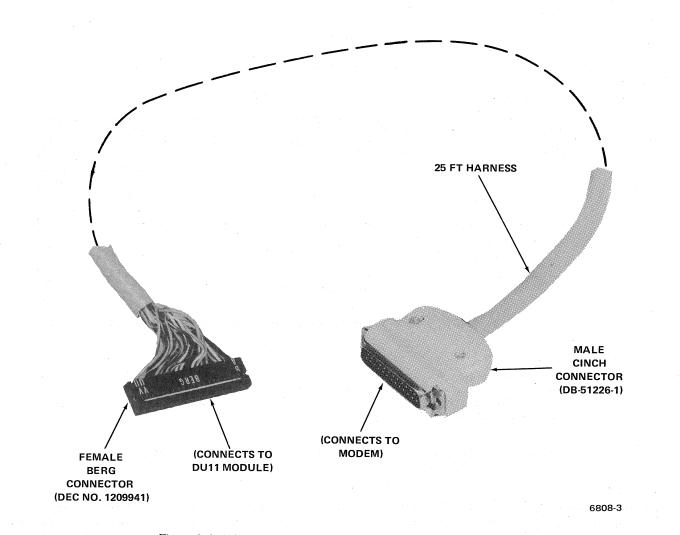

| 2-6 | BC05-25 Cable Harness Used to Connect DU11-DA to Bell 201 Modem    | -6 |

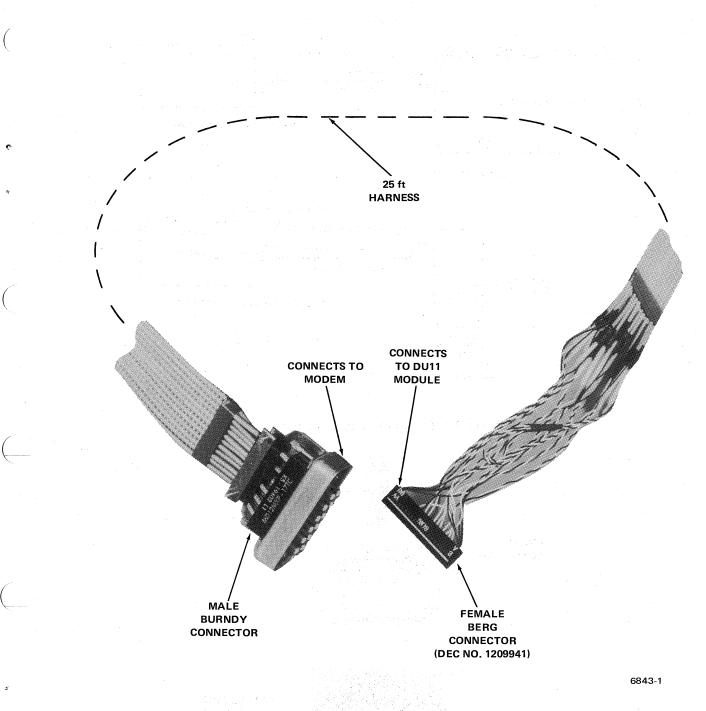

| 2-7 | BC02W-25 Cable Harness Used to Connect DU11-EA to Bell 303 Modem   | -7 |

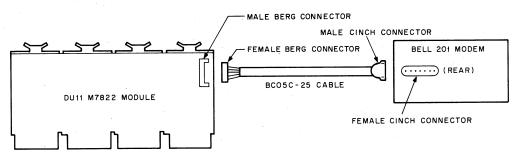

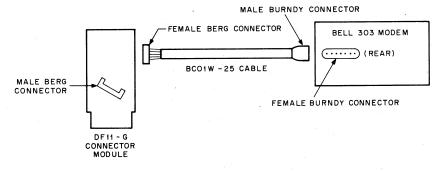

| 2-8 | DU11 to Modem Connection 2                                         | -8 |

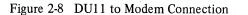

| 2-9 | Modem Test Connection Installation                                 | -8 |

| 3-1 | Receiver Status Register (RXCSR) 3                                 | -2 |

| 3-2 | Receiver Data Buffer (RXDBUF) 3                                    | -5 |

| 3-3 | Parameter Status Register (PARCSR)                                 | -6 |

| 3-4 |                                                                    | -7 |

| 3-5 | Transmitter Data Buffer (TXDBUF)                                   | -9 |

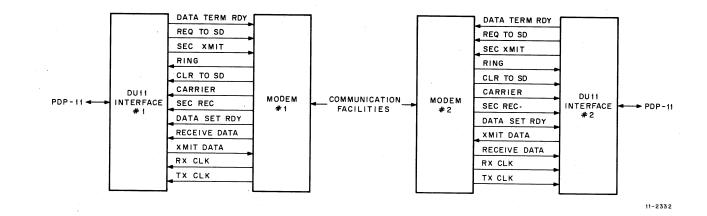

| 4-1 | DU11 to Modem Interface Diagram                                    | -3 |

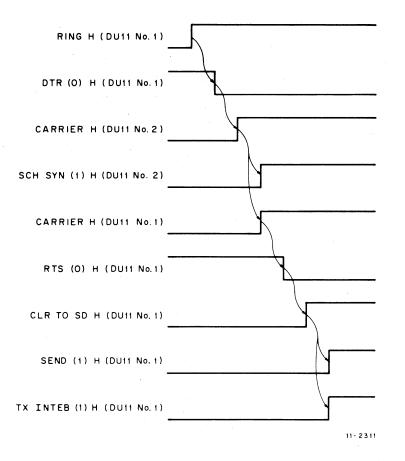

| 4-2 | Handshaking Sequence Timing Diagram                                | -3 |

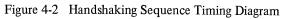

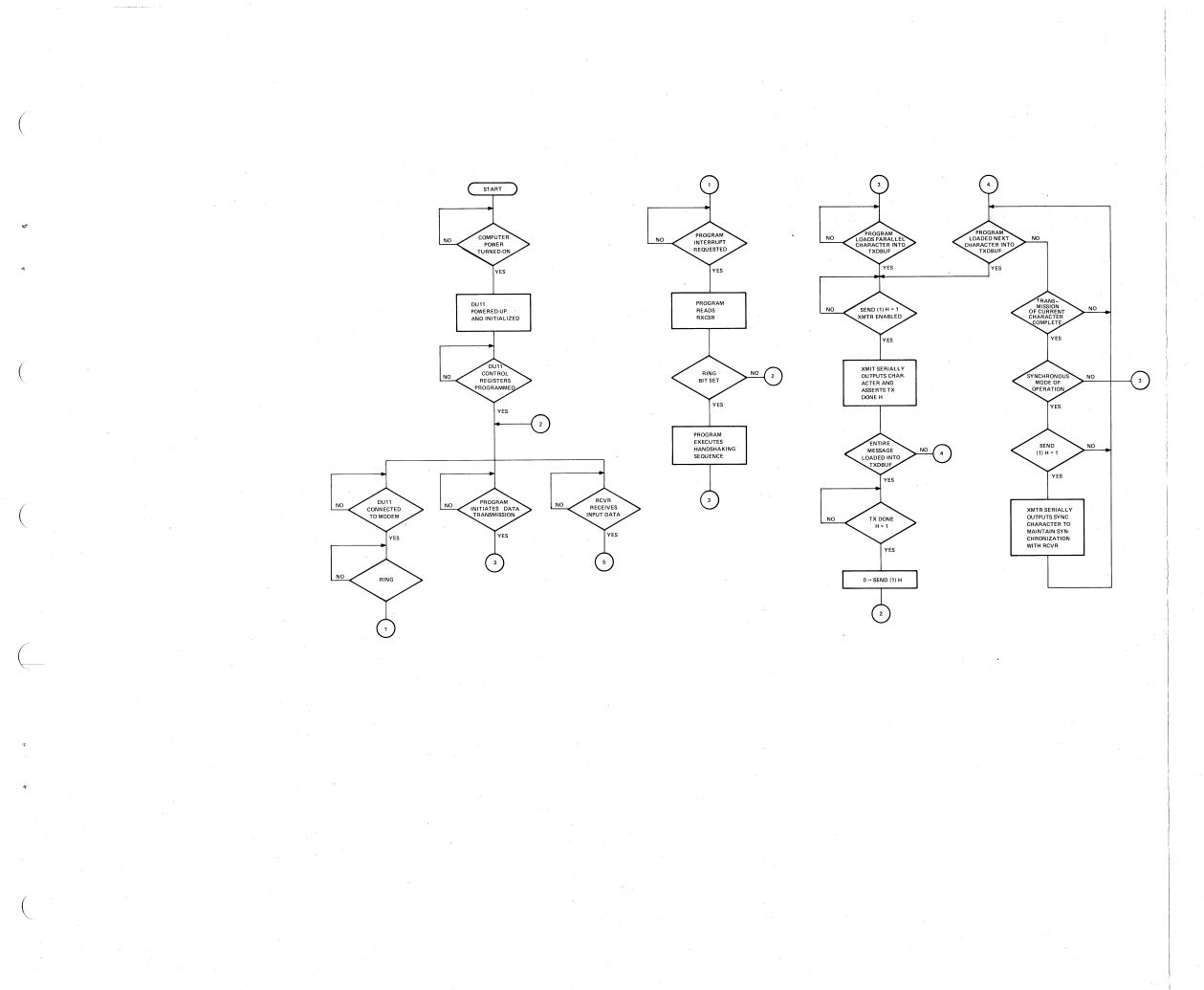

| 4-3 | Duble operation 1100 Diagram 1101 0100 1000                        | -5 |

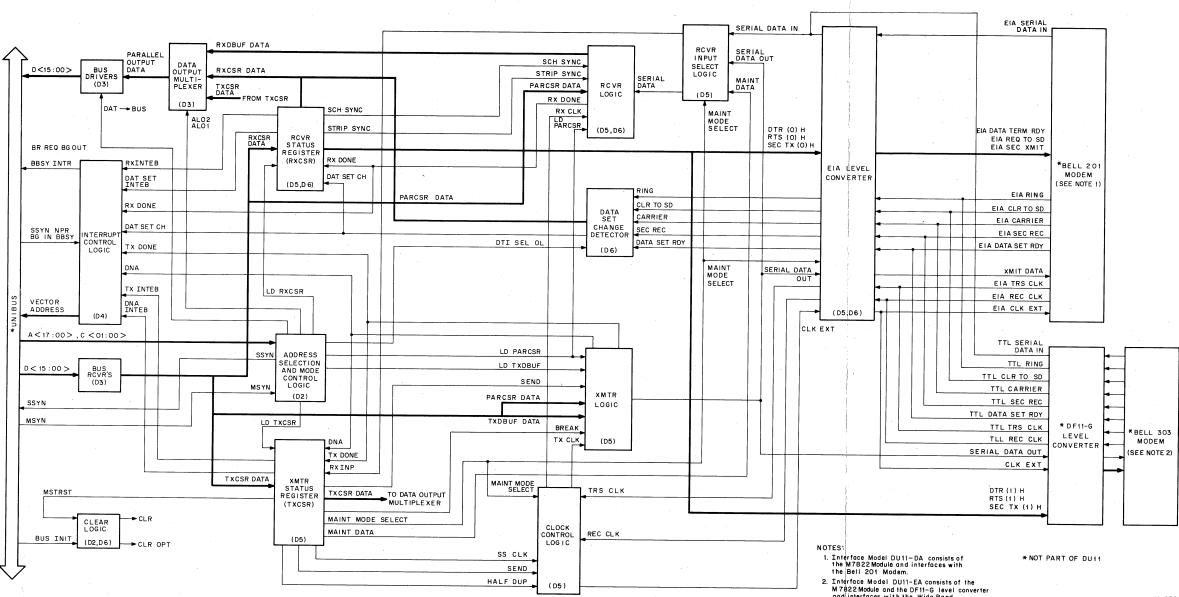

| 4-4 | DU11 Functional Block Diagram                                      | -9 |

## **ILLUSTRATIONS (Cont)**

| Figure No. | Title                                                          | Page |

|------------|----------------------------------------------------------------|------|

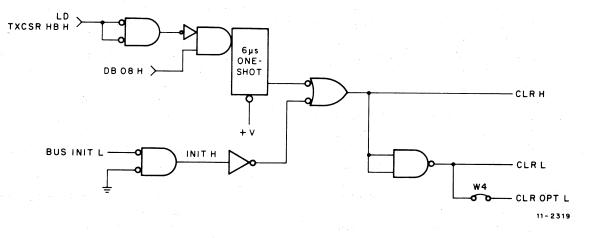

| 4-5        | Clear Logic                                                    | 4-14 |

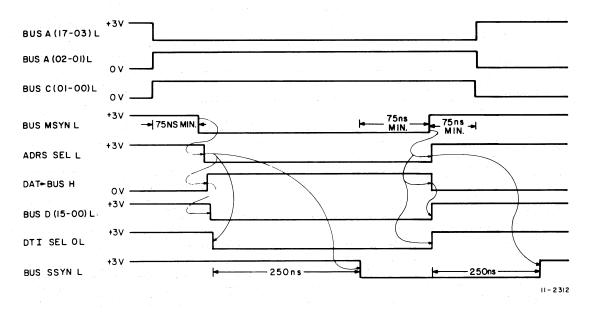

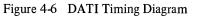

| 4-6        | DATI Timing Diagram                                            |      |

| 4-7        | DATOB Timing Diagram                                           |      |

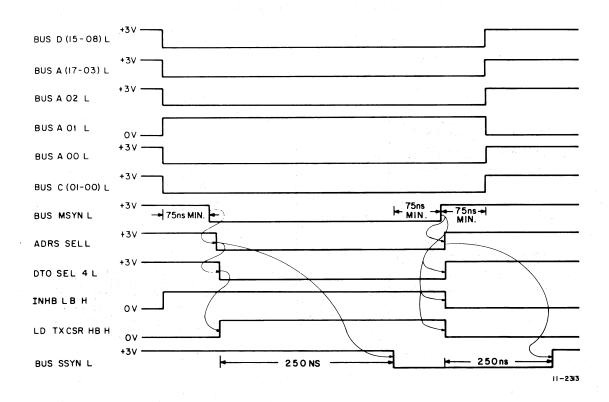

| 4-8        | DATO Timing Diagram                                            |      |

| 4-9        | Data Output Multiplexer Logic                                  |      |

| 4-10       | RCVR Input Select Logic                                        |      |

| 4-11       | External Loop Maintenance Mode Interconnection Diagram         | 4-20 |

| 4-12       | Clock Control Logic                                            |      |

| 4-13       | RCVR Logic                                                     |      |

| 4-14       | RCVR Internal Synchronous Mode Timing Diagram (Example I)      | 4-25 |

| 4-15       | RCVR Internal Synchronous Mode Timing Diagram (Example II)     |      |

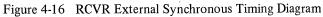

| 4-16       | RCVR External Synchronous Timing Diagram                       |      |

| 4-17       | RCVR Isochronous Mode Timing Diagram                           |      |

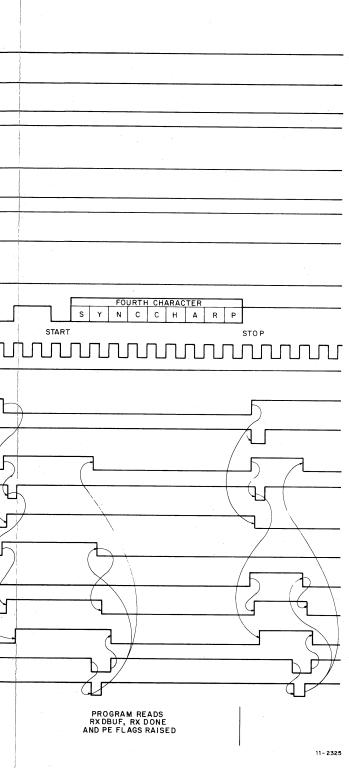

| 4-18       | XMTR Logic                                                     |      |

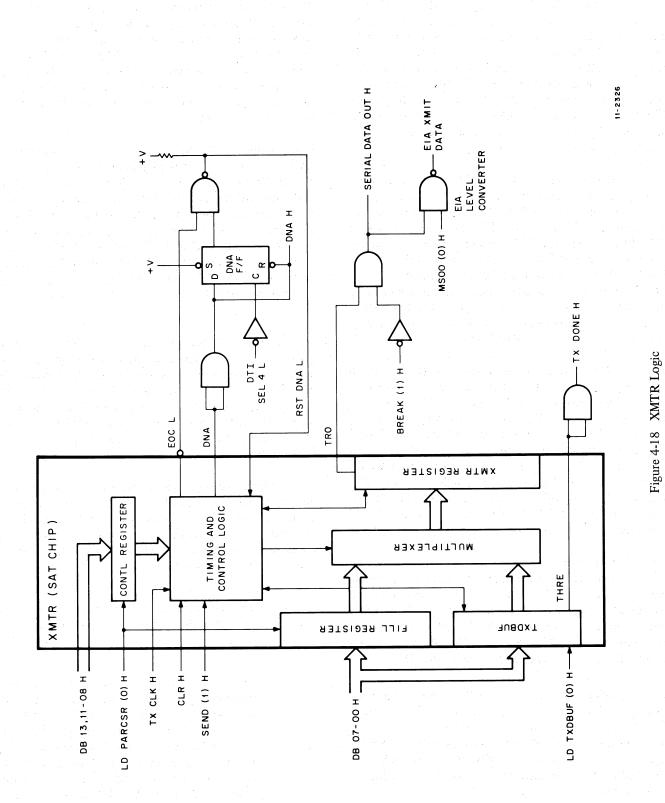

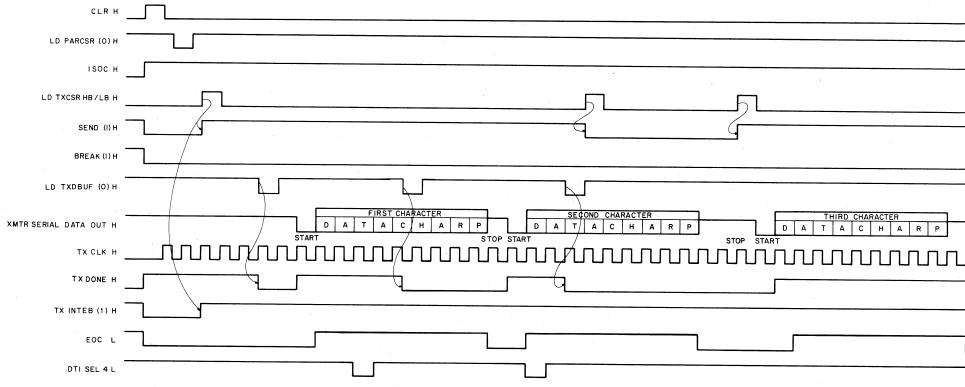

| 4-19       | XMTR Synchronous Mode Timing Diagram                           |      |

| 4-20       | XMTR Isochronous Mode Timing Diagram                           |      |

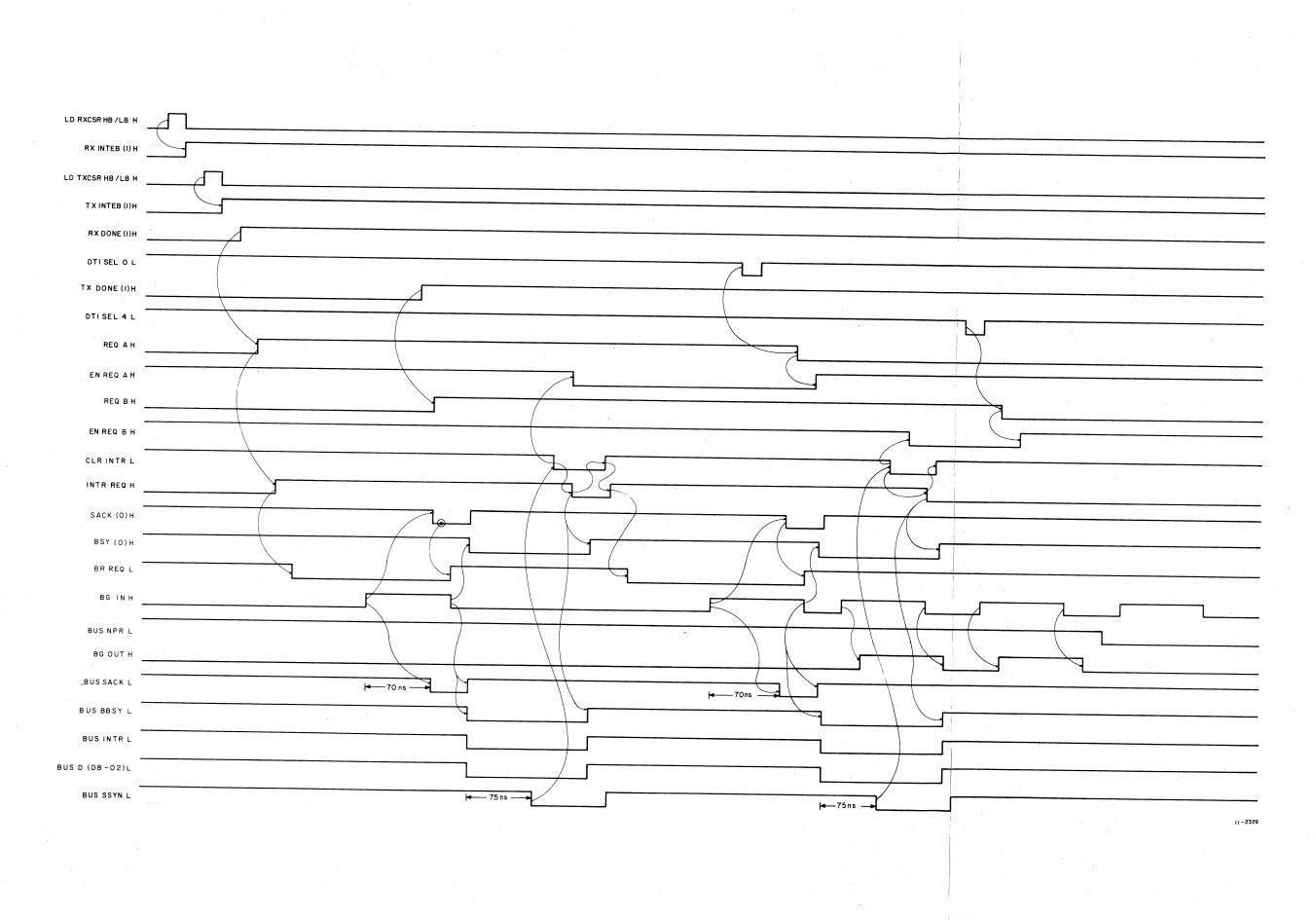

| 4-21       | Interrupt Control Logic Timing Diagram                         |      |

| 6-1        | DU11 Maintenance Diagram                                       |      |

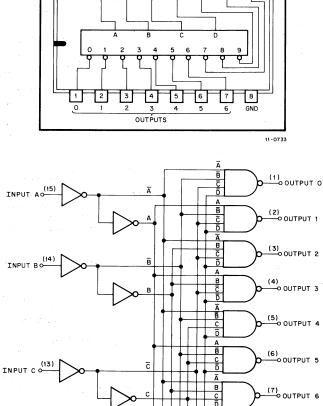

| C-1        | 7442 Package and Logic Diagrams                                |      |

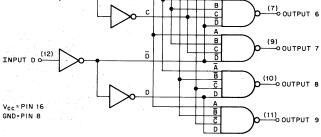

| C-2        | DEC 74123 IC Illustrations                                     |      |

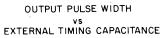

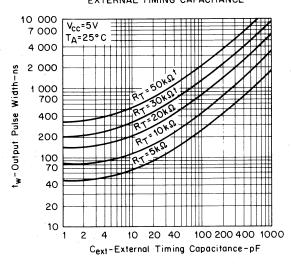

| C-3        | DEC 74123 IC Output Pulse Width vs External Timing Capacitance |      |

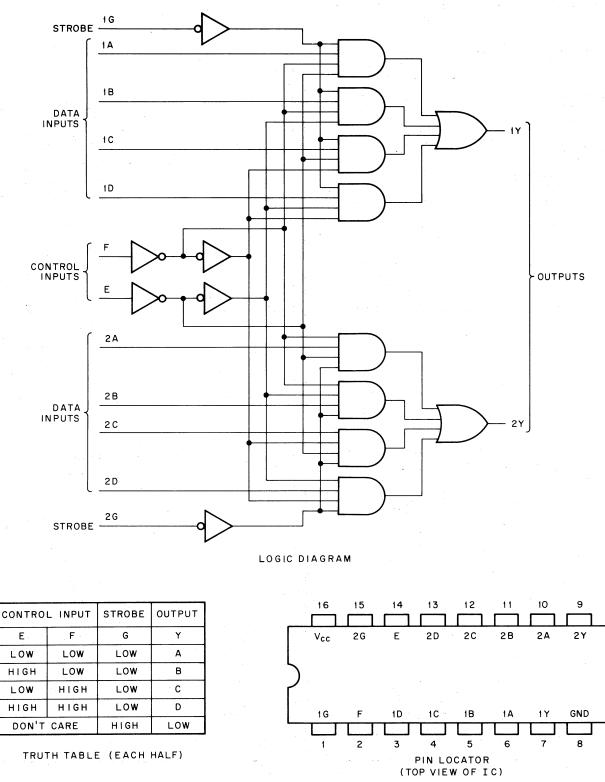

| C-4        | 74153 Package and Logic Diagram                                |      |

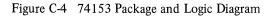

| C-5        | 74174 Logic Diagram                                            |      |

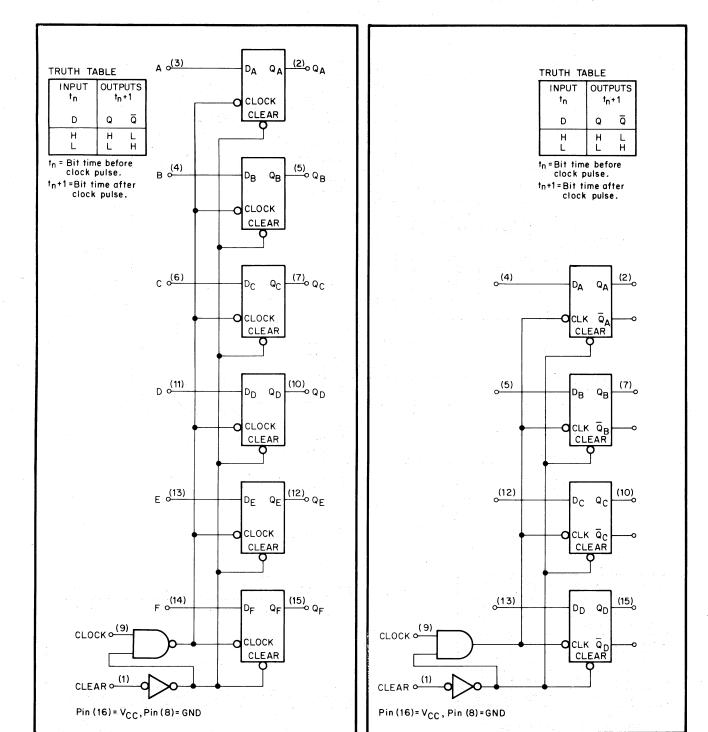

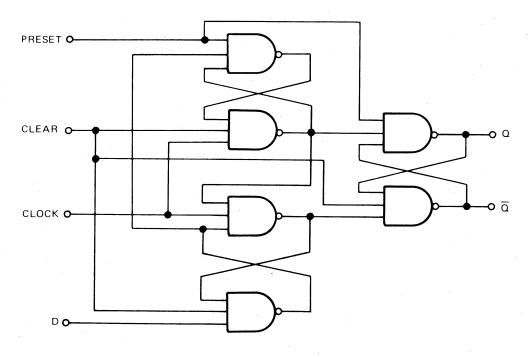

| C-6        | 74175 Logic Diagram                                            |      |

| C-7        | 74H74 Logic Diagram                                            |      |

## TABLES

## Table No.

## Title

Page

| Representative Message Codes                      |

|---------------------------------------------------|

| Computer Communications Applications 1-5          |

| Jumper Assignments                                |

| DU11 Register Address Assignments 3-1             |

| Receiver Status Register Bit Description          |

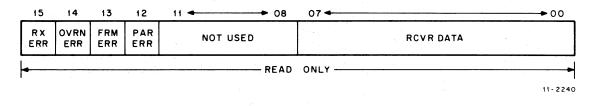

| Receiver Data Buffer Bit Description 3-5          |

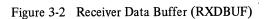

| Parameter Status Register Bit Description         |

| Transmitter Status Register Bit Description 3-7   |

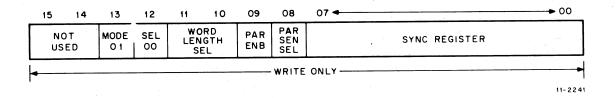

| Transmitter Data Buffer Bit Description           |

| Bus Address Register Select Bit Configurations    |

| Bus Operation Control Bit Configurations          |

| Maintenance Mode to Data Source Relationship 4-19 |

| PARCSR Mode Select Bit Configurations             |

| Test Equipment Required                           |

| Priority Ranking for Floating Vectors             |

| (starting at 300 and proceeding upwards) B-1      |

| Floating Address Sequence B-2                     |

| Floating Device Address Assignments B-2           |

|                                                   |

## DU11 SINGLE LINE PROGRAMMABLE SYNCHRONOUS INTERFACE MAINTENANCE MANUAL

6731-1

DU11 Programmable Synchronous Interface

#### 1.1 SCOPE

This manual provides a complete description of the DU11 Line Interface including installation, theory of operation, programming, and maintenance. The level of discussion assumes that the reader is familiar with basic digital computer theory.

This chapter contains introductory information. It includes a description of data communication techniques and systems, a general description of the DU11, a physical description of the DU11, DU11 specifications, and an explanation of engineering drawing conventions.

## 1.2 DATA COMMUNICATION TECHNIQUES AND SYSTEMS

#### **1.2.1** Data Communication Techniques

There are several techniques used for the transfer of data communication signals. Each has its particular advantages and disadvantages.

1.2.1.1 Pulse Coding – Standard data communication messages are sent in some form of pulse code. There are several varieties of pulsed codes used in the transferral of data in digital form. Binary signals, by their very nature, are natural elements for digital data codes. Such codes are said to be in "binary format."

A formatted binary code can represent different symbols only by allowing sufficient binary elements for each symbol. If we think of one binary digit (or "bit") representing each symbol, we have only two choices: one symbol represented by the "on" state, the other represented by the "off" state. With such an arrangement, we could let the "on" or one state represent "no" and the "off" or zero state represent "yes." While it would be difficult with such an arrangement, we could convey messages of a very limited nature from a remote station (such as the answer to "Is the temperature at your station over 70° F?").

## CHAPTER 1 INTRODUCTION

If, instead of using one binary digit for our character, we use two, we have more characters to choose from. Our choice for a one-bit code was limited to two: 0 or 1. Our choice for a two-bit code is four: 00, 01, 010, or 11. If we choose a three-bit code, our choice is eight: 000, 001, 010, 011, 100, 101, 110, and 111. It can be shown that for a code with a character makeup of n bits, the number of characters available will be  $2^n$ . In communications parlance, instead of calling these codes one-bit codes, two-bit codes, etc. Although any arbitrary meaning can be assigned to a code character, it is more practical for the majority of operations to let the characters of the alphabet. In addition to these, some special codes use characters for other meanings.

**1.2.1.2** Pulse Code Transmission – In order to transmit code characters, it is necessary to arrange their elements in a way that will allow their reception without uncertainty. There are several techniques by which this may be done; these techniques fall into two broad categories: serial data transmission and parallel data transmission.

Because the DU11 is a serial communication interface, only serial data transmission techniques will be discussed.

There are two basic techniques of serial data transmission: asynchronous and synchronous. These two techniques as well as a third, isochronous, will be discussed in the following paragraphs.

1.2.1.2.1 Asynchronous Serial Transmission – This technique enables data to be transferred as it becomes available. This is possible by framing each data character with a begin signal (START bit) and an end signal (STOP bit), so that the equipment receiving the data (the interface receiver) knows when a data character is being presented on the communication line and when the line is inactive.

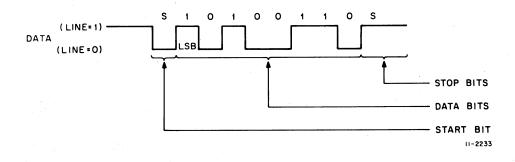

Figure 1-1 Asynchronous Technique Format

Hence, each character consists of three parts: a START bit, the data bits, and a STOP bit (Figure 1-1). A START bit is a line state (usually a zero) that lasts for 1 bit time. The data bits represent the actual binary character being transferred. In many applications the characters are 8 bits long with the least significant bit being sent out and received first. A STOP bit is a line state (usually a one) that lasts for 1, 1.42, or 2 bit times; it indicates that character transmission is complete. The STOP bit enables the interface receiver to check synchronization after each character transmission. If the STOP bit is not received properly, i.e., it is not presented on the line immediately after the last data bit, the character received is considered erroneous and re-transmission is necessary.

Clocking for the interface transmitter and interface receiver during asynchronous transmission is provided by two different sources that are asynchronous to one another. The transmitter clock is enabled when data is available for transmission and clocks the character onto the line. The receiver clock is enabled when a START bit is detected on the line and samples the data bits as they are presented on the line. The receiver is also equipped with a counter that counts the character bits received. When a complete character and a STOP bit are received (the receiver must know the number of bits per character), the receiver clock is disabled until the next START bit is detected.

The asynchronous serial data transmission technique has the following advantages:

- a. Can be generated easily by electromechanical equipment (e.g., Teletype<sup>®</sup> keyboard).

- b. Can be used easily to drive mechanical equipment (e.g., Teletype printer).

- c. Characters can be sent asynchronously (as they become available) because each character has its own synchronizing information.

The disadvantages of the asynchronous serial data transmission technique are:

a. Separate timing required for both transmitter and receiver.

b. Distortion sensitive because the receiver depends on incoming signal sequences to become synchronized. Any distortion in these sequences will affect the reliability with which the character is assembled.

- c. Speed limited because a reasonable amount of margin between characters must be built in to accommodate distortion.

- d. Inefficient because at least 10 bit times are required to send 8 bits of data. If a 2 bit time STOP bit is used, it takes 11 bit times to transfer 8 bits of data.

1.2.1.2.2 Synchronous Serial Transmission – This technique does not use START and STOP bits to accomplish synchronization. Instead, the entire block of data (message) is preceded on the line by a synchronizing code. When the interface receiver recognizes this code (henceforth referred to as sync characters), it locks in and, using a counter, assembles the data characters which follow. Hence, as in the asynchronous technique, the receiver must know the number of bits per character.

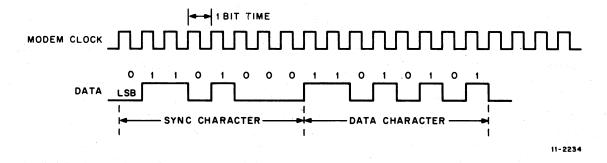

This technique requires that the clocking for the interface transmitter and interface receiver be provided by a common clock source. The clock signal is provided to the transmitter and receiver on lines separate from the data line. At the transmitter, the clock signal serves to clock the data onto the line. At the receiver, the clock signal gates the data in. Figure 1-2 illustrates the timing for a synchronous communication system using modems.

$<sup>^{\</sup>textcircled{R}}$ Teletype is a registered trademark of Teletype Corporation.

Figure 1-2 Synchronous Format

As shown in Figure 1-2, the modem provides the clock, the transmitter presents the data to the line on the positive going edge of the clock and the receiver samples the data on the negative going edge. If the transmitter pauses at any time and fails to inhibit the clock, the receiver will continue to sample the line, synchronization is lost and the remainder of the message will be erroneous.

The advantages of the synchronous serial data transmission technique are:

- a. Modem timing sources can be used for both transmitter and receiver.

- b. Interface receiver does not require clocksynchronizing logic as the asynchronous technique does.

- c. Highly efficient because there are no bit times wasted with the use of START and STOP bits. All bits on the line are data, with the exception of the sync characters at the beginning of the bit stream.

- d. Low distortion sensitivity because the timing is provided along with the data.

- e. Higher speeds are achievable because of the low distortion sensitivity.

The disadvantages of the synchronous serial data transmission technique are:

- a. Characters must be sent synchronously, not asynchronously (asynchronous transmission is desirable for most real time and mechanical applications).

- b. One bit time added to or missing from the data-bit stream can cause the entire message to be faulty.

- c. The common-carrier equipment required to accommodate this mode of operation is more expensive than the equipment required for asynchronous modes of operation.

- d. Mechanical equipment cannot transmit or receive this format directly.

**1.2.1.2.3 Isochronous Serial Transmission** – This technique is essentially the transmission of asynchronous data over a synchronous modem. Character synchronization is achieved via START and STOP bits; a common timing source is used for both the transmitter and receiver.

The isochronous technique does have advantages over the asynchronous technique. Clocking for isochronous operations emanates from the modems and is synchronous to the data; hence, the receiver does not require clocksynchronizing logic and distortion sensitivity is low making higher speeds possible.

#### **1.2.2 Data Communication Systems**

1.2.2.1 Synchronous Systems – Synchronous modulatordemodulators (modems) have permitted a higher rate of data transmission than asynchronous modems over a voice grade facility. The nature of these transmission techniques has also resulted in higher efficiency by eliminating the need for synchronizing information with every character.

The logic design of interfaces to a synchronous modem is considerably easier than the design of an asynchronous interface because there is no need for bit synchronization and sampling hardware. Most synchronous modems supply all the timing necessary to receive each bit as it is made available from the modem. The difficulty in designing a synchronous modem interface is to design the capability of communicating in the message formats used in synchronous communications.

| Character | Meaning                     | Function                                          |

|-----------|-----------------------------|---------------------------------------------------|

| SYN       | Synchronizing signal        | Establish character framing                       |

| SOH       | Start of heading signal     | Precedes block message heading characters         |

| STX       | Start of text signal        | Precedes block of text characters                 |

| ETX       | End of text signal          | Terminates a block of characters started with STX |

| ACK       | Acknowledge signal          | *Affirmative acknowledgment of message received   |

| NAK       | Negative acknowledge signal | *Negative acknowledgment of message received      |

Table 1-1Representative Message Codes

\*ACK and NAK are sent by the station that received the message to the station that originated the message.

It is not the purpose of this manual to discuss the format for synchronous communication in detail. However, a brief description of these formats is outlined below to facilitate the reader's understanding of synchronous interface design.

Because the synchronous transmission technique provides only bit recovery timing, there must be a way to establish character framing and message framing. This is accomplished by using codes (usually ASCII) that are assigned for synchronous message formatting purposes. Representative message codes are listed in Table 1-1.

A typical message that might be sent between two devices (a terminal and a processor) follows.

| Terminal To Processor |

|-----------------------|

| SYN                   |

| SYN                   |

| SYN                   |

| SOH                   |

| an an 🚽 🚽 🖓 👘         |

| User Terminal         |

| N4                    |

| STX                   |

|                       |

| Req. Balance          |

| of Account            |

| No. 14325             |

| l                     |

| ETX                   |

| LRC (check character) |

|                       |

| at e sur a d <mark>e la companya d</mark> e la companya de la company |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Idle Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| te 🔶 🚽                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Processor To Terminal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ł                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SYN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SYN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SYN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ACK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SYN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SYN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SYN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SOH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <b>.</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| To Terminal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| No. 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| STX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Balance is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| \$100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| l<br>ETX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| LRC (check character)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Idle Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Terminal To Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SYN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SYN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SYN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ACK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| J                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Idle Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| a da 🔶 da serie da s                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

1.2.2.2 Computer Application – Electronic computers are often connected into communication systems to help transmit and process digital data. By using computer systems to concentrate data from many low-speed terminals over one voice grade facility, significant improvements can be made in the efficiency of a data communication system. Since most long-range communication systems are connected through common carrier facilities, a communication system using a computer should be interfaced to the correct type facility. There are two basic types of common carrier facilities to which computers must be interfaced: asynchronous serial and synchronous serial. We have already pointed out the advantages and disadvantages of these two types of facilities. Based on these advantages and disadvantages, Table 1-2 shows typical speeds and applications of these two techniques.

As shown in Table 1-2, there are three basic communication applications to be solved by the computer communications engineer:

Low speed terminal equipment, such as Teletypes. Medium speed terminal equipment. Intercomputer communications.

#### **1.3 GENERAL DESCRIPTION**

The DU11 interface is a single line, program controlled, double-buffered communication interface. It provides serial to parallel and parallel to serial data conversion, EIA\* to TTL (transistor-transistor logic) and TTL to EIA voltage level conversion and modem control for full or half duplex communication systems.

The DU11 is compatible with all PDP-11 family computers and is available in two models. Model DU11-DA is the basic

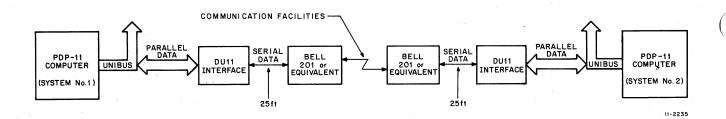

version and is completely contained on the M7822 module. The basic version is compatible with the Bell 201 synchronous modem or equivalent. Model DU11-EA is simply the basic version adapted to current mode operation. The DU11-EA version consists of the basic M7822 module plus the DF11-G current mode converter. The DU11-EA is compatible with the Bell 303, wide band, synchronous modem or equivalent. A typical communication system using the DU11 is shown in Figure 1-3.

Interface operation is completely program controlled. The mode of operation (synchronous or isochronous), character length (5, 6, 7, or 8 bits plus parity if selected), parity enable and sense (odd or even), sync character configuration, and duplex mode (full or half) are all selected via the program.

#### 1.4 PHYSICAL DESCRIPTION

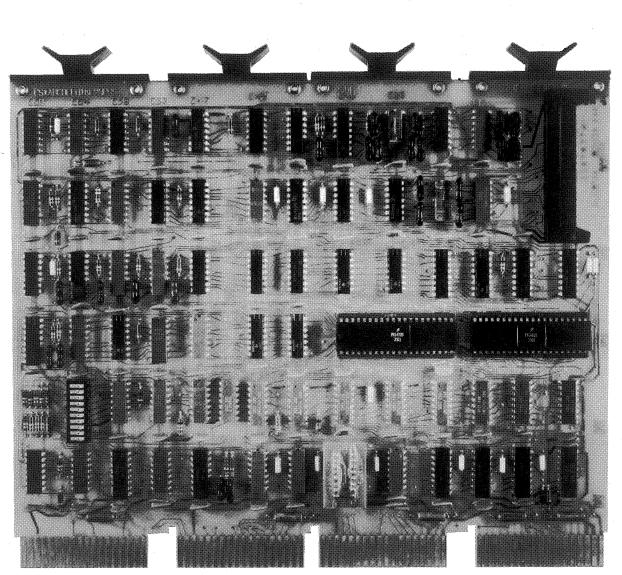

The DU11 interface is completely contained on a single M7822 Quad Integrated Circuit module (Figure 1-4). This module can be mounted easily in the PDP-11 processor small peripheral controller slot (exceptions noted in Chapter 2) or in one of four slots in a DD11-A or DD11-B peripheral mounting panel.

All DU11 operating power is provided by the mounting panel in which it is installed. The power is taken from the mounting box power supply. For proper operation, the module requires +5 V @ 2.2 A, -15 V @ 0.17 A, and +15 V @ 0.07 A.

The mounting panel also connects the DU11 to the Unibus. All Unibus input/output signals enter and leave the module via the mounting panel pins. Refer to Chapter 2 for Unibus to mounting panel connection.

| Speed                      | Asynchronous                                                                                       | Synchronous                                                                                       |

|----------------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| Low<br>0 to 300 baud       | Electromechanical terminals such as keyboard printers and Teletypes.                               | Operations tend to be asynchronous at these speeds.                                               |

| Medium<br>300 to 3000 baud | Unbuffered terminals such as paper<br>tape readers and punches, card readers<br>and line printers. | Buffered terminals such as displays<br>buffered card readers, and line printer<br>configurations. |

| High<br>5000 baud and up   | Not frequently used.                                                                               | Intercomputer communications.                                                                     |

Table 1-2

Computer Communications Applications

\*EIA – A standardized set of signal characteristics (time duration, voltage, and current) specified by the Electronic Industries Association.

Figure 1-3 Typical Communication System Using the DU11 Interface

Major DU11 components are also labeled on Figure 1-4: the rocker switches which are used to select the interface Unibus address, the priority plug which determines the bus request (BR) priority level of the interface (BR5 plug normally installed at factory), the SAR (receiver) and SAT (transmitter) chips, and jumpers W2, W4-W6, and W9-W16 (a complete description of the jumpers is provided in Paragraph 2.1.4).

#### **1.5 SPECIFICATIONS**

Environmental, electrical, and performance specifications for the DU11 are contained in the following paragraphs.

#### 1.5.1 Environmental

Ambient temperature  $10^{\circ}$  to  $50^{\circ}$  C ( $50^{\circ}$  to  $122^{\circ}$  F)

#### Relative humidity

20% to 95% (without condensation)

#### 1.5.2 Electrical

DC voltage requirements

+5 V @ 2.2 A

- 15 V @ 0.17 A

+15 V @ 0.07 A

#### **Electrical Characteristics**

Electrical characteristics of this interface meet EIA standard RS-232C and PDP-11 Unibus Interface specifications.

#### 1.5.3 Performance

The following paragraphs discuss the baud rate limitations of the DU11 and related program response time.

1.5.3.1 Baud Rates for Synchronous Communications – EIA/CCITT\* baud rate (10K baud maximum) is limited by modem and data set interface level converters. Current mode operation (100K baud maximum) is possible only with the DU11-EA. Current mode speed is limited by DU11 logic.

Even though the DU11 can receive and transmit information at such a high rate, it may, in most cases, be impractical. Since the service of the data buffers relies solely on the program, little time if any would be left for other events. This problem would be compounded if the interface were operating in full duplex mode.

1.5.3.2 Baud Rates for Isochronous Communications – EIA/CCITT baud rate (10K baud maximum) is limited by data set interface level converters. Current mode operation baud rate (100K baud maximum) is limited by DU11 logic.

#### **1.6 ENGINEERING DRAWINGS**

A complete set of engineering drawings entitled DU11 Line Interface, Engineering Drawings is provided with each interface. The general logic symbols used on these drawings are described in the *DEC Logic Handbook*, 1972. Specific symbols and conventions are also included in the PDP-11 system manuals. The following paragraphs describe the signal nomenclature conventions used in the drawing set.

#### 1.6.1 Basic Signal Names

Signal names in the DU11 print set are in the following basic form:

#### SOURCE SIGNAL NAME POLARITY

SOURCE indicates the drawing number of the print from which the signal originates. The drawing number of a print is located in the lower right-hand corner of the print title block (D1, D2, D3, D4, D5, and D6).

<sup>\*</sup>CCITT – The Consultive Committee International Telegraph and Telephone is an advisory committee established under the United Nations to recommend worldwide standards.

SIGNAL NAME is the proper name of the signal. The names used on the print set are also used in this manual for correlation between the two.

**POLARITY** is either H or L to indicate the voltage level of the signal: H means +3 V; L means ground.

For example, the signal

#### D5- TX DONE H

originates on sheet 5 of the engineering drawings and is read, "When TX DONE is true, this signal is at +3 V."

Unibus signal lines do not carry a SOURCE indicator. These signal names represent a bidirectional wire-ORed bus; as a result, multiple sources for a particular bus signal exist. Each Unibus signal name is prefixed with the word BUS.

Interface signals fed to or received from the Bell 201 modem via the Berg connector on the M7822 module are preceded by the jack and pin number in parentheses:

(J1-DD) EIA DATA TERM RDY (This signal is shown on engineering drawing D6.)

Interface signals fed to or received from the Bell 303 modem via the mounting panel backpanel wiring and DF11-G level converter are preceded by the M7822 module pin number:

#### AF1 D6-DTR (1) H

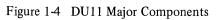

#### 1.6.2 Flip-Flop Signal Names

Flip-flop signal names add an extra dimension. Although flip-flops have only two outputs, four signal names are possible (Figure 1-5). The two real outputs are RX DONE (1) H on pin 5 and RX DONE (0) H on pin 6. The two additional outputs are simply the real outputs reidentified. RX DONE (1) L is electrically the same as RX DONE (0) H, and RX DONE (0) L is electrically the same as RX DONE (1) H.

## CHAPTER 2 INSTALLATION

#### 2.1 INSTALLATION

**2.1.1 Mounting the DU11 in the Computer** There are two DU11 installation configurations:

- a. The standard configuration, in which the DU11-DA interfaces with the Bell 201 synchronous modem or equivalent.

- b. The current mode configuration, in which the DU11-EA interfaces with the Bell wide band 303 modem or equivalent.

2.1.1.1 Standard Configuration – In this configuration, the DU11-DA can be mounted in the small peripheral controller slot in the PDP-11/05, 10, 35, 40, 45, and 50 processors or in any one of four slots in the DD11-A or DD11-B peripheral mounting panels (Figure 2-1). The DD11-A mounting panel (Figure 2-2) is used in the PDP-11/15 and 20 computers, while the DD11-B (Figure 2-3) is used in the PDP-11/05, 10, 35, 40, 45, and 50 computers.

#### NOTE

# The DU11-DA cannot be mounted in the small peripheral controller slot in the PDP-11/15 and 20 processors.

DD11-A and DD11-B mounting requirements are somewhat different. When using the DD11-B mounting panel, the DU11 is simply installed in the mounting panel; however, when using the DD11-A, jumper W16 (engineering drawing D1) and module G8000 must also be installed. Jumper W16 bypasses a voltage dropping resistor and the G8000 module converts the full-wave rectified +8 V/rms mounting panel input signal to a positive dc voltage which is used to drive the EIA level converters. To install the G8000 module, proceed as follows:

- 1. Install the G8000 module in slot A02 of the DD11-A.

- 2. Connect a wire between A03V2 and A02V2.

3. Connect a wire between A02N2 and CXXU1, where XX is to slot location of the M7822 module.

#### NOTE

Jumper W16 must not be installed if the DU11 is being installed in the DD11-B mounting panel.

2.1.1.2 Current Mode Configuration – In this configuration, the DU11-EA must be installed in the DD11-B mounting panel as shown in Figures 2-4 and 2-5.

#### NOTE

The DD11-A mounting panel cannot be used in the current mode configuration because it will not accommodate the DF11-G level converter.

#### 2.1.2 Installing the Modem Cable Harness

A different cable is required to connect the DU11 to the Bell 201 modem than to the Bell 303 modem. The BC05C-25 cable harness (Figure 2-6) is used for the DU11-DA configuration; the BC01W-25 cable harness (Figure 2-7) is used for the DU11-EA configuration.

To install the cables, refer to Figure 2-8 and proceed as follows:

- 1. Position the Berg connector such that the connector name and pin number markings are visible and mate it fully and squarely with the Berg connector on the DU11 module (DU11-DA configuration) or the DF11-G connector module (DU11-EA configuration).

- 2. Align the Cinch connector (DU11-DA configuration) or the Burndy connector (DU11-EA configuration) to the receptacle located on the rear of the modem.

- 3. Mate the connector and tighten the two holddown screws using a screwdriver.

2-2

\*GRANT Continuity Module (G727) must be installed in each slot that does not receive an interface logic module.

NOTES:

1. Can be mounted in slots 1, 2, 3, or 4

2. Can be M920 or BC11-A

3. Can be M920, BC11-A or M930

\*Grant Continuity Module (G727) must be installed in each slot that does not receive an interface logic module.

NOTES:

1. Can be mounted in slots 1, 2, 3, or 4

2. Can be M920 or BC11-A

3. Can be M920, BC11-A or M930

#### Figure 2-3 DU11-DA (M7822 Module) Mounted in DD11-B

C

11-2239

\*Grant Continuity Module (G727) must be installed in each slot that does not receive an interface logic module.

NOTES:

- 1. Can only be mounted in slots 2 or 3

- 2. The DF11-G connector and converter must be mounted in the same slot as the M7822 module.

- 3. Can be M920 or BC11-A

- 4. Can be M920, BC11-A or M930

Figure 2-5 DU11-EA (M7822 Module and DF11-G Converter) Mounted in DD11-B

**2.1.3 Unibus and Interrupt Vector Address Assignments** The Unibus and interrupt vector addresses must be determined prior to operating the DU11. The Unibus address is switch selectable; the interrupt vector addresses are jumper selectable (Figure 1-4 for physical location).

The Unibus address (also referred to as the device address) is controlled by ten rocker switches located in the address selection and mode control logic. The position of these switches determines the required address state (0 or 1) of bus address bits 12–03. If a rocker switch is set to ON, the switch contacts are closed and an address state of 0 is required on the related address bit to address the DU11. Hence, electrically the DU11 can have any device address within the range of 760000 to 777777; however, Digital Equipment Corporation software requires that the device address fall within the floating address range of 760010 to 763776. Refer to Appendix B for a complete discussion of DU11 address assignments.

#### NOTE

If a device address is selected which falls outside the floating address range, the software must be modified accordingly. The interrupt vector addresses are also floating and are established at the factory in accordance with the vector addressing scheme described in Appendix B. If it is necessary to change the vector address, simply change jumpers W9–W14 as required. Jumpers are cut to obtain a logical zero. Jumpers W9–W14 are located in the interrupt control logic (engineering drawing D4). These jumpers control vector address bits 08-03; hence, vector addresses can be generated within the range of 000 to 774; however, software requires that the vector address fall within the floating address range of 300 to 777.

#### NOTE

If a vector address is selected which falls outside the floating address range, the software must be modified accordingly.

#### 2:1.4 Jumper Assignments

Jumpers are used at various points in the DU11 circuitry to increase flexibility and to meet the floating vector address requirement described in Appendix B. For a complete description of the DU11 jumpers, refer to Table 2-1.

Figure 2-6 BC05C-25 Cable Harness Used to Connect DU11-DA to Bell 201 Modem

#### 2.1.5 Priority Assignment

The priority level is determined by the priority plug located on the DU11 module. The DU11 normally has a priority level of BR5. However, the priority may be changed by simply replacing the BR5 plug with a plug wired for a different priority level.

#### NOTE

If the priority level is changed, the software must be modified accordingly.

#### 2.2 INITIAL TESTING

The DU11 must be tested prior to placing the unit into operation. For initial test procedures, refer to the engineering specification, A-SP-DU11-0-4, which is provided with each DU11 delivered.

#### NOTE

Before running diagnostics on interface model DU11-DA, disconnect the modem cable (BC05C-25) from the rear of the modem and install the modem test connector as shown in Figure 2-9.

Figure 2-7 BC01W-25 Cable Harness Used to Connect DU11-EA to Bell 303 Modem

2-7

b. DU11-EA CONFIGURATION

11-2333

Figure 2-9 Modem Test Connection Installation

| Jumper No. and Location             | Normal Configuration | Fu                                                     | inction                        |  |  |  |  |

|-------------------------------------|----------------------|--------------------------------------------------------|--------------------------------|--|--|--|--|

| W2/D5                               | Removed              | This jumper may be installed to enable the receiver to |                                |  |  |  |  |

|                                     |                      |                                                        | pon receiving just one synd    |  |  |  |  |

|                                     |                      |                                                        | ng the normal requirement of   |  |  |  |  |

|                                     |                      |                                                        | s sync characters to achieve   |  |  |  |  |

|                                     |                      | synchronization in the inte                            | ernal synchronous mode.        |  |  |  |  |

| W4/D6                               | Installed            | This jumper may be ren                                 | noved to disable CLR OPT I     |  |  |  |  |

|                                     |                      |                                                        | preventing clearing of bits 03 |  |  |  |  |

|                                     |                      |                                                        | CSR (see Chapter 3 for bi      |  |  |  |  |

|                                     |                      | descriptions and Chapter 4                             | for signal functions).         |  |  |  |  |

| W5, W6/D6                           | Installed            | These jumpers may be                                   | removed to disconnect the      |  |  |  |  |

|                                     |                      |                                                        | between the modem and the      |  |  |  |  |

|                                     |                      | DU11. Removed at custon                                |                                |  |  |  |  |

| W9-W14/D4                           | Floating             | These jumpers control                                  | the receiver and transmitter   |  |  |  |  |

|                                     |                      | interrupt vector address (F                            |                                |  |  |  |  |

|                                     |                      | Jumper                                                 | Address Bit                    |  |  |  |  |

|                                     |                      | -                                                      |                                |  |  |  |  |

|                                     |                      | <b>W</b> 9                                             | BUS D03                        |  |  |  |  |

|                                     |                      | W10                                                    | BUS D04                        |  |  |  |  |

|                                     |                      | W11                                                    | BUS D05                        |  |  |  |  |

|                                     |                      | W12                                                    | BUS D06                        |  |  |  |  |

|                                     |                      | W13<br>W14                                             | BUS D07<br>BUS D08             |  |  |  |  |

|                                     |                      | ¥¥ 14                                                  | BO2 D08                        |  |  |  |  |

| W15/D4                              | Installed            |                                                        | wed to inhibit the BUS NPR L   |  |  |  |  |

|                                     |                      |                                                        | ntrol logic. (Removed only if  |  |  |  |  |

|                                     |                      | PDP-11/20 processor is use                             | ed without KH option.)         |  |  |  |  |

| W16/D1                              | Removed              | This jumper must be insta                              | lled if the DU11 is mounted in |  |  |  |  |

|                                     |                      |                                                        | mounting panel (Paragraph      |  |  |  |  |

| and the second second second second |                      | 2.1.1.1).                                              |                                |  |  |  |  |

Table 2-1 Jumper Assignments

## CHAPTER 3 DEVICE REGISTERS AND INTERRUPT REQUESTS

#### 3.1 SCOPE

This chapter provides a complete description of the DU11 device registers and the interrupt requests employed to service those registers.

#### 3.2 DEVICE REGISTERS

All software control of the DU11 is performed by means of five device registers. These registers have been assigned bus addresses and can be read or loaded (with the exceptions noted) using any PDP-11 instruction referring to their addresses. Address assignments can be changed via the rocker switches to correspond to any address within the floating address range of 160010 to 163776.

#### 3.2.1 Register Address Assignments

The five device registers and associated DU11 addresses are listed in Table 3-1.

#### 3.2.2 Register Title and Bit Assignments

Each of the five device registers plays a specific role in controlling and monitoring DU11 operation. Register titles, bit titles, and read/write capability labeling are intended to

facilitate the programmer's understanding of the purpose of each register relative to interface operation and to simplify software preparation.

**3.2.2.1 Title Assignments** – Register titles and functions are listed below:

- a. RXCSR programmed and monitored (read/ write) to control the RCVR (receiver) portion of the interface; to communicate interface status, requests, and supervisory data to the modem; and to monitor status and supervisory data inputs from the modem.

- b. RXDBUF monitored (read only) to detect interface RCVR status flags and RCVR parallel data outputs.

- c. PARCSR programmed (write only) to establish the overall operating parameters of the DU11, i.e., the mode of operation (synchronous or isochronous), word length (5, 6, 7, or 8 bits plus parity), parity (enabled or disabled), parity sense (odd or even), and sync character configuration.

| Table 3-1                         |  |

|-----------------------------------|--|

| DU11 Register Address Assignments |  |

|                                   |  |

| Register                    | Mnemonic | Mnemonic Address |            |  |  |

|-----------------------------|----------|------------------|------------|--|--|

| Receiver Status Register    | RXCSR    | 16XXX0           | Read/Write |  |  |

| Receiver Data Buffer        | RXDBUF   | 16XXX2           | Read Only  |  |  |

| Parameter Status Register   | PARCSR   | 16XXX2           | Write Only |  |  |

| Transmitter Status Register | TXCSR    | 16XXX4           | Read/Write |  |  |

| Transmitter Data Buffer     | TXDBUF   | 16XXX6           | Write Only |  |  |

XXX = Selected in accordance with floating device address scheme described in Appendix B.

- d. TXCSR programmed and monitored (read/ write) to control the XMTR (transmitter) portion of the interface, to control the resetting and initialization of the interface, and to control and monitor the maintenance mode operation of the interface.

- e. TXDBUF programmed (write only) to provide parallel data to the interface XMTR for serial transmission to the modem.

**3.2.2.2** Bit Assignments – The bit names indicate the function of the bit. The bits that are defined as "not used" or "write-only" are always read as 0. In the same respect, attempts to program the "not used" bits or "read-only" bits have no effect on the bit.

The following figures and tables describe register content. Figures 3-1 through 3-5 illustrate the register formats. Tables 3-2 through 3-6 list bit descriptions.

The mnemonic INIT is used frequently in the following tables and refers to the initialization signal generated by the processor. The processor will issue an INIT signal for any one of the following conditions:

- a. A programmed RESET instruction is processed.

- b. The processor START switch is pressed.

- c. The power fail sequence occurs.

During a power fail sequence, INIT is asserted when power is going down and again when power is coming up.

| 15                 | 14   | 13                | 12           | 11         | 10                 | 09                 | 08            | 07          | 06          | 05                   | 04          | 03                  | 02              | 01                  | . 00    |

|--------------------|------|-------------------|--------------|------------|--------------------|--------------------|---------------|-------------|-------------|----------------------|-------------|---------------------|-----------------|---------------------|---------|

| DA TA<br>SET<br>CH | RING | CLR<br>TO<br>SEND | CAR-<br>RIER | REC<br>ACT | SEC<br>REC<br>DATA | DATA<br>SET<br>RDY | STRIP<br>SYNC | R X<br>DONE | RX<br>INTEB | DATA<br>SET<br>INTEB | SCH<br>Sync | SEC<br>XMIT<br>DATA | REQ<br>TO<br>SD | DATA<br>TERM<br>RDY |         |

| R                  | R    | R                 | R            | R          | R                  | R                  | R/W           | R           | R/W         | R/W                  | R/W         | R/W                 | R/W             | R/W                 |         |

|                    |      |                   |              |            |                    |                    |               |             |             |                      |             |                     |                 |                     | 11-2244 |

| Bit | Name                            | Description                                                                                                                                                |

|-----|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | DAT SET CH<br>(Data Set Change) | When set, this bit indicates a modem status change.                                                                                                        |

|     | (Data Set Charge)               | This bit is set by a transition of any of the following lines:                                                                                             |

|     |                                 | <ul> <li>Ring</li> <li>Clear To Send</li> <li>Carrier</li> </ul>                                                                                           |

|     |                                 | <ul><li>Secondary Received Data</li><li>Data Set Ready</li></ul>                                                                                           |

|     |                                 | If bit 05 of this register is set, the setting of this bit will cause a RCVR interrupt.                                                                    |

|     |                                 | Read-only bit; cleared by INIT, Master Reset, and the DTI SEL 0 (RXCSR read strobe).                                                                       |

| 14  | RING<br>(Ring)                  | This bit reflects the state of the modem Ring line. When set,<br>this bit indicates that a Ring signal is being received from the<br>modem. Read-only bit. |

Table 3-2Receiver Status Register Bit Description

| Bit     | Name                                    | Description                                                                                                                                                                                       |  |  |  |  |  |

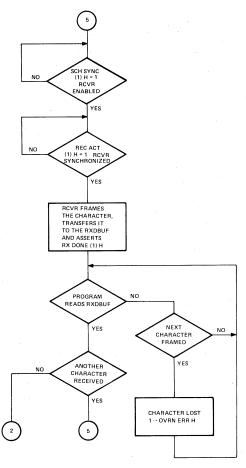

|---------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|