# MAINTENANCE MANUAL VOLUME I

The PDP-14 system and its unique approach to machine control, including its physical parts, its circuitry, and its expressed or implied methods of programming, are patent-pending. All rights are claimed by Digital Equipment Corporation. The information presented herein is proprietary in nature, and is intended solely to inform our customers in the use of our products.

Copyright © 1970 by Digital Equipment Corporation

The material in this manual is for information purposes and is subject to change without notice.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC PDP FLIP CHIP FOCAL DIGITAL COMPUTER LAB

# CONTENTS

| CHAD. | FED 1 CENTED AT                                                      | Page |

|-------|----------------------------------------------------------------------|------|

| CHAP. | TER 1 GENERAL                                                        |      |

| 1.1   | PDP-14 System                                                        | 1-1  |

| 1.2   | Maintenance Levels                                                   | 1-2  |

| 1.2.1 | On-Line                                                              | 1-2  |

| 1.2.2 | Off-Line                                                             | 1-2  |

| 1.3   | Test Equipment and Spares                                            | 1-3  |

| СНАРТ | ER 2 ON-LINE MAINTENANCE                                             |      |

| 2.1   | General                                                              | 2-1  |

| 2.2   | Machine or Process System Fault Isolation                            | 2-2  |

| 2.2.1 | Fault Isolation Technique                                            | 2-2  |

| 2.2.2 | NEMA Enclosure Input and Output Tables                               | 2-2  |

| 2.2.3 | System Troubleshooting Example #1, Control Input Device Malfunction  | 2-5  |

| 2.2.4 | System Troubleshooting Example #2, Control Output Device Malfunction | 2-6  |

| 2.2.5 | System Troubleshooting Example #3, PDP-14 System Malfunction         | 2-6  |

| 2.3   | PDP-14 System Fault Isolation                                        | 2-6  |

| 2.3.1 | PDP-14 Control Unit and Storage Box Checkout Procedure               | 2-6  |

| 2.3.2 | PDP-14 Storage Box Fault Isolation Procedure                         | 2-13 |

| 2.3.3 | PDP-14 Read Only Memory Checkout Procedure                           | 2-16 |

| 2.3.4 | PDP-14 Output Box Fault Isolation Procedure                          | 2-19 |

| 2.3.5 | PDP-14 Input Box Fault Isolation Procedure                           | 2-22 |

| 2.3.6 | PDP-14 Accessory Box Fault Isolation Procedure                       | 2-24 |

| 2.3.7 | Fault Isolation Without Test Computer                                | 2-29 |

| CHAPT | ER 3 THEORY OF OPERATION                                             |      |

| 3.1   | General                                                              | 3-1  |

| 3.2   | System Functional Description                                        | 3-3  |

| 3.2.1 | Internal Mode Instruction Set                                        | 3-3  |

| 3.2.2 | Cycle Control and Data Transfer                                      | 3-9  |

| 3.2.3 | External Computer Interface and Skip Comparator                      | 3-10 |

| 3.3   | Detailed Circuit Descriptions                                        | 3-10 |

| 3.3.1 | Test Flop and Conditional Jumps                                      | 3-10 |

| 3.3.2 | Major States                                                         | 3-13 |

| 3.3.3 | Timing Cycle                                                         | 3-16 |

# CONTENTS (Cont)

|       |                                                                  | Page          |

|-------|------------------------------------------------------------------|---------------|

| 3.3.4 | Manual Control and Power Detection Circuits                      | 3-21          |

| 3.3.5 | Read Only Memory (ROM) Circuits                                  | 3-25          |

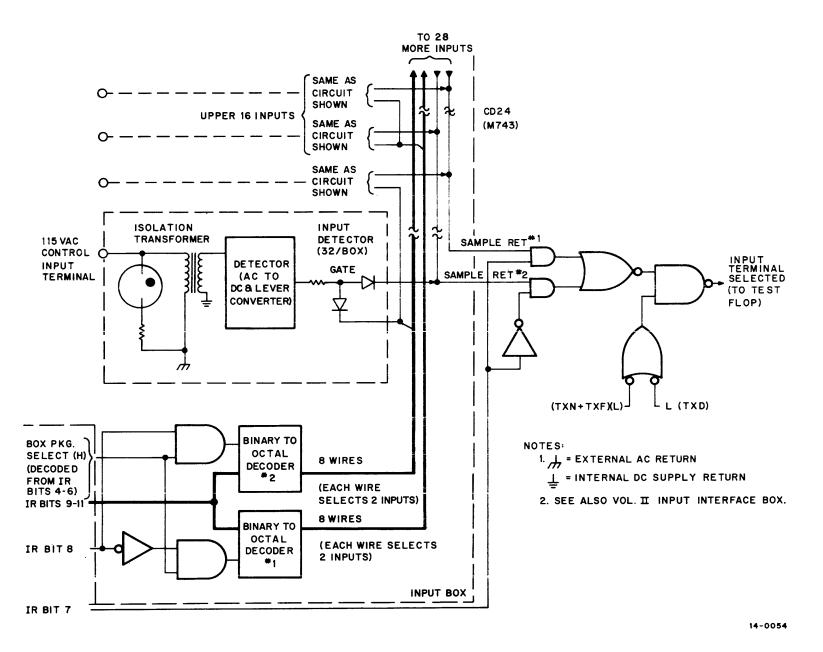

| 3.3.6 | Input Box Circuits                                               | 3-29          |

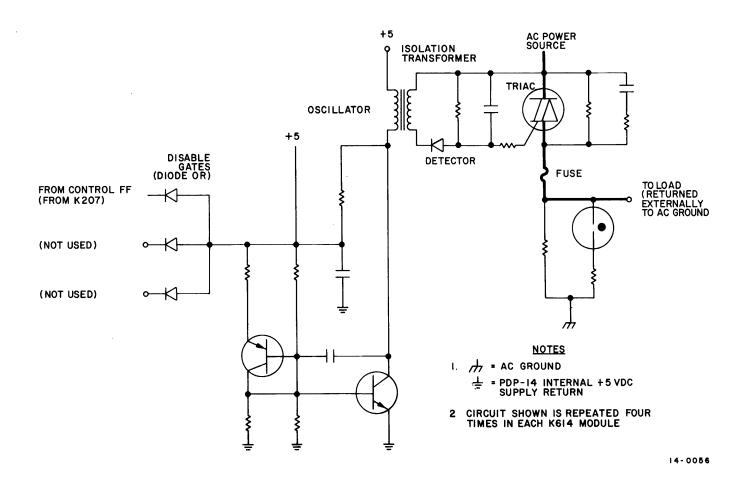

| 3.3.7 | Output Box Circuits                                              | 3-31          |

| 3.3.8 | Storage Box Circuits                                             | 3-31          |

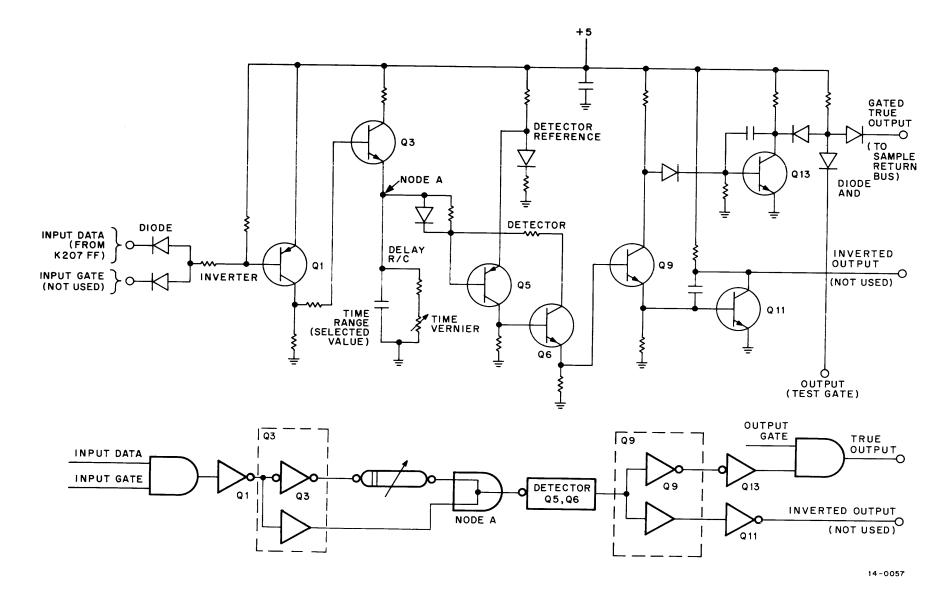

| 3.3.9 | Accessory Box Circuits                                           | 3-31          |

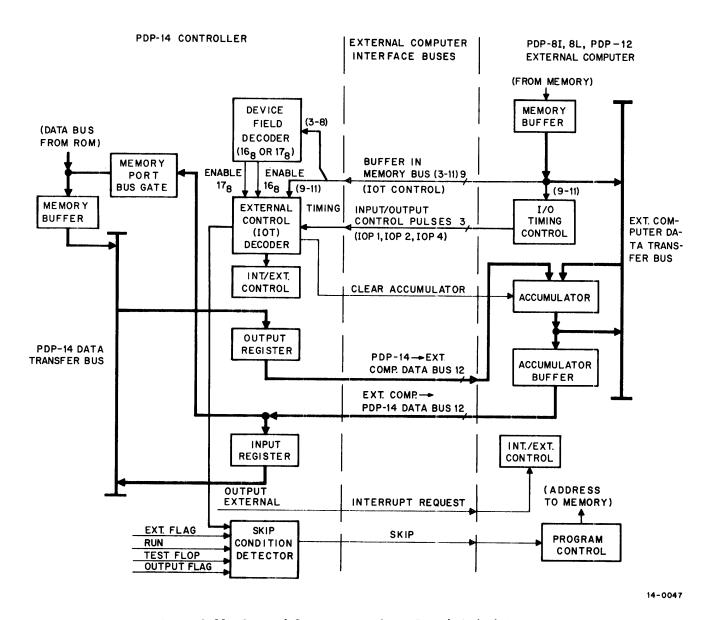

| 3.4   | External Computer Interface                                      | 3 <b>-</b> 34 |

| 3.4.1 | External Control Instruction Set                                 | 3-36          |

| 3.4.2 | External Mode Instruction Set                                    | 3-38          |

| 3.4.3 | External Computer Interface Circuits                             | 3-39          |

| 3.4.4 | Interrupt and External Mode Control Circuits                     | 3-40          |

| CHAPT | ER 4 OFF-LINE MAINTENANCE                                        |               |

| 4.1   | General                                                          | 4-1           |

| 4.2   | Component Fault Isolation Procedures                             | 4-1           |

| 4.2.1 | Control Unit Procedure                                           | 4-2           |

| 4.2.2 | ROM Assembly Procedure                                           | 4-3           |

| 4.2.3 | Accessory Box Procedure                                          | 4-6           |

| 4.2.4 | Hints and Kinks                                                  | 4-7           |

| 4.3   | Module Repair Techniques                                         | 4-8           |

|       | TABLES                                                           |               |

| 1-1   | Maintenance Test Equipment                                       | 1-3           |

| 1-2   | Module Spares                                                    | 1-4           |

| 2-1   | Test Program Error Code/Module Location Cross Reference          | 2-11          |

| 2-2   | Test Program Address/S-Box Module Location Cross Reference Table | 2-14          |

| 2-3   | Output Box Fault Isolation                                       | 2 <b>-</b> 21 |

| 2-4   | Input Box Fault Isolation                                        | 2-23          |

| 2-5   | Accessory Box Module/ABE-14 Error Code Cross Reference           | 2 <b>-</b> 28 |

| 2-6   | Accessory Box Module Location/Address Cross Reference            | 2 <b>-</b> 28 |

| 3-1   | PDP-14 Internal Mode Instruction Set                             | 3-6           |

| 3-2   | PDP-14 Register and Counters                                     | 3-8           |

| 3-3   | External Control (IOT) Instruction Set                           | 3-36          |

| 2_1   | External Mode Instruction Set                                    | 3-38          |

# **ILLUSTRATIONS**

|      |                                                                                              | ruge         |

|------|----------------------------------------------------------------------------------------------|--------------|

|      | PDP-14 Controller                                                                            | Frontispiece |

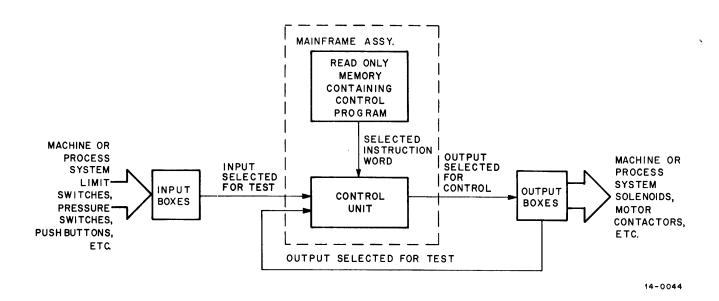

| 1-1  | PDP-14 Controller, Simplified Functional Diagram                                             | 1-1          |

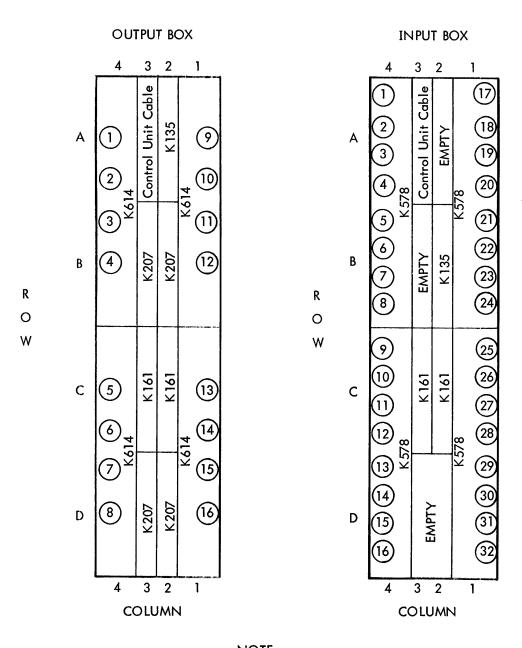

| 2-1  | NEMA Enclosure Input Box Terminal Assignment Table With Sample Entries                       | 2-3          |

| 2-2  | NEMA Enclosure Output Box Terminal Assignment Table With Sample Entries                      | 2-3          |

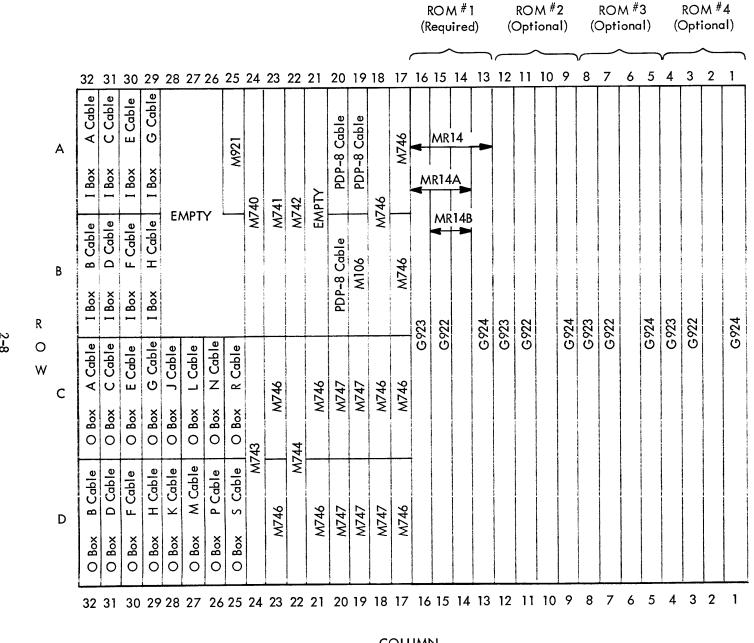

| 2-3  | Mainframe Module and Cable Connector Map, Front View                                         | 2-8          |

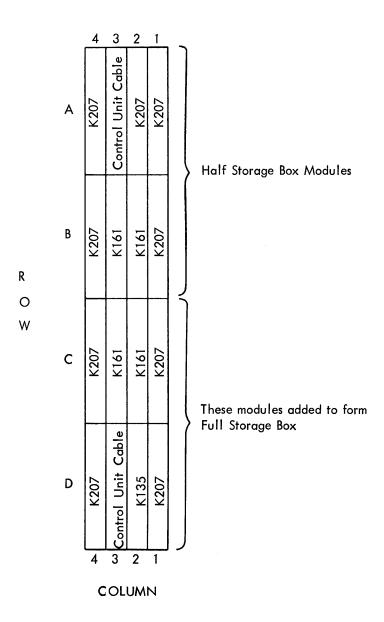

| 2-4  | Storage Box Module and Cable Connector Map, Front View                                       | 2-15         |

| 2-5  | Input and Output Boxes Module and Cable Connector Maps, Front View                           | 2-20         |

| 2-6  | Accessory Box Module and Cable Connector Map, Front View                                     | 2-27         |

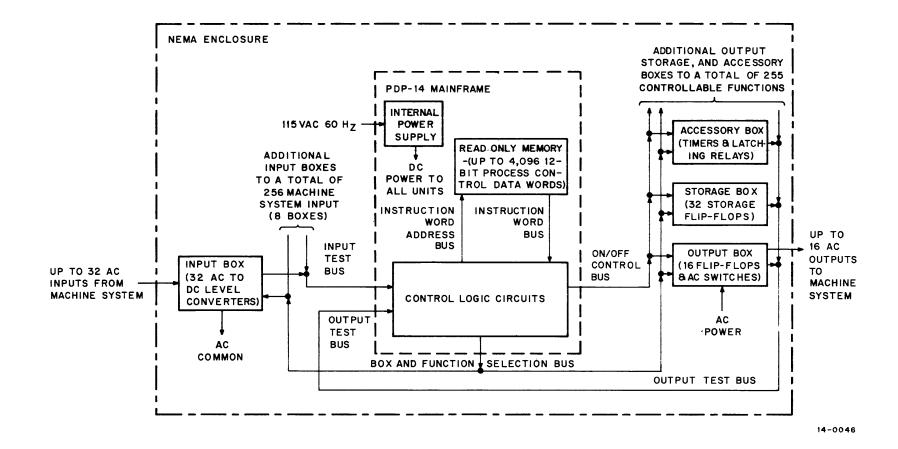

| 3-1  | PDP-14 Controller, Simplified Block Diagram                                                  | 3-2          |

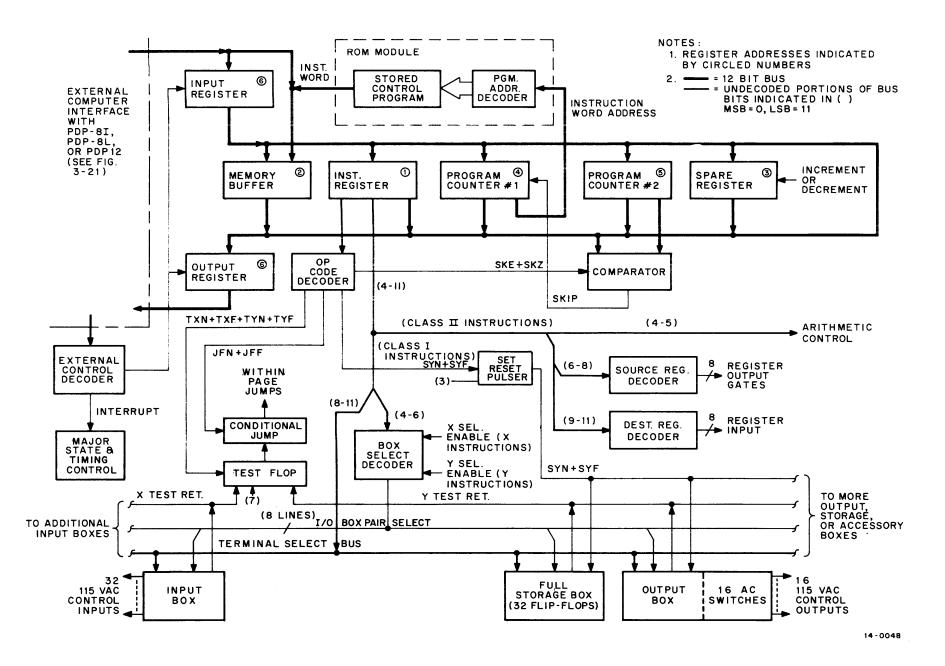

| 3-2  | PDP-14 Controller, Detailed Block Diagram                                                    | 3-4          |

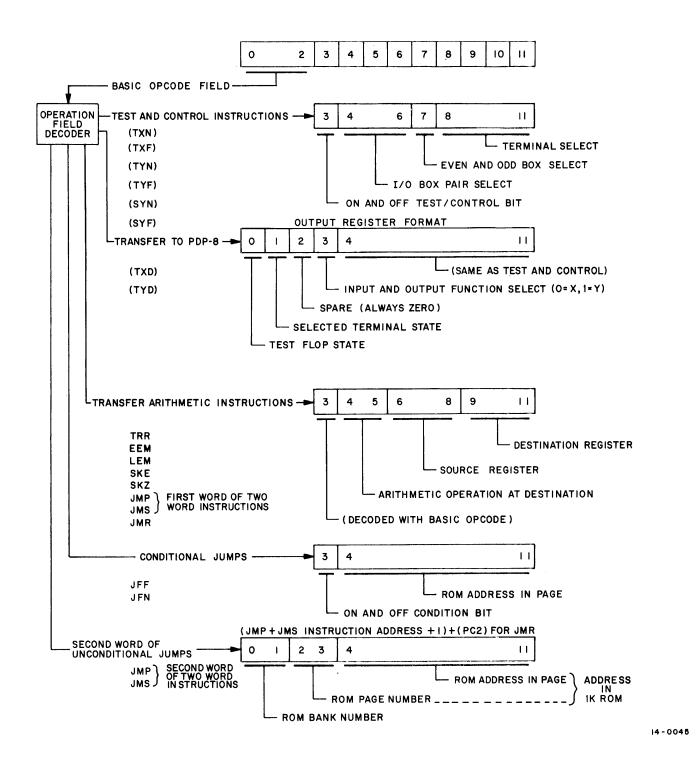

| 3-3  | Instruction Word Formats                                                                     | 3-5          |

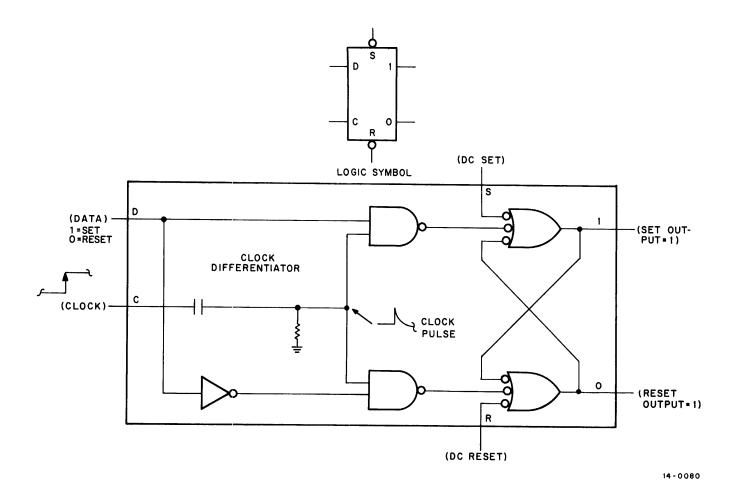

| 3-4  | Gated Flip-Flop and Equivalent Logic Circuit                                                 | 3-11         |

| 3-5  | Test Flop and Associated Circuits, Simplified Logic Diagram                                  | 3-12         |

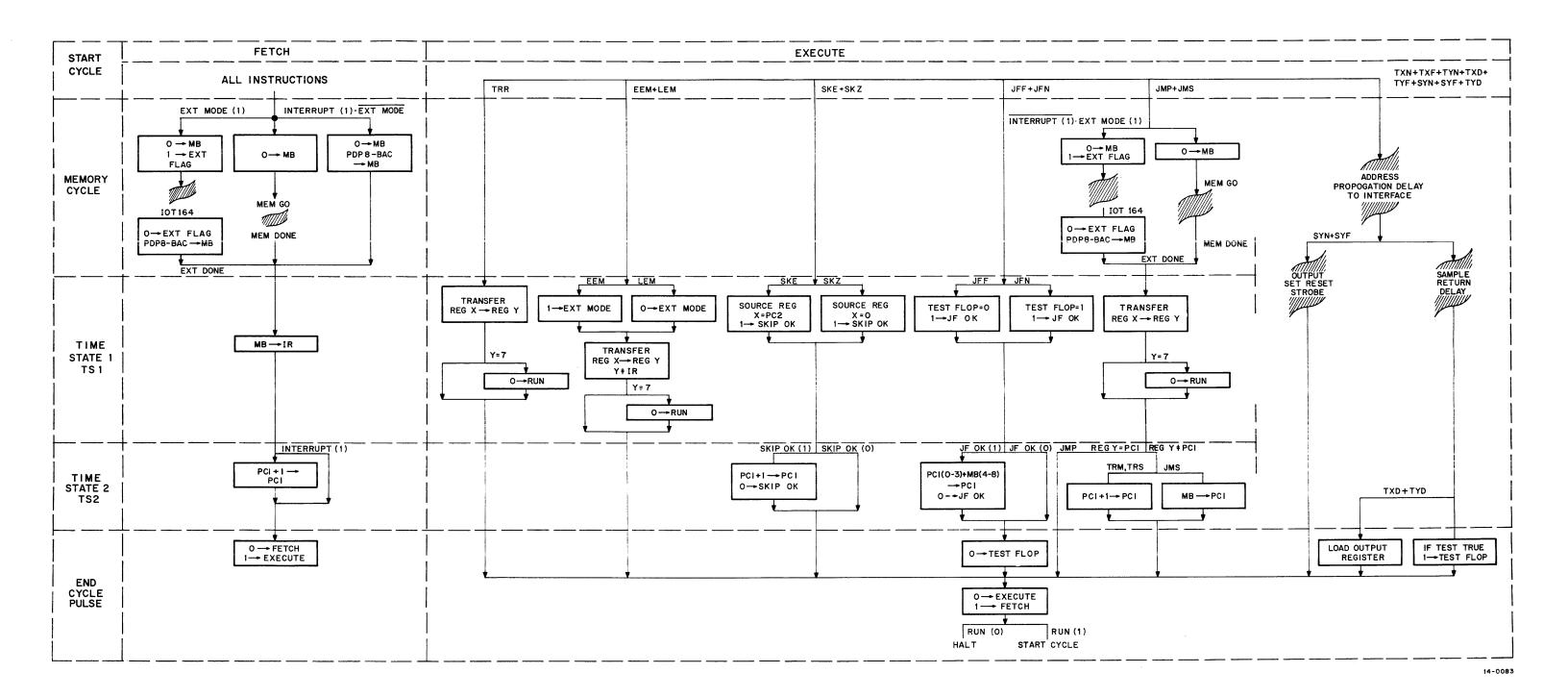

| 3-6  | PDP-14 Controller, Flow Diagram                                                              | 3-14         |

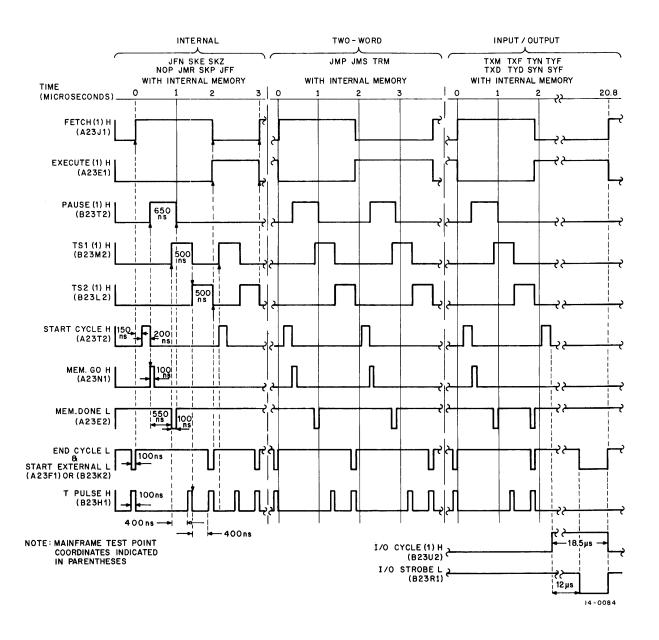

| 3-7  | Control Logic Timing Diagram                                                                 | 3-15         |

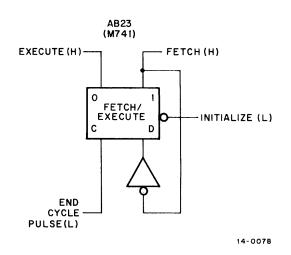

| 3-8  | Fetch/Execute Major States Toggle                                                            | 3-16         |

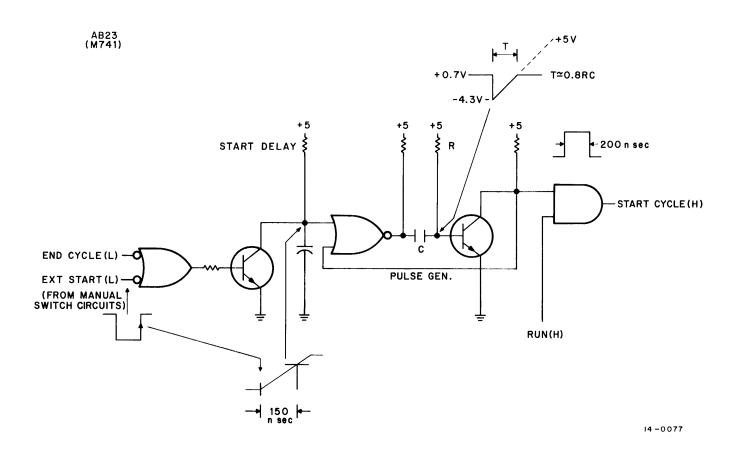

| 3-9  | Start Cycle Control, Simplified Logic Diagram                                                | 3-17         |

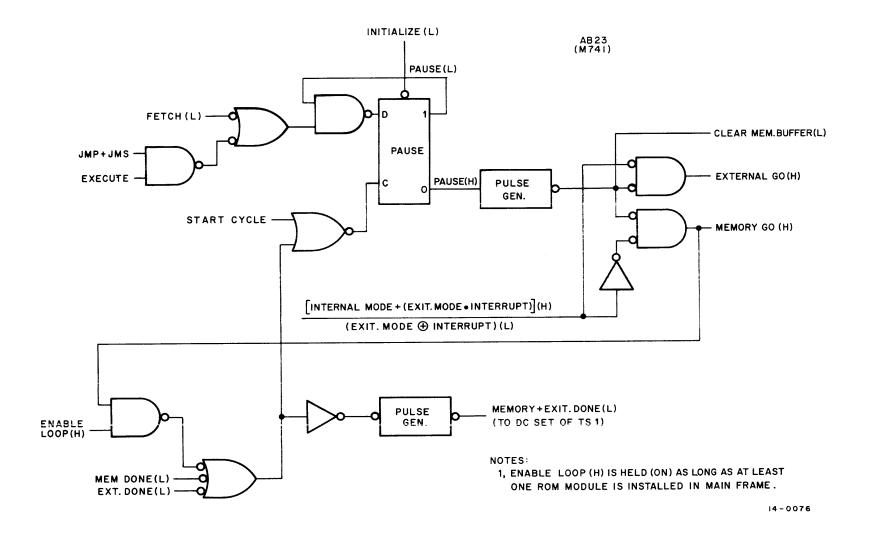

| 3-10 | Pause Cycle Control, Simplified Logic Diagram                                                | 3-18         |

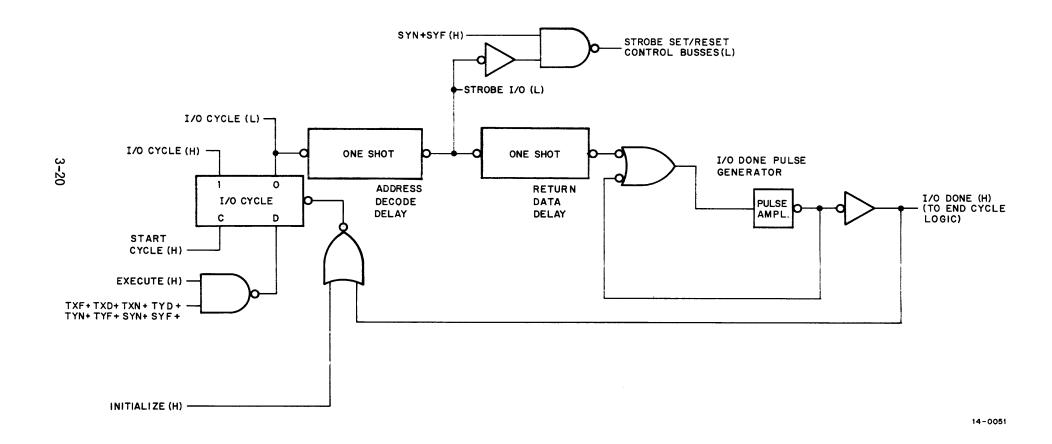

| 3-11 | I/O Cycle Control, Simplified Logic Diagram                                                  | 3-20         |

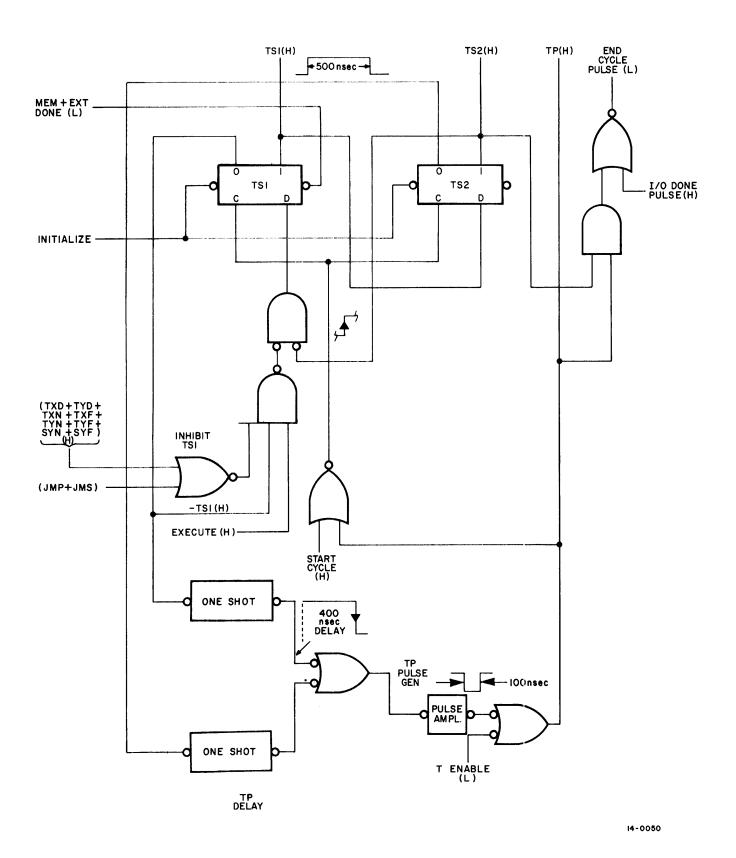

| 3-12 | TS1, TS2, End Cycle Pulse, and Timing Pulse Generators, Simplified Logic Diagram             | n 3-22       |

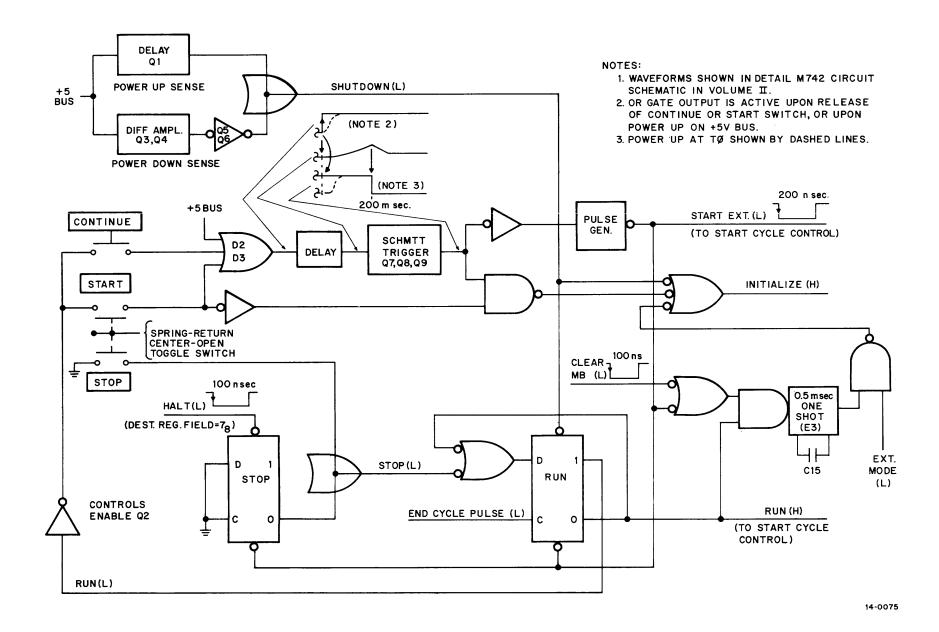

| 3-13 | Manual Controls and Power Sense Circuits, Simplified Logic Diagram                           | 3-23         |

| 3-14 | Read Only Memory (ROM), Simplified Logic Diagram                                             | 3-26         |

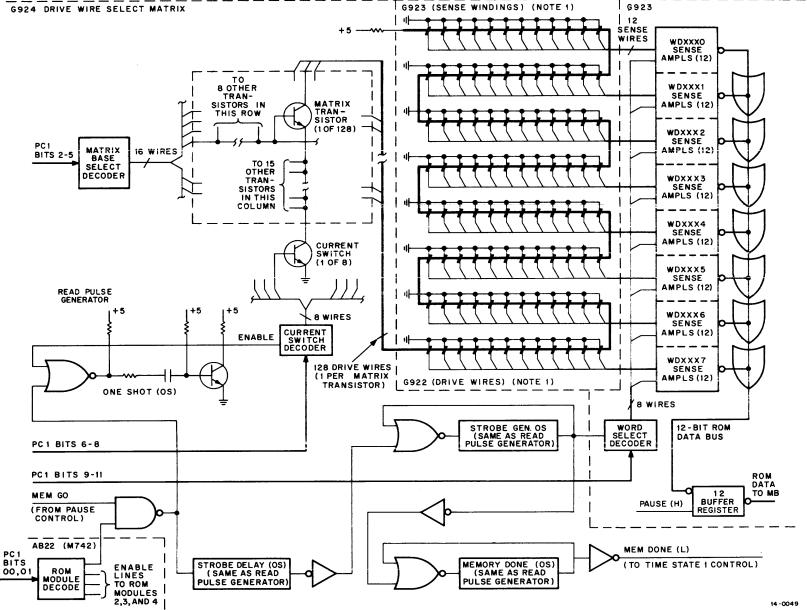

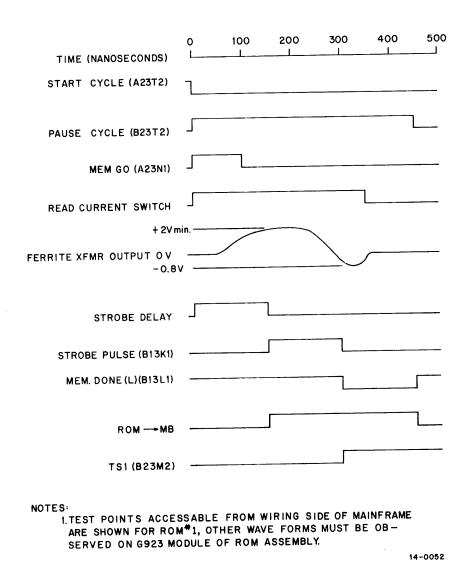

| 3-15 | ROM Timing Diagram                                                                           | 3-27         |

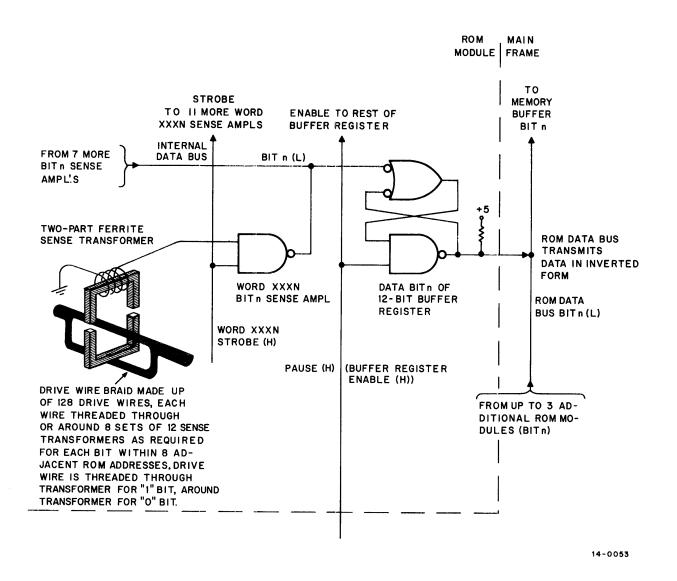

| 3-16 | ROM Data Sense Circuits, Simplified Logic Diagram                                            | 3-28         |

| 3-17 | Input Box Circuits, Simplified Logic Diagram                                                 | 3-30         |

| 3-18 | Output and Storage Box Circuits, Simplified Logic Diagram                                    | 3-32         |

| 3-19 | Output Box AC Control Circuit, Simplified Schematic Diagram                                  | 3-33         |

| 3-20 | Timer Module, Time Delay Circuit, Simplified Schematic Diagram, and Equivalent Logic Diagram | 3-35         |

| 3-21 | External Computer Interface, Detailed Block Diagram                                          | 3-40         |

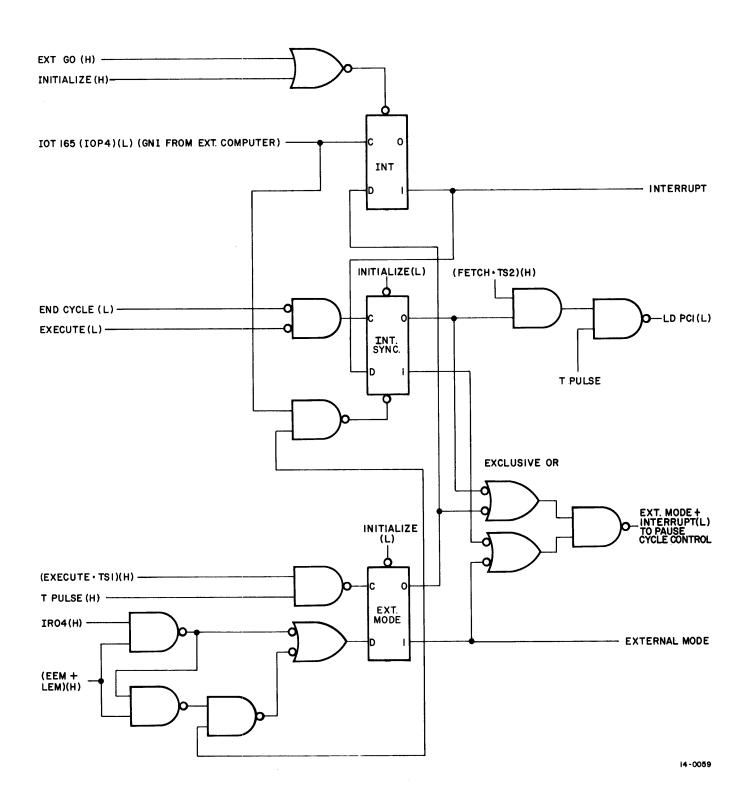

| 3-22 | Interrupt and External Mode Controls, Simplified Logic Diagram                               | 3-41         |

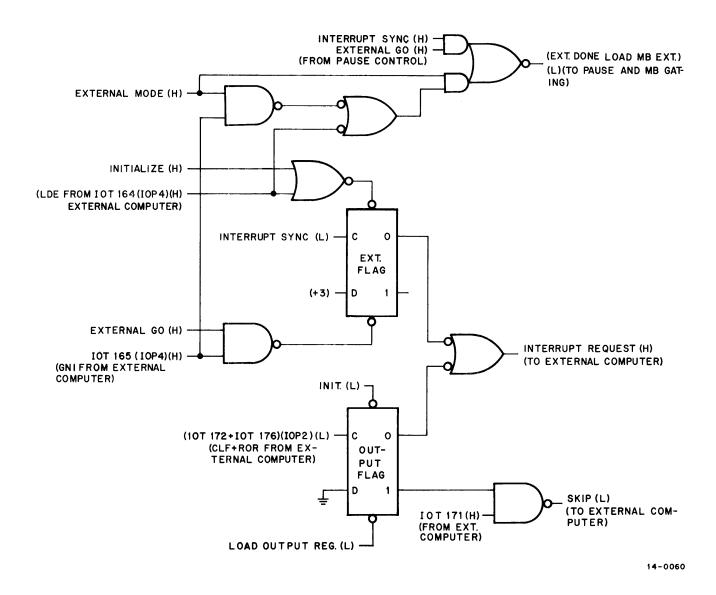

| 3-23 | External and Output Flags, Simplified Logic Diagram                                          | 3-43         |

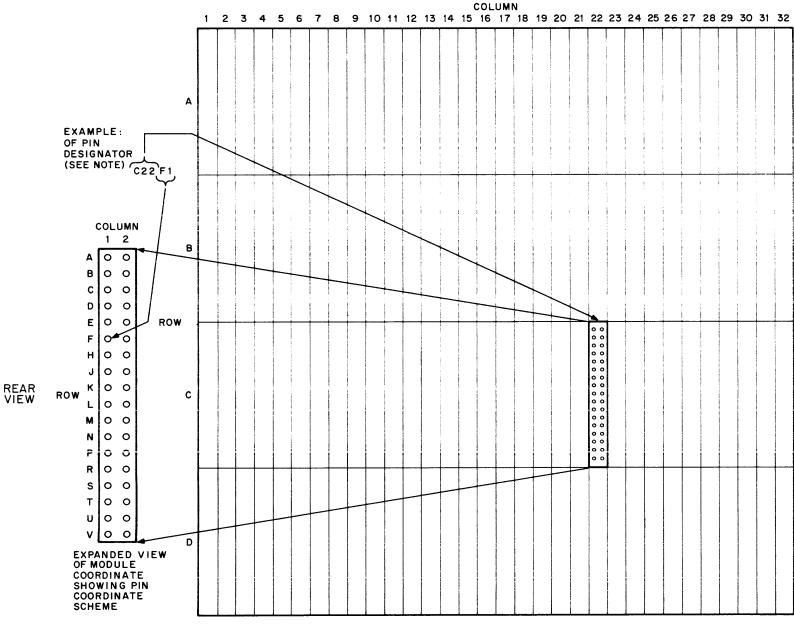

| 4-1  | Control Unit Mainframe Wirewrap Panel, Rear View, Showing Pin Coordinațe Sche                | me 4-4       |

PDP-14 Controller

### 1.1 PDP-14 SYSTEM

The PDP-14 System is designed to replace relay control systems in industrial and other applications using AC control power. Control relay wiring is replaced by a control program stored in Read Only Memory (ROM) modules located in the PDP-14 mainframe assembly (see Figure 1-1).

Figure 1-1 PDP-14 Controller, Simplified Functional Diagram

To accomplish its purpose, the PDP-14 tests the status (on or off) of machine or process system limit switches, pressure switches, push buttons, etc, and its own outputs. The PDP-14 compares these conditions, one at a time, with information from the control program within the ROM. The results of these comparisons cause outputs associated with these conditions to be turned on or off.

The basic operation sequence is as follows: first, the control unit obtains an instruction from the control program contained within the ROM (Fetch major state); second, the control unit performs the operation specified by the instruction (Execute major state).

The control program instructions take three basic forms.

- a. Test Instructions These instructions cause the control unit to test an input or output, specified in the instruction, to determine whether that input or output is on or off.

- b. Decision-Making Instructions These instructions are used to determine the future action of the program through the use of conditional jumps performed on the basis of test instruction results. These program jumps lead to additional test instructions and, eventually, to turning a particular output on or off.

- c. Control Instructions These instructions cause the control unit to turn on or off an output specified by the instruction. Additional instructions are used to facilitate transfer of information between the PDP-14 System and an external computer, and to perform internal "bookkeeping" functions.

The PDP-14 User's Manual (DEC-14-GGZA-D) provides detailed programming and installation information, which is beyond the scope of this Maintenance Manual.

### 1.2 MAINTENANCE LEVELS

Two distinct PDP-14 maintenance levels are presented in this manual. Both levels provide fault isolation and correction procedures; no preventive maintenance is required.

### 1.2.1 On-Line

Chapter 2 presents maintenance procedures to be performed without disconnecting the PDP-14 from the machine or process system. This material is presented in a step-by-step format in order that the maintenance electrician can rapidly isolate and correct the fault by simply substituting modules, in the rare event the fault is within the PDP-14 Controller.

Although Paragraph 2.3.7 describes a method of fault isolation and correction using only module substitution, it is recommended that the maintenance programs and a test computer be utilized to assist in fault isolation. The test computer (Digital Equipment Corporation, PDP-8/I, PDP-8/L, or PDP-12) can also be used for generation of new control programs as required to meet changes in the machine or process system. A complete package of programs is provided with each PDP-14.

### 1.2.2 Off-Line

Chapter 4 provides techniques and information required to repair defective modules or other PDP-14 components.

The defective module or other components must be removed to a location suitable for repair of relatively delicate

electronic equipment. In addition, personnel performing these procedures must be familiar with digital equipment hardware, electronic and logic schematic diagrams, and electronic equipment repair techniques. These personnel must also thoroughly understand the operation of PDP-14 circuits. To assist in this, Chapter 3 consists of a complete discussion of PDP-14 circuits oriented toward the technician with a good understanding of basic electronic and digital circuits.

Volume II of this manual contains a complete set of engineering physical (parts location) drawings and electrical schematic diagrams of PDP-14 modules to be used with Chapter 4 in fault isolation and repair of defective modules. The techniques in Chapter 4 require a test computer and maintenance programs, in addition to standard electronic test equipment.

### 1.3 TEST EQUIPMENT AND SPARES

Table 1-1 lists the test equipment required (but not supplied) for the two levels of maintenance. Table 1-2 is a list of recommended spare modules.

Table 1-1

Maintenance Test Equipment

| Equipment Description                                                                   | On-Line<br>Maintenance    | Off-Line<br>Maintenance |

|-----------------------------------------------------------------------------------------|---------------------------|-------------------------|

| Test Computer: Digital Equipment Corp. PDP-8/1, PDP-8/L, or PDP-12                      | Optional (recommended)    | Required                |

| Teleprinter: Teletype Corp. 33ASR                                                       | Optional (recommended)    | Required                |

| Test Computer Interface Pkg.: DA14–I (for PDP–8/I), DA14–L (for PDP–8/L or PDP–12).     | Optional<br>(recommended) | Required                |

| Oscilloscope: Bandwidth Min. 5 mHz,<br>Min. Gain 1 V/cm, external trigger or dual trace | Not used                  | Required                |

| Volt/Ohm Meter: 1,000 ohms/volt                                                         | Not used                  | Optional                |

| Module Extender: Digital Equipment Corp. Type W982                                      | Not used                  | Required<br>(four)      |

Table 1-2 Module Spares

| Type<br>(one each) | Description                              | Usage                  |

|--------------------|------------------------------------------|------------------------|

| M740               | Instruction Decoder and Register Control | Control Unit           |

| M741               | Major States and Timing                  | Control Unit           |

| M742               | PDP-14 Switch and Power Control          | Control Unit           |

| M743               | K Interface Control                      | Control Unit           |

| M744               | Register Compare Circuit                 | Control Unit           |

| M745*              | PDP-14 to PDP-8/L, -8/I Interface        | Control Unit           |

| M746               | Bus Register                             | Control Unit           |

| M747               | Incrementing Bus Register                | Control Unit           |

| G922               | ROM Braid Board                          | Control Unit           |

| G923               | ROM Sense Amplifier                      | Control Unit           |

| G924               | ROM Selection                            | Control Unit           |

| M921*              | Device Code Select Jumper Board          | Control Unit           |

| M106*              | Dot NOR Gates                            | Control Unit           |

| K578               | AC Inputs                                | I-Boxes                |

| K614               | Isolated AC Switch                       | O-Boxes                |

| K302**             | Two Timers                               | A-Boxes                |

| K272***            | Retentive Memory                         | A-Boxes                |

| K207               | Flip-Flop                                | O-, S-, and A-Boxes    |

| K161               | Binary-to-Octal Decoder                  | I-, O-, S-, and A-Boxe |

| K 135              | Inverters                                | I-, O-, S-, and A-Boxe |

| BC14A              | Cable                                    | I-, O-, S-, and A-Boxe |

<sup>\*</sup>Required only for external computer interface.

<sup>\*\*</sup>Required only if accessory box time delays are used.

\*\*\*Required only if accessory box retentive memories are used.

### 2.1 GENERAL

The PDP-14 Controller requires no periodic maintenance. Maintenance consists of fault isolation and repair in the event of a machine or process system malfunction. Though the PDP-14 Controller is seldom the cause of the malfunction, the neon lamps on the PDP-14 input and output boxes are very useful tools for determining whether the problem is in the machine or process system (and where within the machine or process system) or within the PDP-14 System.

The machine or process system is defined as the machine, or group of machines, under the control of a PDP-14 Controller. The machine or process system includes all control solenoids, limit switches, etc, and all control wiring between these elements and the PDP-14 input and output box terminals.

On-line repair consists of two major steps, which must be performed in sequence:

| Step | <u>Procedure</u>                                                                                                                                                                                                                    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Fault isolation to wiring and components outside the PDP-14 Controller or to PDP-14 Controller components; and                                                                                                                      |

| 2    | Localization and repair of the machine or process system wiring or component (limit switch, pushbutton, solenoid, motor contactor, etc), or localization and repair of the PDP-14 Controller by substitution of plug-in components. |

Paragraph 2.2 describes the techniques to follow in order to make maximum use of the PDP-14 lamps in locating a defective component outside the PDP-14 Controller.

If it is determined from following the procedures of Paragraph 2.2 that the trouble is definitely within the PDP-14, Paragraph 2.3 contains step-by-step procedures to locate the defective PDP-14 component. On-line repair of the PDP-14 is limited to substituting a properly functioning component (module) for the defective component. If the trouble is determined to be within the PDP-14 Control Unit mainframe but cannot be isolated using the procedures described in Paragraph 2.3, the mainframe must be removed from the NEMA enclosure and sent to a test area where specially trained personnel and electronic test equipment are available to perform detailed troubleshooting and repair procedures.

### 2.2 MACHINE OR PROCESS SYSTEM FAULT ISOLATION

The techniques described under this heading isolate the malfunction to a machine or process system component (AC control wiring, limit switches, pushbuttons, solenoids, motor contactors, etc), or to the PDP-14 system (input and output boxes, and control unit modules).

### 2.2.1 Fault Isolation Technique

The machine or process system malfunction is usually apparent at one or more machine stations, or may be indicated by fault indicator lamps on the operator's console. In either case, the machine or process system circuits associated with the fault should be checked, using the neon lamps on the PDP-14 input and output boxes.

If the neon lamps on the PDP-14 input and output boxes disagree with the actual status of the machine, the trouble is <u>not</u> in the PDP-14. Thus, if a carriage reaches the end of its travel and depresses a normally-open limit switch operating lever but the associated input box lamp does not light, the trouble must be in the limit switch or in the wiring to the PDP-14 input box terminal adjacent to the lamp.

If a motor is not running, but the PDP-14 output box lamp corresponding to the contactor for that motor is lighted, the trouble is <u>not</u> in the PDP-14. The trouble is in the AC wiring from the output box to the contactor, within the contactor, in the high power wiring to the motor, or within the motor itself.

However, if the motor fails to run when the carriage activates the limit switch, and the input box lamp associated with the limit switch is lighted but the output box lamp associated with the motor contactor is not lighted, then there is a malfunction within the PDP-14. In other words, if the combination of input box lights, as observed, does not produce the correct output lamp response, the procedures in Paragraph 2.3 must be followed to isolate the trouble to a PDP-14 input or output box or control unit module.

### 2.2.2 NEMA Enclosure Input and Output Tables

To assist in locating the input box lamps associated with a particular control function, a list is posted inside the NEMA enclosure door to identify each input box terminal. A sample of the input table format is presented in Figure 2-1.

A similar table lists the output box terminals and the conditions required to turn each output on. A sample of the output table format is presented in Figure 2-2.

### NOTE

There is usually an interlock on the NEMA enclosure door. This interlock must be defeated in order to observe output box lamps.

# Input Box Terminal Assignments

| Input Box<br>and<br>Terminal Number | Input Device<br>Identification      | Functional Description of Active State                                 | Input<br>Device<br>X Number |

|-------------------------------------|-------------------------------------|------------------------------------------------------------------------|-----------------------------|

| А8                                  | UNCLAMP<br>Pushbutton, 10PB         | Applies power to input terminal when pressed.                          | X10                         |

| A16                                 | Head Retracted<br>Limit Switch, 4LS | Applies power to input terminal when machine head is fully retracted.  | X20                         |

| A14                                 | Clamps In Limit<br>Switch, 1LS      | Limit switch applies power to input terminal when clamp is engaged.    | X16                         |

| A17                                 | Clamps Out Limit<br>Switch, 5LS     | Limit switch removes power from input terminal when clamp is released. | X21                         |

Figure 2-1 NEMA Enclosure Input Box Terminal Assignment Table With Sample Entries

# Output Box Terminal Assignments

| Output Device<br>Identification                    | Output Device Control Equation  X=Input Terminal, Y=Output Terminal, +=OR, *=AND, /=NOT                     | Output Device<br>Y Number |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------------------|

| Red AUTOMATIC<br>Console Lamp, 2LT                 | <pre>\$1. 2LT=3PB*(4PB+2LT)*/3LT Y0 = X0*(X1 + Y0)*/Y1</pre>                                                | Υ0                        |

| Amber MANUAL<br>Console Lamp, 3LT                  | \$2. 3LT=3PB*(5PB+3LT)<br>Y1 = X0*(X2 + Y1)                                                                 | Υ1                        |

| Machine Head FULL DEPTH<br>Amber Console Lamp, 5LT | <pre>\$9. 5LT = (3LS*/4LS)+(1LS*2LS*5LT) Y2 = (X16*/X17)+(X15 * Y2)</pre>                                   | Y2                        |

| Release Clamp<br>Solenoid B                        | ;14. SOLB = 4LS*3LT*10PB+[(1LS*2LS*5LT+SOLB)*/5LS*/6LS*2LT] Y5 = X17*Y1 * X7 +[( X15 * Y2+ Y5 )* /X20 *Y0 ] | Y5                        |

Figure 2–2 NEMA Enclosure Output Box Terminal Assignment Table With Sample Entries

The input and output box terminals are numbered in octal from top to bottom starting with the lamp in the top left corner then down the right row of lamps ( $0_8$  through  $37_8$  for input boxes,  $0_8$  through  $17_8$  for output boxes).

The right-hand column of the Output Box Terminal Assignment Table defines the conditions required to turn a particular output ON. These conditions are stated in Boolean algebra, which is simply a shorthand method of describing the conditions necessary to turn on the output box terminal. The slash symbol (/) is used to indicate negation of a signal; e.g., /X17 means NOT X17.

When the asterisk symbol (\*) appears between two terminal designators, the conditions on either side of the asterisk MUST be present in order to satisfy that portion of the statement. Thus

means that the lamp associated with input terminal X16 must be on, and the lamp associated with input terminal X17 must be off in order to turn the output terminal ON.

When the plus symbol (+) appears between two terminal designators, either one or the other condition flanking the plus symbol (or both) must be present in order to satisfy that portion of the statement. Thus

$$X16+/X17$$

means that the lamp associated with input terminal X16 must be on, or the lamp associated with input terminal X17 must be off (or both conditions) in order to turn the dependent output ON.

Parentheses are used to combine a group of conditions to be considered a SINGLE condition in relation to other conditions outside the parentheses. Thus the Boolean statement

$$X16*(/X17+X15)$$

means that either the lamp associated with input terminal X17 be off, or the lamp associated with input terminal X15 be on; and, in addition to this requirement, the lamp associated with input terminal X16 must be on.

Several sets of parentheses, nested one within the other, may be used in a single Boolean equation. Always check lamps starting with those outside any parentheses, then check those within the innermost sets of parentheses—noting whether or not the relationship within a single set of parentheses is satisfied before going to the next wider set of parentheses. In this way it can be determined if the combination of lamps, as observed, should cause the associated output lamp to light. Thus

$$X16* ((/X17 + Y13) * X15)$$

means the lamp associated with input terminal X17 must be off, or the lamp associated with output terminal Y13 must be on, or both. If one of these three possibilities is observed on the lamps, then, additionally, the lamp associated with input terminal X15 must be on. If the conditions described thus far are observed in some form, then the lamp associated with input terminal X16 must also be on in order for the output lamp and circuit controlled by this relationship to be turned on.

### NOTE

Whenever groups of parentheses are encountered, always work from the innermost sets, then consider the contents of the innermost sets as single conditions to be considered in relation to the other conditions bracketed by the next wider set of parentheses.

# 2.2.3 System Troubleshooting Example #1, Control Input Device Malfunction

As an example of the system troubleshooting procedure, assume that an automatic transfer line machining engine blocks is stopped by a malfunction. A visual check of the line reveals that the left-hand clamp holding the blocks under a particular machining head is still clamped, even though the engine block at that station has already been machined and the clamp should have released. The trouble is therefore associated with the clamp and its control circuitry.

The NEMA enclosure housing the PDP-14 is opened (the interlock must be defeated) and the solenoid controlling the clamp release is located in the output box terminal assignment table inside the NEMA enclosure door (see sample entries in Figure 2-2). The PDP-14 Output Box and terminal number associated with the clamp release solenoid are noted, and the lamp associated with that terminal is observed.

The lamp associated with the clamp solenoid is not lighted. This does <u>not</u> mean that the PDP-14 has malfunctioned. It simply means that the trouble is apparently not in the clamp release solenoid or the control wiring between the output box and the solenoid.

It is now necessary to return to the output box terminal assignment table and compare the conditions required to turn on output box terminal Y6 with the existing state of the input and output box lamps. It is observed that the lamp associated with input terminal X20 is not lighted. As this condition is necessary in order to activate output terminal Y6, it can now be assumed that the trouble is definitely not in the PDP-14 system, but must be in the outside circuit associated with input terminal X20.

The input box terminal assignment table is now consulted, and it is found that input terminal X20 is connected to limit switch 4LS, which should be ON when the machine head is fully retracted (see sample entries in Figure 2-1). The machine head is observed to be fully retracted; therefore, the trouble must be in the limit switch or its associated wiring. A check of the limit switch reveals that it has, in fact, failed. Replacing the switch puts the line back in production again.

# 2.2.4 System Troubleshooting Example #2, Control Output Device Malfunction

The same machine system malfunction described in Paragraph 2.2.3 is observed. This time the lamp associated with output terminal Y6 is lighted. The trouble is <u>not</u> in the PDP-14 System, but must be in the solenoid, in the wiring between the output box and the solenoid, or in the machinery between the solenoid and the clamp. Examination reveals that a defective hydraulic valve, controlled by the solenoid, prevented release of the clamp. The valve is replaced and the line put back in production.

## 2.2.5 System Troubleshooting Example #3, PDP-14 System Malfunction

The same machine system malfunction described in Paragraph 2.2.3 is observed. This time the lamp associated with output terminal Y6 is not lighted, but all the conditions required to activate output terminal Y6 are present. The trouble must be assumed to be in the PDP-14 System.

### NOTE

Each PDP-14 Output Box terminal is fused. If it is suspected that an output load has exceeded five amperes, the output circuit should be repaired to remedy the overcurrent condition (shorted wiring, solenoid winding, etc), and the output box fuse associated with that terminal should be checked. If the output box fuse is blown, the lamp associated with that output will not light.

If the trouble is in the PDP-14 system, the procedures in Paragraph 2.3 must be followed to isolate the trouble to a control unit module or to an input or output box.

# 2.3 PDP-14 SYSTEM FAULT ISOLATION

The procedures under this heading should not be performed until the procedures described in Paragraph 2.2 have been performed and the trouble has been definitely isolated to the PDP-14 System. The test computer procedures in Paragraphs 2.3.1 through 2.3.6 must be performed in sequence, the one exception being that the procedure in Paragraph 2.3.4 may be performed first if it is suspected that an output box fuse has been blown because of a control output short or other circuit overload conditions.

If an external computer is not available for fault isolation, Paragraph 2.3.7 describes a few simple substitution techniques which may be used to isolate the defective PDP-14 System module.

# 2.3.1 PDP-14 Control Unit and Storage Box Checkout Procedure

### CAUTION

PDP-14 and/or test computer circuits may be damaged if modules or connectors are inserted or removed with power ON.

| этер_ | Procedure                                                                                                                |

|-------|--------------------------------------------------------------------------------------------------------------------------|

| 1     | Remove PDP-14 control unit shield cover.                                                                                 |

| 2     | Connect test computer (PDP-8/I or PDP-8/L) system power cable to convenience outlet on PDP-14 control unit switch panel. |

| 3     | Place PDP-14 Control Unit and Test Computer Panel Switches in OFF position.                                              |

| 4     | Connect three control cables between the test computer and the PDP-14 control unit as follows:                           |

|       |                                                                                                                          |

| From               |                     | To Test Compu                             | ter                |

|--------------------|---------------------|-------------------------------------------|--------------------|

| PDP-14<br>Location | PDP-8/I<br>Location | PDP <b>-</b> 8/L<br>Location<br>(4K) (8K) | PDP=12<br>Location |

| A19                | J05 & J06           | D34 B34                                   | N16                |

| A20                | J03 & J04           | D35 B35                                   | N15                |

| B20                | J01 & J02           | D36 B36                                   | N14                |

Disconnect all Input (I) Box, Storage (S) Box, Accessory (A) Box, and Output (O) Box cables from PDP-14 control unit mainframe.

### NOTE

These connectors should be labeled with the I or O box letter designator or mainframe location designator to facilitate replacement when testing is completed.

Insert all storage box (S-Box) cable connectors into adjacent PDP-14 mainframe output box locations (see Figure 2-3). Always insert full S-Box cable connectors first, making certain that cables leaving the top of the S-Boxes are connected to mainframe row C connectors and cables leaving the bottom of the S-Boxes are connected to the mainframe row D connectors.

### NOTE

Any number of "full" S-Boxes can be checked at one time, but only one half S-Box can be checked at one time, and its cable connector must be inserted into the last sequential mainframe output box connector (this will always be in row C). If additional half S-Boxes must be checked, the first half S-Box tested must be disconnected at the mainframe, the next half S-Box cable connected, and the entire test cycle repeated.

- 7 Place PDP-14 control unit and test computer power switches in ON position.

- Place PDP-14 START/STOP switch momentarily in STOP position.

- 9 Set test computer SWITCH REGISTER to 7777<sub>8</sub>. The correct switch configuration for this is

### 111 111 111 111

Press the LOAD ADDRESS switch on test computer.

NOTES:

- 1. Maximum Mainframe Configuration Shown.

- 2. O Box Letter Designators "I", "O", and "Q" are not used to Prevent Confusion With Numbers "1" and "0".

COLUMN

Figure 2-3 Mainframe Module and Cable Connector Map, Front View

| Step | Procedure                                                                                                                                                                                                                                                                                                                                           |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11   | Load the TEST-14 paper tape into the test computer teleprinter paper-tape reader as follows:                                                                                                                                                                                                                                                        |

|      | a. Set the reader START/STOP/FREE switch to the FREE position.                                                                                                                                                                                                                                                                                      |

|      | <ul> <li>Release the cover guard by means of the latch at the right and open<br/>cover.</li> </ul>                                                                                                                                                                                                                                                  |

|      | c. Insert the leader (start) end of the punched tape from the rear over the<br>reader sprocket wheel so that the small holes in the tape engage the<br>sprocket teeth and there are 3 holes spaces on the tape to the left of the<br>sprocket wheel. The leader portion of tape has a single row of large<br>holes and a single row of small holes. |

|      | d. Close reader cover.                                                                                                                                                                                                                                                                                                                              |

| 12   | Place paper-tape reader START/STOP/FREE switch to START position.                                                                                                                                                                                                                                                                                   |

| 13   | Press test computer START switch momentarily. Tape should now move through reader until it is completely read and only the trailing portion remains in the reader.                                                                                                                                                                                  |

|      | NOTE                                                                                                                                                                                                                                                                                                                                                |

|      | If tape stops before it has been completely read, place tape leader in reader and press test computer CONT switch momentarily.                                                                                                                                                                                                                      |

| 14   | Remove the trailing portion of the TEST-14 paper tape from the reader by releasing the cover guard with the latch and opening the reader cover. Lift the tape off the sprocket wheel.                                                                                                                                                               |

| 15   | Enter the number 200g on test computer console SWITCH REGISTER. The correct switch configuration for this is                                                                                                                                                                                                                                        |

|      | 000 010 000 000                                                                                                                                                                                                                                                                                                                                     |

| 16   | Press the LOAD ADDRESS switch on test computer console.                                                                                                                                                                                                                                                                                             |

| 17   | Enter the following configuration in the SWITCH REGISTER switches:                                                                                                                                                                                                                                                                                  |

|      | 000 000 000 000                                                                                                                                                                                                                                                                                                                                     |

|      | if PDP-14 control unit module positions C20 and D20 are empty, or enter                                                                                                                                                                                                                                                                             |

|      | 000 000 100 000                                                                                                                                                                                                                                                                                                                                     |

|      | if PDP-14 control unit module positions C20 and D20 contain modules.                                                                                                                                                                                                                                                                                |

| 18   | Press the START switch on test computer console. Program will type                                                                                                                                                                                                                                                                                  |

|      | HOW MANY-I-BOXES?                                                                                                                                                                                                                                                                                                                                   |

| 19   | Respond to this question by typing the number zero.                                                                                                                                                                                                                                                                                                 |

|      | then press the carriage return (RETURN) key.                                                                                                                                                                                                                                                                                                        |

|      | - ,                                                                                                                                                                                                                                                                                                                                                 |

Step Procedure

19 (Cont)

### NOTE

Do not type the letter "o". This character is not recognized by the test program.

Program will type

HOW MANY O-BOXES?

20 Respond to this question by typing the number zero.

0

Then press the RETURN key.

The program will type

HOW MANY HALF S-BOXES?

Respond to this question by typing the number of S-Box connectors inserted in succeeding output box connector locations, then press RETURN key.

### NOTE

Do not type the letter "I". This character is not recognized by the test program.

The test program will now start and run automatically. If the program types

PASS 1 COMPLETE

the PDP-14 has been tested and found to be operating properly. In this case, the problem can be assumed to be in an Input or Output box or in the machine control program; proceed to Paragraph 2.4. If the program types anything else, proceed to the following step.

## NOTE

If the test program types PDP-14 STOPPED, substitute PDP-14 control unit modules at locations AB23 (M741) and AB22 (M742). If the test program types PDP-14 HUNG, or if the test computer RUN lamp goes out, substitute PDP-14 control unit modules at locations AB23 (M741) and AB18 (M745).

- If the test program detects a malfunction in the PDP-14 control unit, the program will identify the problem area by typing a two-letter error code flanked by asterisks. The module locations referenced by each two-letter error code are identified in Table 2-1. Module types are presented in parentheses following the module locations (a module map is presented in Figure 2-3). Substitute the module at the first location listed for a particular error code in Table 2-1.

- Press test computer STOP switch. Enter 201<sub>8</sub> in switch register. The correct switch configuration for this is

000 010 000 001

Table 2-1

Test Program Error Code/Module Location Cross Reference

| Error<br>Code<br>Typed | Module<br>Location/<br>(Type)                           | Error<br>Code<br>Typed | Module<br>Location/<br>(Type)                                         |

|------------------------|---------------------------------------------------------|------------------------|-----------------------------------------------------------------------|

| **AA**                 | AB18 (M745)<br>A17 (M746)                               | **AJ**                 | AB24 (M740)<br>C23 (M746)                                             |

|                        | B17 (M746)<br>C17 (M746)<br>D17 (M746)                  | **AK**                 | D23 (M746)<br>Same as **AJ**                                          |

|                        | C18 (M746)                                              | **AL**                 | Same as **AJ**                                                        |

|                        | D18 (M746)<br>AB23 (M741)                               | **AM**                 | Same as **AJ**                                                        |

|                        | AB24 (M740)                                             | **AN**                 | Same as **AJ**                                                        |

|                        | C23 (M746)<br>D23 (M746)                                | **AO**                 | Same as **AJ**                                                        |

| **AB**                 | C19 (M747)                                              | **AP**                 | Same as **AJ**                                                        |

|                        | D19 (M747)<br>C18 (M746)                                | **AQ **                | Same as **AJ**                                                        |

|                        | D18 (M746)<br>AB24 (M740)<br>C23 (M746)<br>D23 (M746)   | **AR**                 | AB23 (M741)<br>AB24 (M740)<br>C23 (M746)<br>D23 (M746)                |

| **AC**                 | C21 (M746) D21 (M746) C18 (M746) D18 (M746) AB24 (M740) | **AS**                 | AB23 (M741)<br>CD22 (M744)<br>AB24 (M740)<br>C23 (M746)<br>D23 (M746) |

|                        | C23 (M746)<br>D23 (M746)                                | **AT**                 | Same as **AJ**                                                        |

| **AD**                 | C20 (M747)                                              | **AU**                 | Same as **AJ**                                                        |

|                        | D20 (M747)<br>C18 (M746)                                | **AV**<br>**AW**       | Same as **AJ** CD22 (M744)                                            |

|                        | D18 (M746) AB24 (M740) C23 (M746) D23 (M746)            |                        | AB24 (M740)<br>C23 (M746)<br>D23 (M746)                               |

| **AE**                 | Same as **AB**                                          | **AX**                 | Same as **AJ**                                                        |

| **AF**                 | Same as **AD**                                          | **AY**                 | Same as **AJ**                                                        |

| **AG**                 | Same as **AB**                                          | **AZ**                 | Same as **AJ**                                                        |

| **AH**                 | Same as **AD**                                          | **BA**                 | Same as **AJ**                                                        |

| **AI**                 | AB18 (M745)                                             | **BB**<br>**BC**       | Same as **AJ**                                                        |

|                        | AB23 (M741)<br>C19 (M747)                               | **BD**                 | Same as **AJ** Same as **AJ**                                         |

|                        | D19 (M747)                                              | **BE**                 | Same as **AJ**                                                        |

|                        | C18 (M746)<br>D18 (M746)                                | **BF**                 | Same as **AJ**                                                        |

|                        | AB24 (M740)<br>C23 (M746)<br>D23 (M746)                 | **BG**                 | Same as **AJ**                                                        |

Table 2-1 (Cont)

Test Program Error Code/Module Location Cross Reference

| Error<br>Code<br>Typed     | Module<br>Location/<br>(Type) | Error<br>Code<br>Typed | Module<br>Location/<br>(Type) |

|----------------------------|-------------------------------|------------------------|-------------------------------|

| **BH**                     | CD24 (M743)                   | **BP**                 | Same as **BO**                |

|                            | S Box†<br>AB22 (M742)         | **BQ **                | Same as **BH**                |

|                            | AB23 (M741)                   | **BR**                 | Same as **BO**                |

|                            | AB24 (M740)<br>C23 (M746)     | **BS**                 | Same as **BH**                |

|                            | D23 (M746)                    | **BT**                 | Same as **BO**                |

| **BI**                     | Same as **BH**                | **BU**                 | Same as **BO**                |

| **BJ**                     | CD24 (M743)                   | **BV**                 | Same as **BJ**                |

| 05                         | AB24 (M740)                   | **BW**                 | Same as **BO**                |

|                            | C23 (M746)<br>D23 (M746)      | **BX**                 | Same as **BH**                |

| **BK**                     | Same as **BJ**                | **BY**                 | Same as **BH**                |

| **BL**                     | Same as **BH**                | **BZ**                 | Same as **BJ**                |

| **BM**                     | AB22 (M742)                   | **CA**                 | Same as **BJ**                |

| 2                          | CD24 (M743)                   | **CB**                 | Same as **BH**                |

|                            | AB24 (M740)<br>C23 (M746)     | **CC**                 | Same as **BH**                |

|                            | D23 (M746)                    | **CD**                 | AB18 (M745)                   |

| **BN**                     | Same as **BH**                |                        | AB24 (M740)<br>C23 (M746)     |

| **BO**                     | AB23 (M741)                   |                        | D23 (M746)                    |

|                            | AB24 (M740)<br>C23 (M746)     | **CE**                 | C19 (M747)<br>D19 (M747)      |

|                            | D23 (M746)                    |                        | AB22 (M742)<br>AB24 (M740)    |

| <sup>†</sup> Refer to Para | ıgraph 2.3.2.                 |                        | C23 (M746)<br>D23 (M746)      |

| Step | Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 24   | Press the LOAD ADDRESS switch on test computer console. Test program will now be repeated without typing questions. If the same error code is typed as was typed during the previous test pass, substitute the module at the next location listed for that error code in Table 2-1. Continue to repeat this step until program types PASS COMPLETE (regardless of pass number). The module just substituted is defective and should be returned to the proper facility for repair. |  |  |

| 25   | If all modules have been substituted and the same error code is again typed, or if the program types something other than a two-letter error code flanked by asterisks, the control unit mainframe must be repaired off line, using information provided in Chapters 3 and 4 of this manual.                                                                                                                                                                                       |  |  |

| 26   | If the control unit and S-Boxes are functioning properly, proceed to Paragraph 2.3.2 to check the PDP-14 Program Storage modules.                                                                                                                                                                                                                                                                                                                                                  |  |  |

# 2.3.2 PDP-14 Storage Box Fault Isolation Procedure

The storage boxes are checked by the test computer during the procedure described in Paragraph 2.3.1 above. If error code \*\*BH\*\* (or any of the codes listed subsequently in Table 2-1 which refer to \*\*BH\*\*) is typed by the test computer, the control unit module at location CD24 should first be substituted.

If, upon repeating the test program, the same error code is printed, the following procedure should be performed to check out the suspected storage box:

| Step | Procedure                                                                                                                                                                                                                                                                                                                                                     |  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1    | Note the leftmost 4-digit number associated with the error code.                                                                                                                                                                                                                                                                                              |  |

| 2    | Locate this number in Table 2-2. (The numbers are listed in sets of 4.)                                                                                                                                                                                                                                                                                       |  |

| 3    | Note the mainframe location designator directly above the group of numbers in Table 2–2 which contains the printed number.                                                                                                                                                                                                                                    |  |

| 4    | Observe the S-Box connector inserted at this mainframe location. This connector should identify the S-Box with which it is associated.                                                                                                                                                                                                                        |  |

| 5    | Turn test computer and PDP-14 system OFF.                                                                                                                                                                                                                                                                                                                     |  |

|      | CAUTION                                                                                                                                                                                                                                                                                                                                                       |  |

|      | Failure to shut down test computer and PDP-14 System be-<br>fore removing or inserting modules can damage PDP-14<br>System components.                                                                                                                                                                                                                        |  |

| 6    | Remove the cover from the S-Box identified in step 4 by loosening eight 5/16 hex head screws which secure the cover to the S-Box shell.                                                                                                                                                                                                                       |  |

| 7    | Referring again to Table 2-2, substitute the module at the S-Box locations listed in the right-hand column, directly across from the group of numbers in the Table containing the number printed by the program (see Figure 2-4). Turn PDP-14 and test computer ON, and repeat the test (Paragraph 2.3.1) from step 16 until the defective module is located. |  |

Table 2-2

Test Program Address/S-Box Module Location Cross Reference Table

|                                          | locations. Up        | oper S-Box cal<br>/ D. | oles must be in       | serted in main       | frame row C a          | ind lower S-Bo   | vence in the mox cables must l | ainframe O-Box<br>be inserted in | Replace<br>S-Box<br>Module at   |

|------------------------------------------|----------------------|------------------------|-----------------------|----------------------|------------------------|------------------|--------------------------------|----------------------------------|---------------------------------|

|                                          | Upper S-Box C<br>C32 | Cable connect          | ed to Mainfrar<br>C30 | ne Module Loc<br>C29 | cation (see Fig<br>C28 | jure 2-3)<br>C27 | C26                            | C25                              | Location,<br>(Type)             |

| Leftmost                                 | 0000-0003            | 0040-0043              | 0100-0103             | 0140-0143            | 0200-0203              | 0240-0243        | 0300-0303                      | 0340-0343                        | A4(K207<br>B3(K161)<br>A2(K135  |

| 4-digit<br>number<br>typed by<br>program | 0004-0007            | 0044-0047              | 0104-0107             | 0144-0147            | 0204-0207              | 0244-0247        | 0304-0307                      | 0344-0347                        | B4(K207)<br>B3(K161)<br>A2(K135 |

| program                                  | 0010-0013            | 0050-0053              | 0110-0113             | 0150-0153            | 0210-0213              | 0250-0253        | 0310-0313                      | 0350-0353                        | A1(K207<br>B2(K161)<br>A2(K135  |

|                                          | 0014-0017            | 0054-0057              | 0114-0117             | 0154-0157            | 0214-0217              | 0254-0257        | 0314-0317                      | 0354-0357                        | B1(K207)<br>B2(K161)<br>A2(K135 |

|                                          | Lower S-Box 0<br>D32 | Cable connect<br>D31   | ed to Mainfran<br>D30 | me Module Loc<br>D29 | cation (see Fig<br>D28 | gure 2-3)<br>D27 | D26                            | D25                              |                                 |

| Leftmost                                 | 0020-0023            | 0060-0063              | 0120-0123             | 0160-0163            | 0220-0223              | 0260-0263        | 0320-0323                      | 0360-0363                        | C4(K207<br>C3(K161<br>D2(K135   |

| 4-digit<br>number<br>typed by<br>program | 0024-0027            | 0064-0067              | 0124-0127             | 0164-0167            | 0224-0227              | 0264-0267        | 0324-0327                      | 0364-0367                        | D4(K207<br>C3(K161<br>D2(K135   |

| program                                  | 0030-0033            | 0070-0073              | 0130-0133             | 0170-0173            | 0230-0233              | 0270-0273        | 0330-0333                      | 0370-0373                        | C1(K207<br>C2(K161<br>D2(K135   |

|                                          | 0034-0037            | 0074-0077              | 0134-0137             | 0174-0177            | 0234-0237              | 0274-0277        | 0334-0337                      | 0374-0376                        | D1(K207<br>C2(K161<br>D2(K135   |

# STORAGE BOX

Figure 2-4 Storage Box Module and Cable Connector Map, Front View

| Step | <u>Procedure</u>                                                                                                                                                                                                                                           |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8    | If the fault is not isolated, return to Table 2-1 and substitute the remaining control unit modules listed for the **BH** error code.                                                                                                                      |

| 9    | If the above procedure fails to isolate a defective module, turn all power off, remove all modules from the S-Box, and remove the S-Box connector panel by loosening six Phillips head screws slightly and sliding the panel from beneath the screw heads. |

| 10   | Substitute a properly functioning connector panel and replace all modules (see Figure 2–4).                                                                                                                                                                |

### 2.3.3 PDP-14 Read Only Memory Checkout Procedure

The control program for the machine system is stored within the PDP-14 Control Unit in Read Only Memory (ROM) modules (see Figure 2-3). Assuming that the PDP-14 and the test computer are already interconnected and that power is ON in both machines, the ROM modules are checked by the following procedure.

### NOTE

The PDP-14 Control Unit must be tested and found to be working properly, using the procedure in Paragraph 2.3.1, before testing the ROMs with this procedure.

| Step | <u>Procedure</u>                                                                                                                                                                                                                            |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Place PDP-14 START/STOP switch momentarily in STOP position.                                                                                                                                                                                |

| 2    | Set test computer SWITCH REGISTER to 77778. The switch configuration for this is                                                                                                                                                            |

| 3    | Press the LOAD ADDRESS switch on test computer.                                                                                                                                                                                             |

| 4    | Load the VER-14 paper tape into the test computer teleprinter paper tape reader as follows:                                                                                                                                                 |

|      | a. Set the reader START/STOP/FREE switch to the FREE position.                                                                                                                                                                              |

|      | b. Release the cover guard by means of the latch at the right and open cover.                                                                                                                                                               |

|      | <ul> <li>c. Insert the punched tape leader from the rear over the reader sprocket wheel so that the small holes in the tape engage the sprocket teeth and there are 3 hole spaces on the tape to the left of the sprocket wheel.</li> </ul> |

|      | d. Close reader cover.                                                                                                                                                                                                                      |

| 5    | Place paper tape reader START/STOP/FREE switch to START position.                                                                                                                                                                           |

| 6    | Press test computer START switch momentarily. Tape should now move through reader until completely read and only trailing portion remains in reader.                                                                                        |

|      | NOTE                                                                                                                                                                                                                                        |

|      | If tape stops before it has been completely read, place tape leader in reader and press test computer CONT                                                                                                                                  |

switch momentarily. If tape cannot be read, refer to Chapter 4 of this manual to reload the BIN tape.

| Step | Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | Remove the trailing portion of the VER-14 paper tape from the reader by releasing the cover guard with the latch and opening the reader cover. Lift the tape off the sprocket wheel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8    | Load the LOAD-14 paper tape into the test computer teleprinter paper tape reader using the procedure described in Step 4, above.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9    | Place the paper tape reader START/STOP/FREE switch to START position.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 10   | Press the test computer START switch momentarily. The tape should now move through reader until it is completely read and only the trailing portion remains in reader.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | NOTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | If the tape stops before it has been completely read, place the tape leader in reader and press the test computer CONT switch momentarily. If the tape cannot be read, refer to Chapter 4 of this manual to reload the BIN tape.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |