# DSV11 Communications Option Technical Description

Order Number. EK-DSV1M-TD-001

digital equipment corporation maynard, massachusetts

#### Fourth Draft, June 1988

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation.

Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software, if any, described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license. No responsibility is assumed for the use or reliability of software or equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Copyright ©1988 by Digital Equipment Corporation.

All Rights Reserved. Printed in U.S.A.

The postpaid READER'S COMMENTS form on the last page of this document requests the user's critical evaluation to assist in preparing future documentation.

The following are trademarks of Digital Equipment Corporation:

| BASEWAY   | MicroPDP-11   | RSX                |

|-----------|---------------|--------------------|

|           |               |                    |

| BI Bus    | Micro/RSTS    | RT                 |

| DEC       | Micro/RSX     | ThinWire           |

| DECmate   | MicroVAX II   | ULTRIX-32          |

| DECnet    | PDP           | UNIBUS             |

| DECUS     | P/OS          | VAX                |

| DECwriter | MicroVAX 3500 | VAXcluster         |

| DELNI     | MicroVAX 3600 | VAXELN             |

| DELQA     | Professional  | VAX station II     |

| DEQNA     | Q-bus         | VAX station II/GPX |

| DESTA     | Q22-bus       | VMS                |

| DIBOL     | Rainbow       | VT                 |

| MASSBUS   | RSTS          | Work Processor     |

|           |               |                    |

IBM is a trademark of International Business Machines PAL is a registered trademark of Monolithic Memories Inc.

FCC NOTICE: The equipment described in this manual generates, uses, and may emit radio frequency energy. The equipment has been type tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such radio frequency interference when operated in a commercial environment. Operation of this equipment in a residential area may cause interference, in which case the user at his own expense may be required to take measures to correct the interference.

| Ρ | re | fa | ce               |

|---|----|----|------------------|

|   |    |    | $\sim \sim \sim$ |

| ÷ | ÷., |

|---|-----|

| л | 1   |

| Chapter 1 OVERVIEW OF THE DSV11                   |       |

|---------------------------------------------------|-------|

| 1.1 General Description of the DSV11              | 1-1   |

| 1.1.1 Configurations                              | 1-2   |

|                                                   |       |

| Chapter 2 REGISTERS AND COMMANDS                  |       |

| 2.1 PROGRAMMING OVERVIEW                          | 2-1   |

| 2.2 DEVICE REGISTERS                              | . 2–1 |

| 2.2.1 Register Access                             | 2-1   |

| 2.2.2 Register Bit Definitions                    | 2–2   |

| 2.2.2.1 Flag Register (FLAG)                      | 2–2   |

| 2.2.2.2 Command Memory Address Register (CMAR)    | 2-4   |

| 2.2.2.3 Command Memory Data Register Low (CMDRL)  | 2-4   |

| 2.2.2.4 Command Memory Data Register High (CMDRH) | 2-4   |

| 2.3 COMMAND MEMORY                                | 2-5   |

| 2.4 COMMAND LIST STRUCTURE                        | 2-5   |

| 2.4.1 Overview                                    | 2-5   |

| 2.4.2 The Initialization Block                    | 2-6   |

| 2.4.3 The Command List                            | 2-8   |

| 2.4.4 The Response List                           | 2–8   |

| 2.5 COMMAND LIST ELEMENTS                         | 2-8   |

| 2.5.1 Command List Element Structure              | 2–8   |

| 2.5.1.1 Command List Link Address                 | 2-10  |

| 2.5.1.2 Response List Link Address                | 2-10  |

| 2.5.1.3 Function Longword                         | 2-10  |

| 2.5.1.4 Buffer Length Longword                    | 2-13  |

| 2.5.1.5 Buffer Address Longword                   | 2-13  |

| 2.5.1.6 Parameter Longwords                       | 2-13  |

| 2.6 COMMAND FUNCTIONS                             | 2-13  |

| 2.6.1 Return Device Parameters                    | 2-14  |

| 2.6.2 Return Channel Parameters                   | 2-14  |

| 2.6.3 Initialize Channel                          | 2-15  |

| 2.6.4 Change Channel Parameters                   | 2-17  |

| 2.6.5 Reset Channel                               | 2-17  |

| 2.6.6 Transmit Data                               | 2-18  |

| 2.6.7 Receive Data                                | 2-19  |

| 2.6.8 Update and Report Modern Status             | 2-21  |

|        | Report Status Change      |         |           |                 |                   |          |

|--------|---------------------------|---------|-----------|-----------------|-------------------|----------|

| 2.6.10 | Perform Diagnostic Action | • • • • | • • • • • | • • • • • • • • | <br>• • • • • • • | <br>2-24 |

# Chapter 3 PROGRAMMING PROCEDURES

| 3.1   | INITIALIZATION                           | 3-1  |

|-------|------------------------------------------|------|

| 3.2   | COMMAND LIST PROCESSING                  |      |

| 3.3   | MAINTENANCE PROGRAMMING                  | 3–9  |

| 3.3.1 |                                          |      |

| 3.3.2 |                                          | 3-10 |

| 3.4   | PROGRAMMING EXAMPLES                     | 3-12 |

| 3.4.1 | Process the Response List                | 3-13 |

| 3.4.2 |                                          | 3-13 |

| 3.4.3 | Adding a New Command to the Command List | 3-14 |

# Chapter 4 PHYSICAL DESCRIPTION

| 4.1     | VERSIONS          |         | • • • |     | • • • | •••••       |       | ••••• | • • • | • • • |       | ••••••• | • •  |       | • • | 4 | -1          |

|---------|-------------------|---------|-------|-----|-------|-------------|-------|-------|-------|-------|-------|---------|------|-------|-----|---|-------------|

| 4.1.1   | Serial Interfaces |         |       | • • |       | •••         |       |       |       | • • • | •••   | •••     | •••• | ••••  | • • | 4 | 1-2         |

| 4.1.1.1 | Line Receivers    | • • • • |       | ••• | • • • | • •         | • • • | • • • |       | •••   | • • • | •       | • •  | • • • | ••• | 4 | <b>₩</b> -3 |

| 4.1.1.2 | Line Transmitters |         | • • • | ••  |       | <pre></pre> | • • • |       | • • • | • • • | • • • | •       | •    | • • • | ••• | 4 | 1-3         |

# Chapter 5 FUNCTIONAL DESCRIPTION

| 5.1   | DATA TRANSFER        | 5-3 |

|-------|----------------------|-----|

|       | Q22-BUS INTERFACE    |     |

| 5.3   | Serial Interfaces    | 5-4 |

| 5.3.1 | Interface Comparison | 5-4 |

# Chapter 6 TECHNICAL DESCRIPTION

| 그는 것 같아요. 그는 것 같아요. 이는 것 같아요. | 1 1  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 6.1 SCOPE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6–1  |

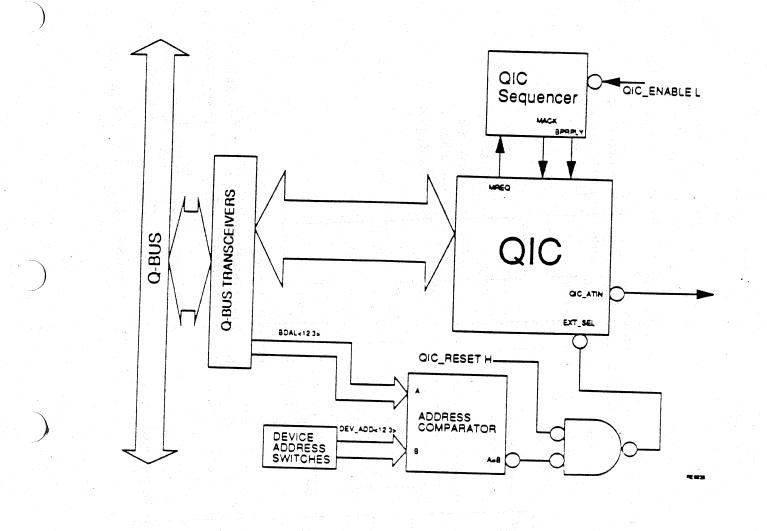

| 6.2 Q-BUS INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6–2  |

| 6.2.1 Bus Transceivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6-3  |

| 6.2.2 The QIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6-4  |

| 6.2.3 Address Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6-5  |

| 6.2.4 QIC-to-68000 Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6-7  |

| 6.2.5 QIC Backport Memory Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6-7  |

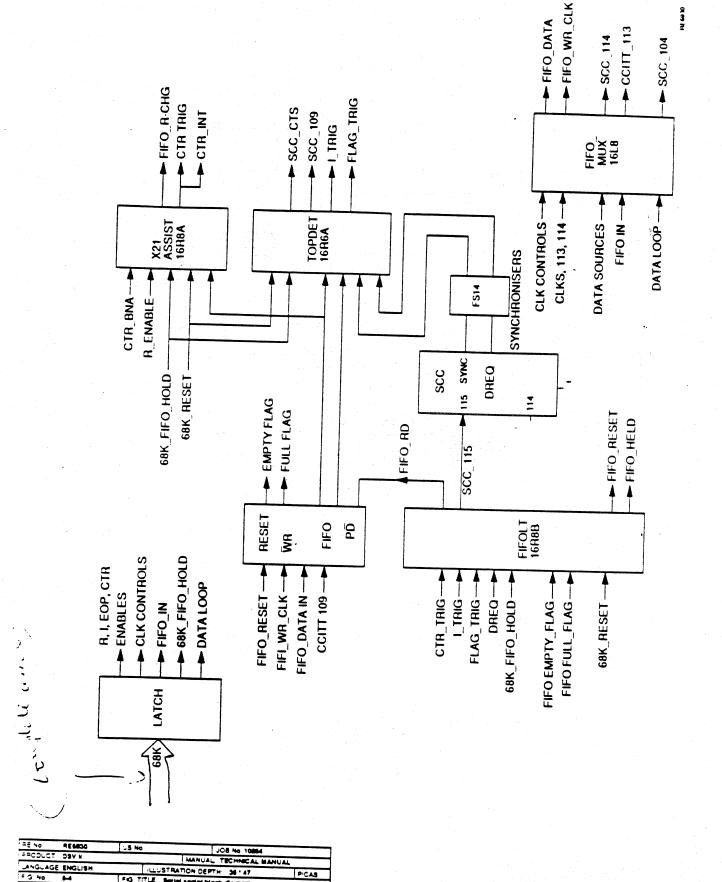

| 6.3 SERIAL INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6-7  |

| 6.3.1 Serial assist interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 68   |

| 6.3.1.1 Serial FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6-10 |

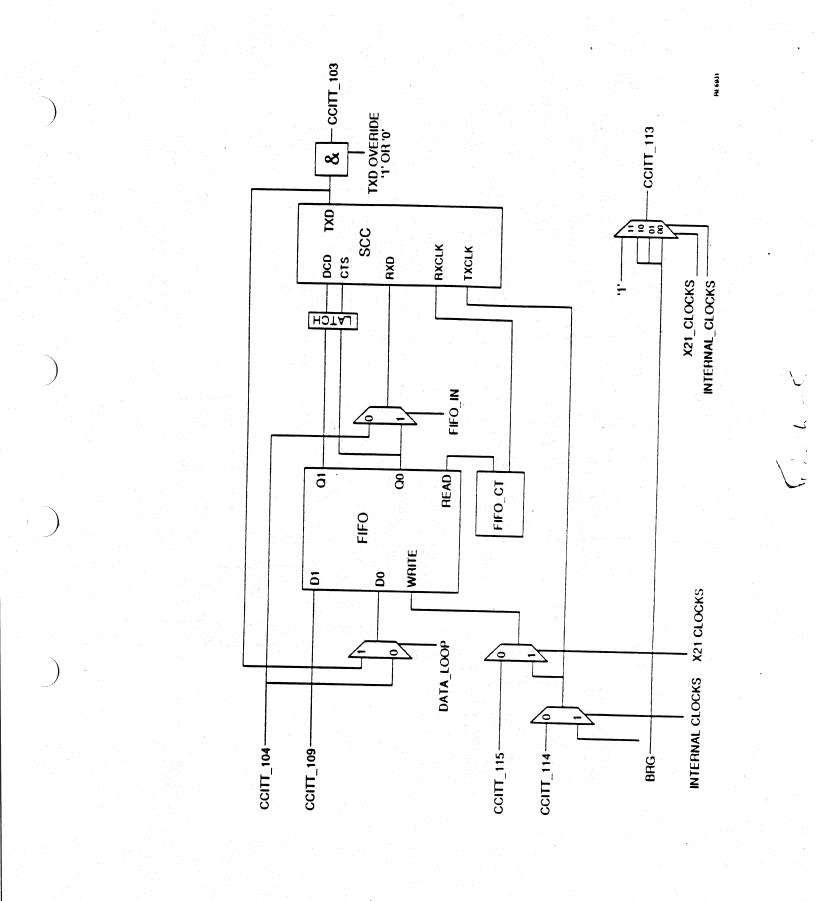

| 6.3.2 Data Path Multiplexing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6-10 |

| 6.3.3 Clock Path Multiplexing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6-12 |

| 6.3.3.1 EOP - End Of Packet Detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6–12 |

| 6.3.3.2 Serial Assist FIFO Control Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6-13 |

| 6.3.3.3 I-lead Transition Detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6-13 |

| 6.3.3.4 R-lead Transition Detector                             | 6-13 |

|----------------------------------------------------------------|------|

| 6.3.3.5 Serial Assist Counter                                  | 6-13 |

| 6.3.4 DMA Transfers                                            | 6-14 |

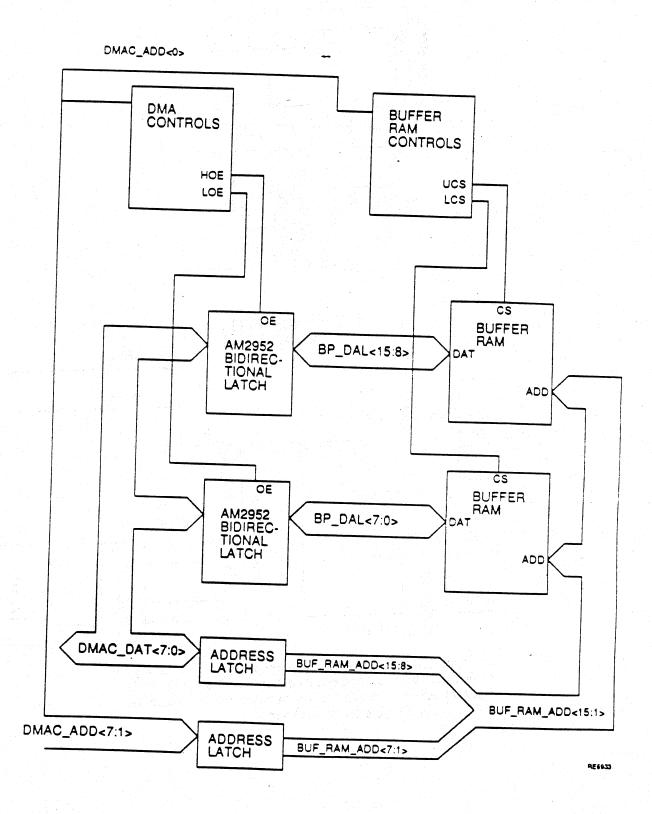

| 6.3.5 Byte-Word Multiplexer                                    | 6-16 |

| 6.3.6 Drivers and Receivers                                    | 6-18 |

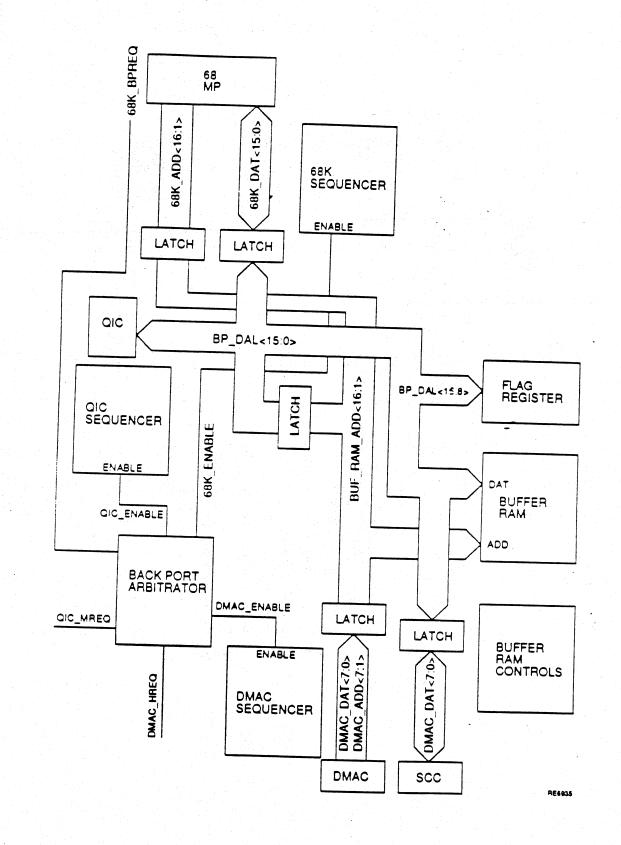

| 6.4 BACKPORT BUS                                               | 6-18 |

| 6.4.1 Buffer RAM                                               | 6-20 |

| 6.4.2 Command Memory Interface                                 | 6-20 |

| 6.4.3 The Flag Register                                        | 6-22 |

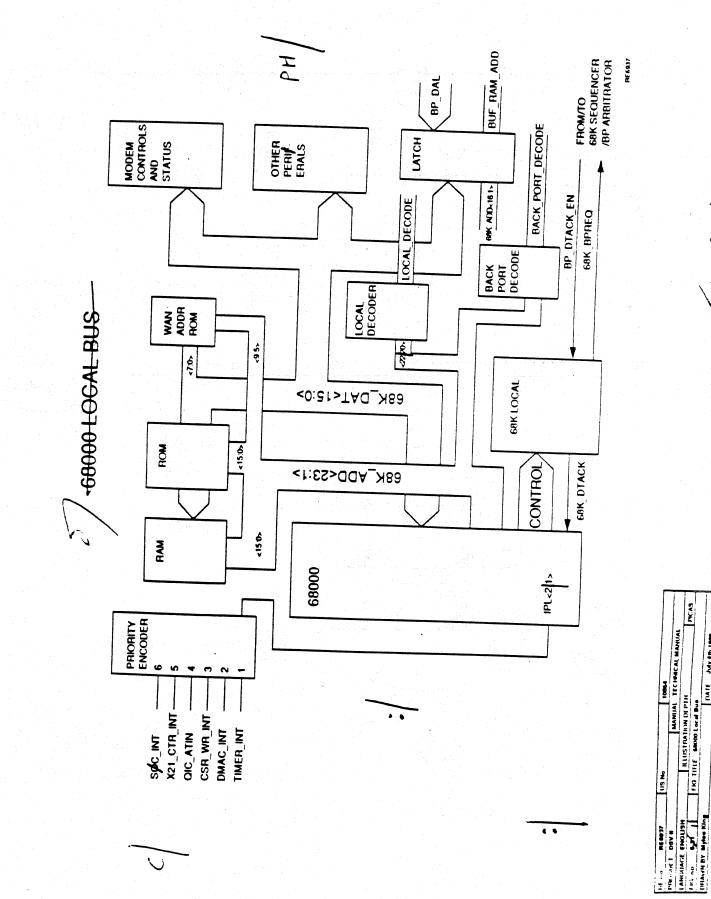

| 6.5 CONTROL SECTION                                            |      |

| 6.5.1 The 68000 Microprocessor                                 | 6–22 |

| 6.5.2 Address Decoding                                         | 6–22 |

| 6.5.3 68000 Microprocessor Accesses                            | 6–24 |

| 6.5.4 Interrupt Logic                                          | 6–24 |

| 6.5.5 Memory—ROM, RAM                                          | 6–25 |

| 6.5.6 Input/Output                                             | 6-25 |

| 6.5.6.1 Modem Status                                           | 6-25 |

| 6.5.6.2 Modem Control                                          | 6-25 |

| 6.5.6.3 Switches, I/O control and Cable Codes                  | 6–26 |

| 6.5.6.4 I/O Status Channel 0 - READ Address <500000>           | 6-26 |

| 6.5.6.5 Diagnostic and Driver Controls - WRITE address<600000> | 6-27 |

| 6.5.6.6 FIFO Reset - WRITE address <700000>                    | 6–27 |

| 6.6 The 68K_SEQUENCER                                          |      |

| 6.7 CLOCKS AND RESETS                                          | 6–28 |

| 6.7.1 Clocks                                                   | 6-29 |

| 6.7.2 Resets                                                   | 6-29 |

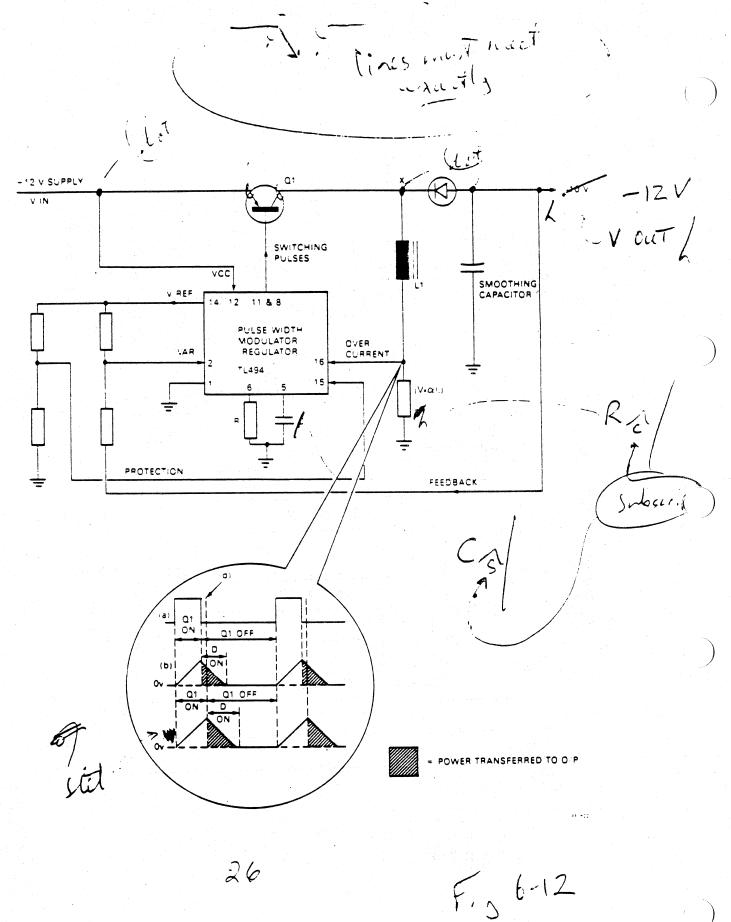

| 6.8 POWER SUPPLIES                                             | 6-30 |

| 6.8.1 DC-to-DC Converter                                       | 6-30 |

# Chapter 7 MAINTENANCE AND DIAGNOSTIC INFORMATION

| 7.1 SCOPE                             | 7–1 |

|---------------------------------------|-----|

| 7.2 MAINTENANCE STRATEGY              | 7-1 |

| 7.2.1 Preventive Maintenance          | 7-1 |

| 7.2.2 Corrective Maintenance          | 7–1 |

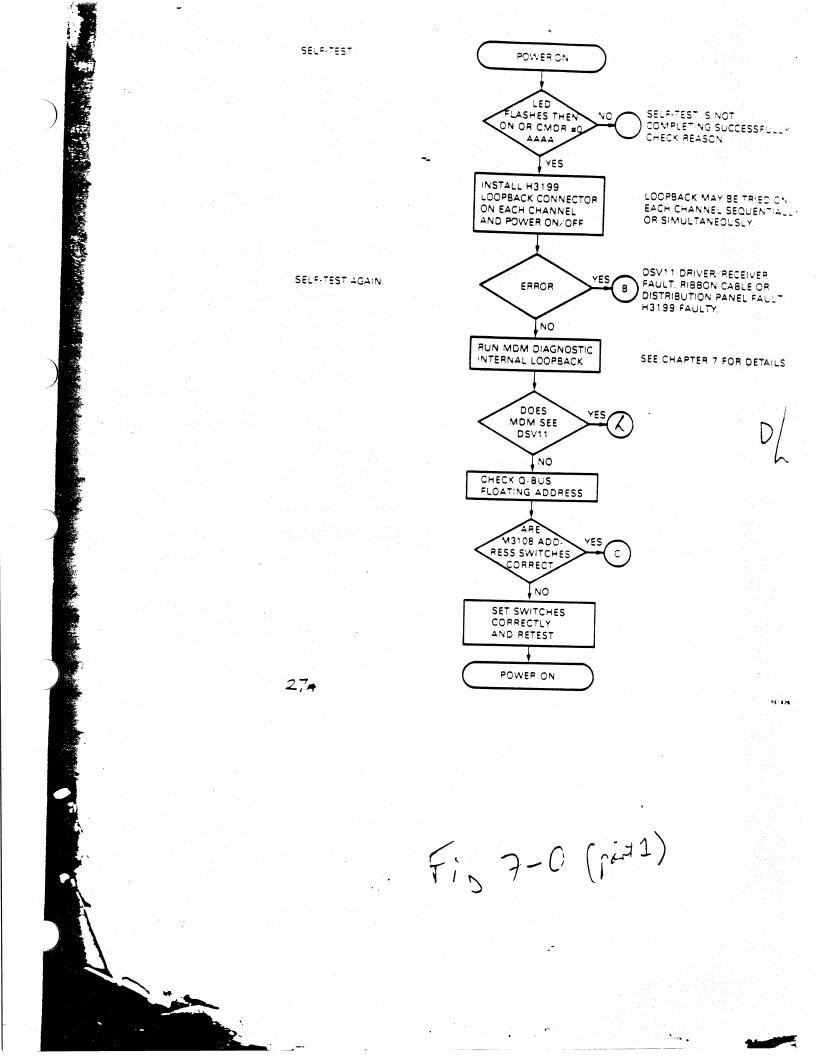

| 7.3 SELF-TEST                         | 7–1 |

| 7.4 MicroVAX DIAGNOSTICS              | 7–2 |

| 7.4.1 MDM Diagnostics                 | 7-2 |

| 7.4.1.1 Verify Mode Testing           | 7–2 |

| 7.4.1.2 Verify Mode Functional Tests  | 7–2 |

| 7.4.1.3 Verify Mode Exerciser Test    | 7-3 |

| 7.4.1.4 Service Mode Testing          | 7–3 |

| 7.4.1.5 Service Mode Functional Tests | 7–3 |

| 7.4.1.6 Service Mode Exerciser Test   | 7-4 |

| 7.4.1.7 Cable Test Utility            | 7-4 |

| 7.4.2 Running the MDM Diagnostics  |      |

|------------------------------------|------|

| 7.4.2.1 Running Service Mode Tests | 7-4  |

| 7.4.2.2 Running Utility Tests      | 7–5  |

| 7.4.3 Example Printouts            |      |

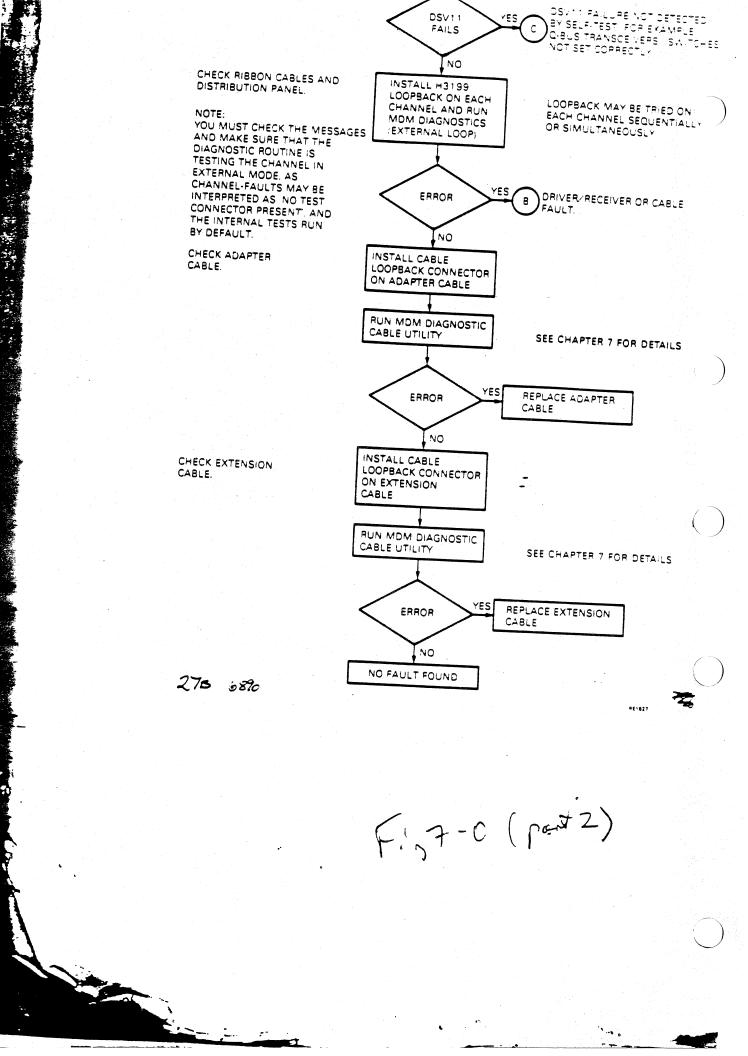

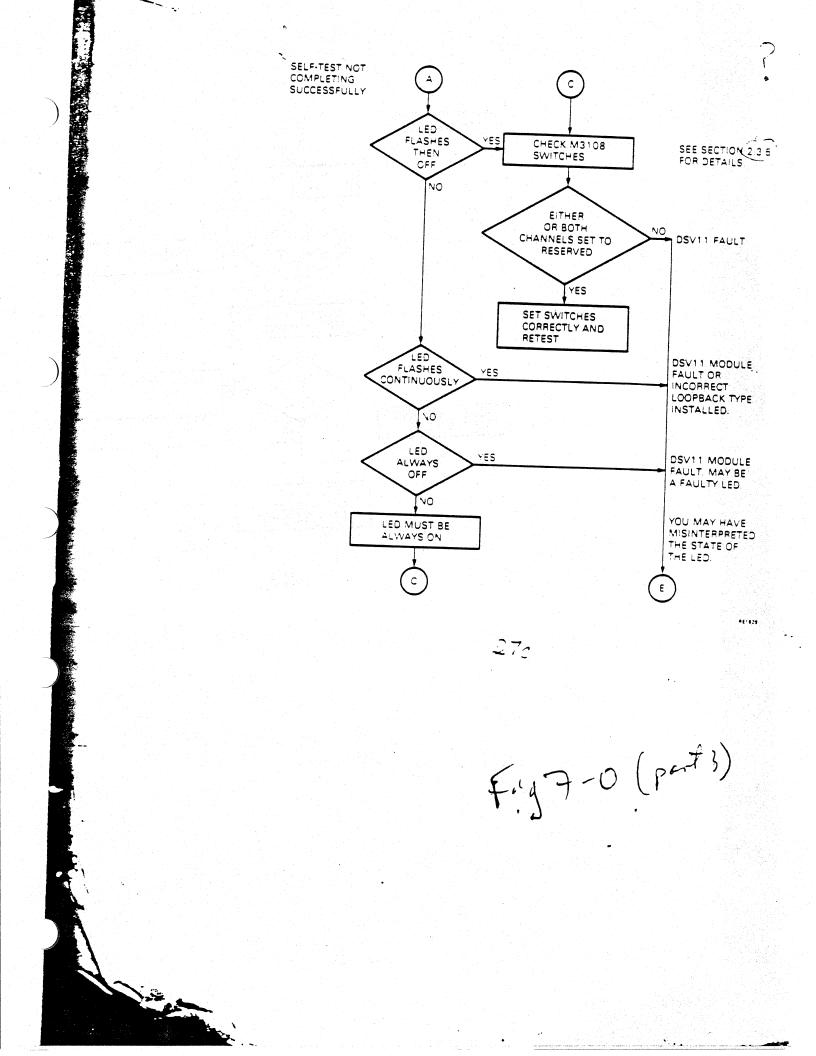

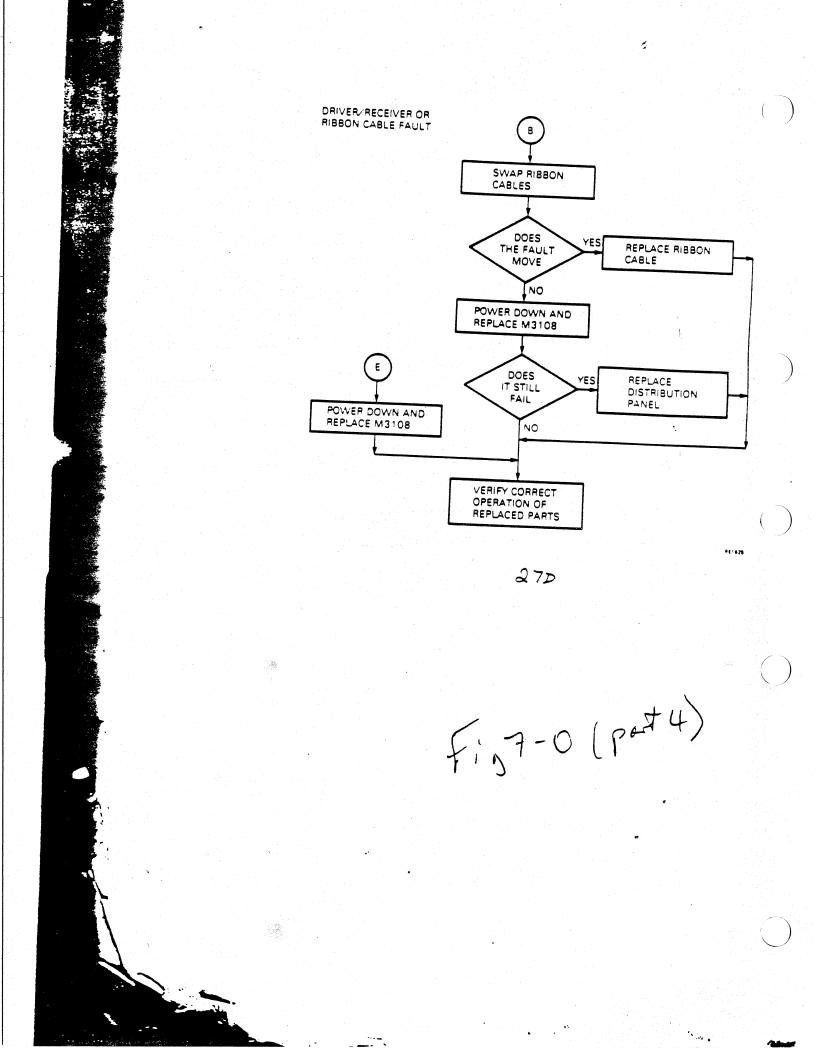

| 7.5 TROUBLESHOOTING PROCEDURE      | 7–11 |

| 7.6 TROUBLESHOOTING NOTES          | 7–12 |

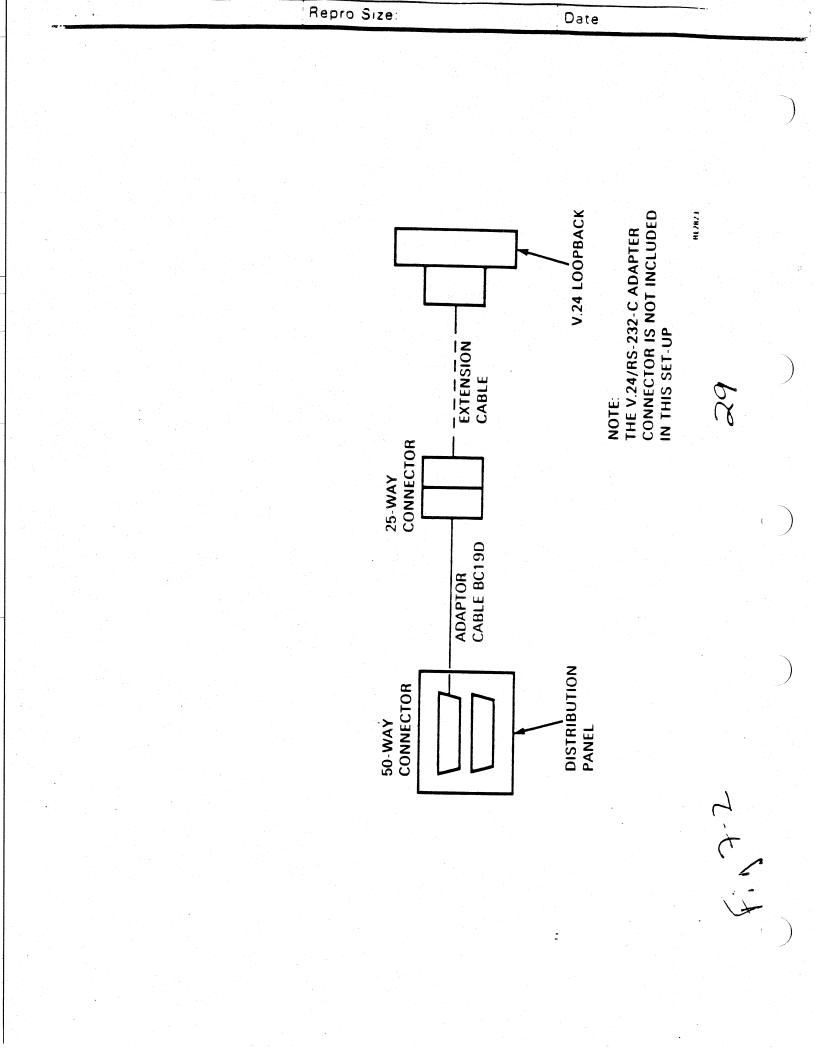

| 7.6.1 Cable Loopback Limitations   | 7–12 |

| 7.6.2 Diagnostic Limitations       |      |

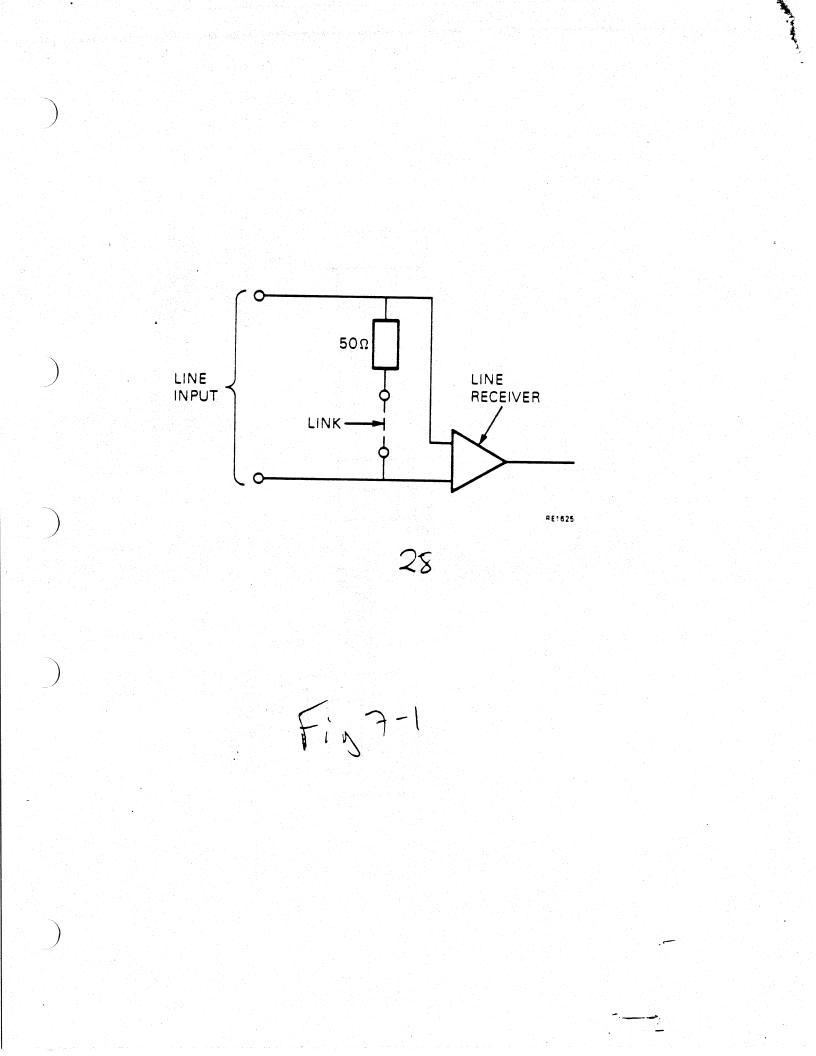

| 7.6.3 RS-423 Modems                | 7–12 |

| 7.6.4 RS-449                       |      |

| 7.6.5 Testing Ribbon Cables        | 7–13 |

| 7.6.6 V.24 Cable Tests (BC19D)     | 7–14 |

| 7.6.7 NCP Loop Testing             | 7–15 |

| 7.7 FIELD-REPLACEABLE UNITS (FRUs) | 7-16 |

# Appendix A PROTOCOL DETAILS

| A.1 | SDLC/HDLC |                                     | A-1 |

|-----|-----------|-------------------------------------|-----|

| A.2 | DDCMP     | · · · · · · · · · · · · · · · · · · | A-2 |

| A.3 | BISYNC    |                                     | A-3 |

# Appendix B SPECIFICATIONS

| B.1 PHYSICAL DESCRIPTION                                       | B-1 |

|----------------------------------------------------------------|-----|

| B.2 ENVIRONMENTAL CONDITIONS                                   | B-1 |

| B.3 ELECTRICAL REQUIREMENTS                                    | B-1 |

| B.4 INTERFACES                                                 | B-1 |

| B.4.1 System Bus Interface                                     | B-1 |

| B.4.2 Serial Interfaces                                        | B-1 |

| B.4.2.1 Interface Standards                                    | B-2 |

| B.5 ELECTRICAL COMPATIBILITY                                   | B-2 |

| B.6 PERFORMANCE                                                | B-3 |

| B.6.1 Data Rates                                               | B-3 |

| B.6.2 Throughput                                               | B-3 |

| B.7 INTERCHANGE CIRCUITS AND THEIR ELECTRICAL CHARACTERISITICS | B-4 |

# Appendix C IC DESCRIPTIONS

| C.1   | SCOPE                                  | C-1 |

|-------|----------------------------------------|-----|

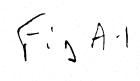

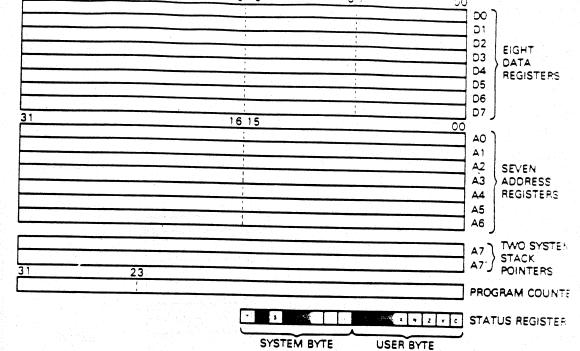

|       | 68000 MICROPROCESSOR                   |     |

| C.2.1 | Overview                               | C-1 |

|       | Signals and Pinout                     |     |

|       | 8530A SERIAL COMMUNICATIONS CONTROLLER |     |

| C.3.1 | Overview                               | C-7 |

|       | Signals and Pinout                     |     |

| C.4 82 | 37A-5 DMA CONTROLLER | Z-11 |

|--------|----------------------|------|

| C.4.1  | Overview             | 2-12 |

| C.4.2  | Signals and Pinout   | C-14 |

## Appendix D THE Q-BUS INTERFACE CHIP (QIC)

| D.1   | SCOPE                    | D-1 |

|-------|--------------------------|-----|

| D.2   | INTRODUCTION             | D-1 |

| D.3   | SIGNAL DESCRIPTION       | D-2 |

| D.4   | QIC REGISTERS            | D-4 |

| D.4.1 | QIC Register Addressing  | D-4 |

| D.4.2 | QIC Register Definitions | D-6 |

## Appendix E CONNECTORS AND CABLES

| E.1 DATA RATE TO CABLE LENGTH RELATIONSHIPS | E-1 |

|---------------------------------------------|-----|

| E.1.1 RS-232-C/V.24 Incompatibility         | E-4 |

| E.2 Adapter Cables                          | E6  |

## Appendix F FLOATING ADDRESSES

| F.1 | FLOATING DEVICE ADDRESSES | -1 |

|-----|---------------------------|----|

| F.2 | FLOATING VECTORS F        | -5 |

## Appendix G GLOSSARY OF TERMS

| G.1 | SCOPE    |           | <br>• • |      | • • • | • • • | <br>•••   | n sin<br>Airth |       | • • • • |       | • • • |         | G-1 |

|-----|----------|-----------|---------|------|-------|-------|-----------|----------------|-------|---------|-------|-------|---------|-----|

| G.2 | GLOSSARY | • • • • • | <br>    | •••• | •     | • • • | <br>• • • | • • •          | • • • | • • • • | • • • | •     | • • • • | G-1 |

### Index

## Examples

| 7–1 | Successful Pass of All Service Mode Functional Tests | 7-6  |

|-----|------------------------------------------------------|------|

| 7–2 | Running the Service Mode Exerciser Test              | 7-7  |

| 7–3 | Successful Pass of the Cable Test Utility            | 7–8  |

| 7-4 | Repairing a Fault with the Cable Test Utility        | 7–8  |

| 7–5 | Failing Pass of Badly Damaged Adapter Cable          | 7–10 |

| Characterization |                                        |

|------------------|----------------------------------------|

| 1-1              | Example of DSV11 Configuration         |

| 2-1              | DSV11 Flag Register                    |

| 2-2              | DSV11 Softload Operation Sequence      |

| 2-3              | DSV11 Command List Element Structure . |

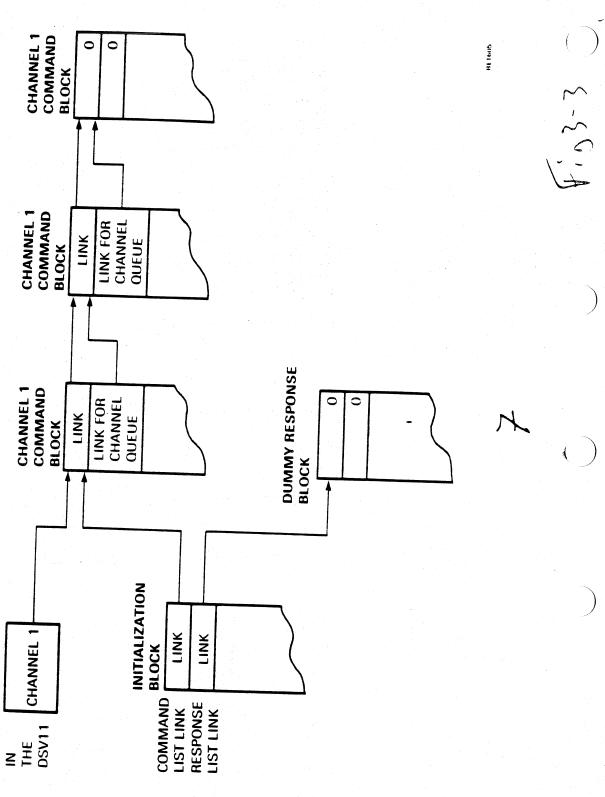

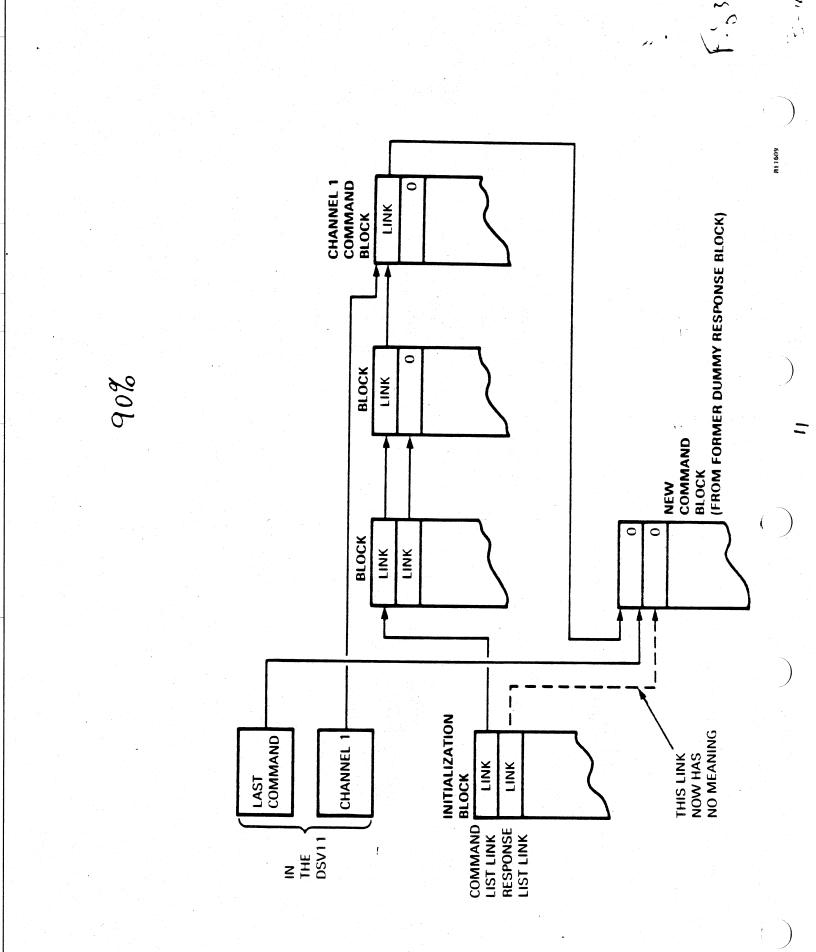

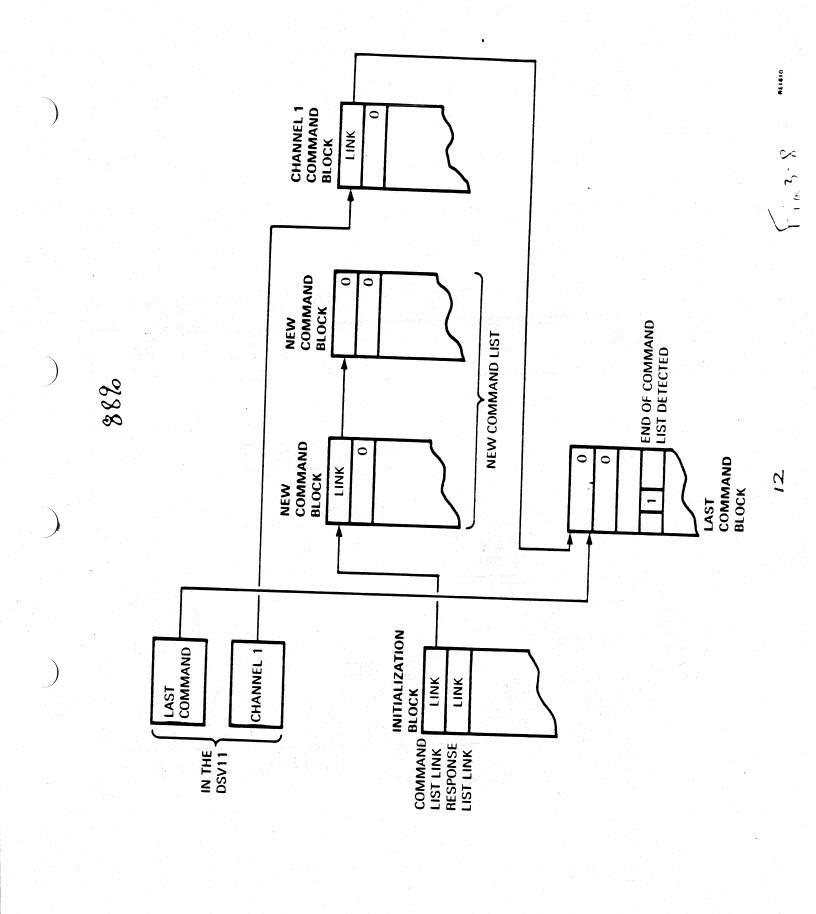

| 3-1              | Command List Structure (1)             |

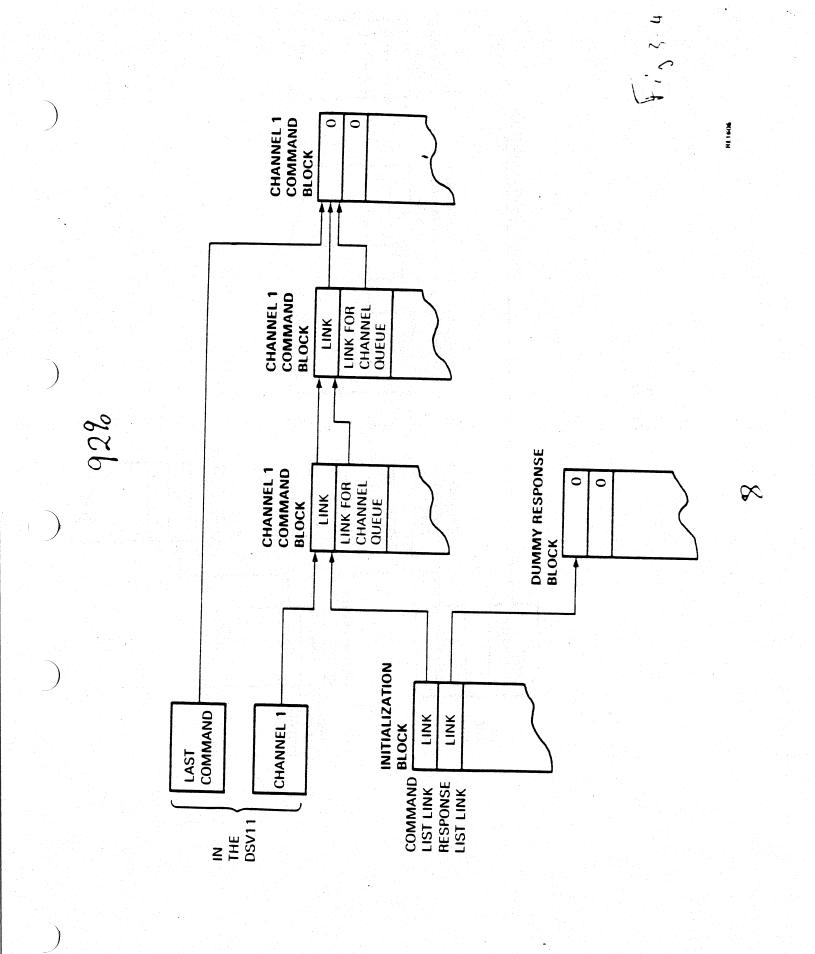

| 3-2              | Command List Structure (2)             |

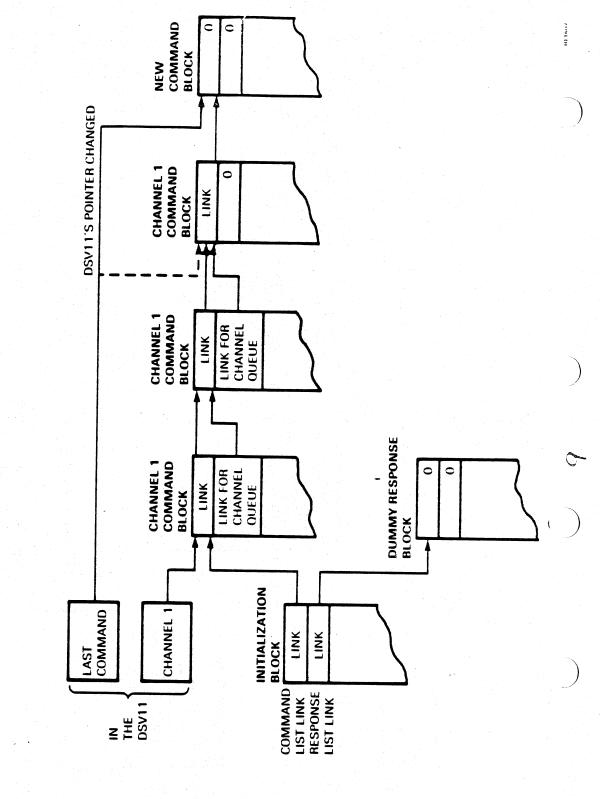

| 3-3              | Command List Structure (3)             |

| 3-4              | Command List Structure (4)             |

| 3-5              | Command List Structure (5)             |

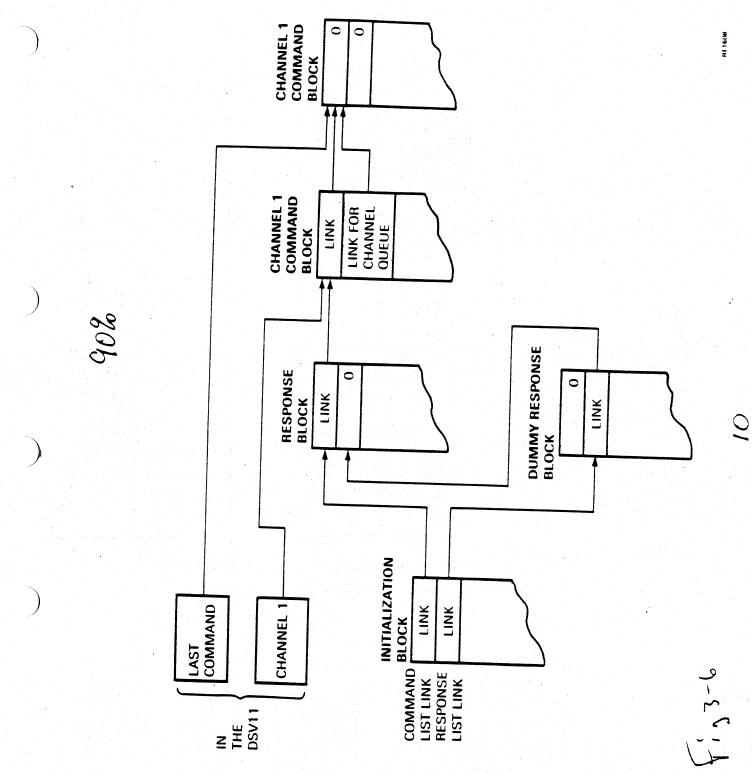

| 36               | Command List Structure (6)             |

| 3–7              | Command List Structure (7)             |

| 3-8              | Command List Structure (8)             |

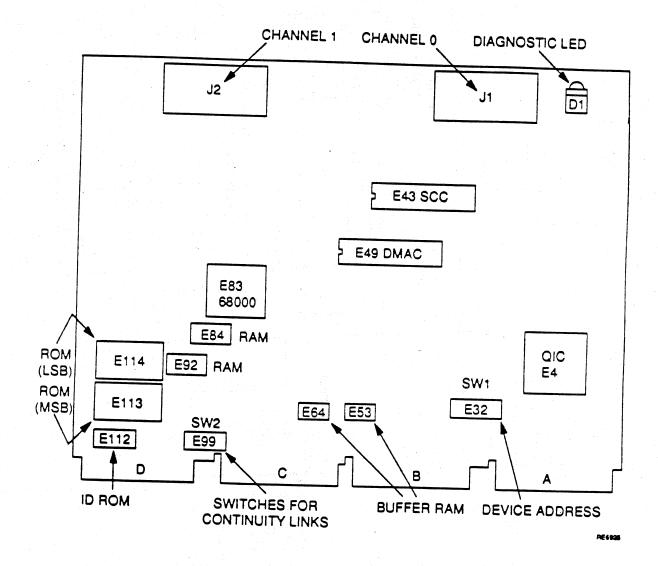

| 4-1              | M3108 Module                           |

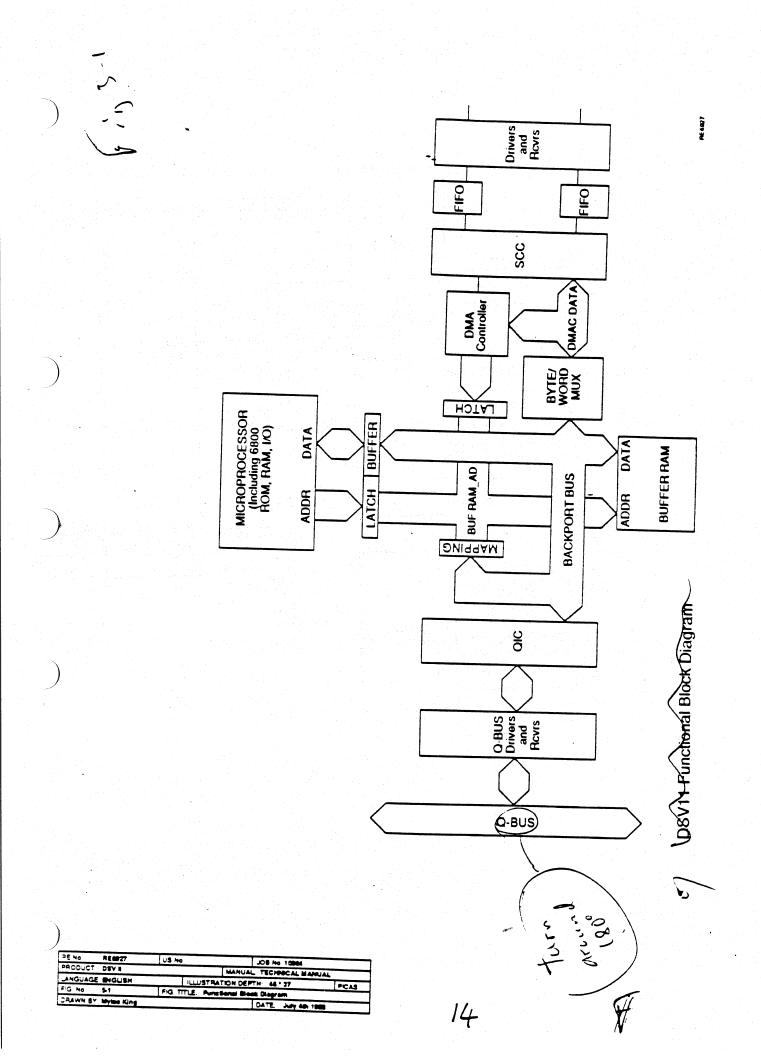

| 5-1              | DSV11 Functional Block Diagram         |

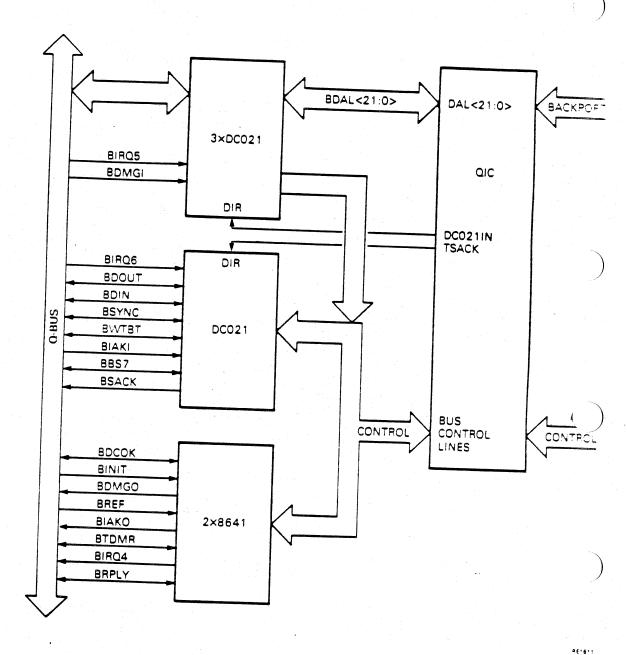

| 6-1              | DSV11 Block Diagram                    |

| 6-2              | Q-bus Transceivers                     |

| 6-3              | Q-bus Address Decoding                 |

| 6-4              | Serial Assist Block Diagram            |

| 6-5              | DSV11 Serial Data and Clock Paths      |

Figures

| 1-1  |                                       | 1-5         |

|------|---------------------------------------|-------------|

| 2-1  | DSV11 Flag Register                   | 2–2         |

| 2-2  | DSV11 Softload Operation Sequence     | 2-6         |

| 2-3  | DSV11 Command List Element Structure  | 2-9         |

| 3-1  | Command List Structure (1)            | 3–2         |

| 3-2  | Command List Structure (2)            | 3-3         |

| 3-3  | Command List Structure (3)            | 3-4         |

| 3-4  | Command List Structure (4)            | 3-5         |

| 3-5  | Command List Structure (5)            | 3-6         |

| 36   | Command List Structure (6)            | 3–7         |

| 3–7  | Command List Structure (7)            | 3-8         |

| 38   | Command List Structure (8)            | 3-9         |

| 4-1  | M3108 Module                          | 4-2         |

| 5-1  | DSV11 Functional Block Diagram        | 5-2         |

| 6-1  | DSV11 Block Diagram                   | 6-2         |

| 6-2  | Q-bus Transceivers                    | 6-4         |

| 6-3  | Q-bus Address Decoding                | 66          |

| 6-4  | Serial Assist Block Diagram           | 69          |

| 6-5  | DSV11 Serial Data and Clock Paths     | 6-11        |

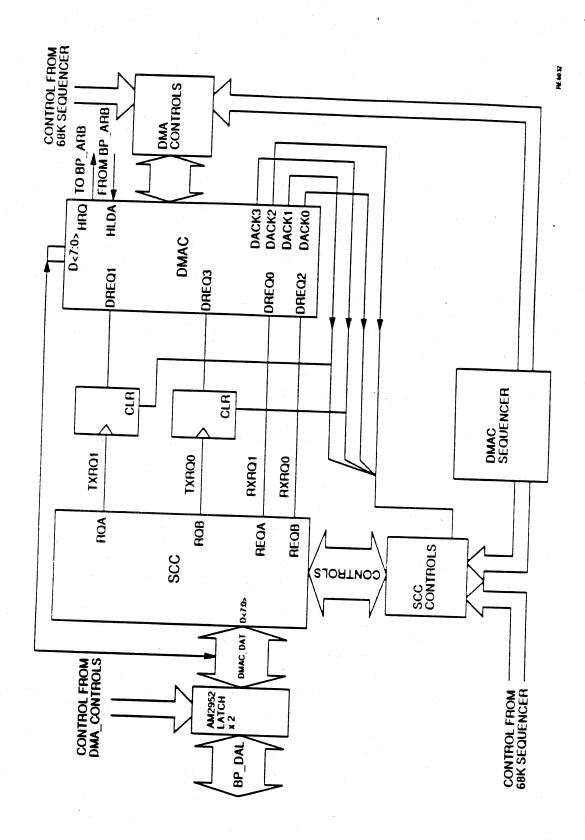

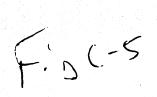

| 66   | The SCC and DMAC                      | 6-15        |

| 6-7  | The Byte-Word Multiplexer             | 6-17        |

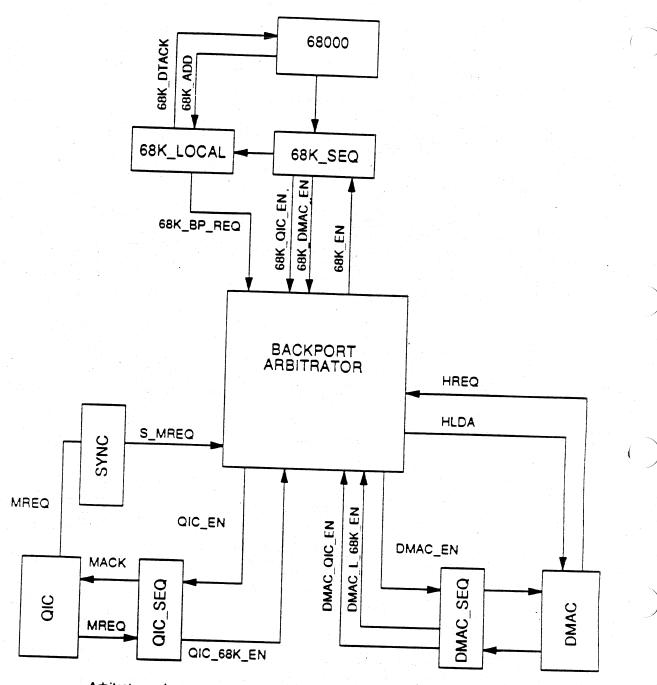

| 6-8  | DSV11 Backport Arbitration            |             |

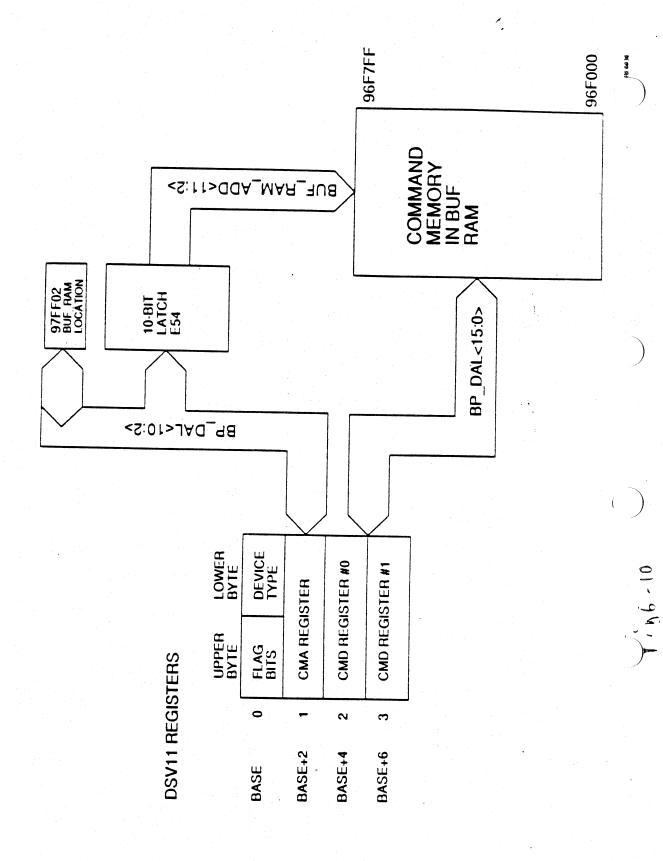

| 6-9  | Command Memory Interface              | 6-21        |

| 6–10 | 68000 Local Bus                       | 6-23        |

| 6–11 | The Backport Bus                      | 6-28        |

| 6-12 | DC-DC Converter                       | 6-31        |

| 7–1  | Typical RS-423 Modem Receiver Circuit | 7-13        |

| 7–2  | Testing the V.24 Adapter Cable        | 7-15        |

| C-1  | 68000 Internal Registers              | C-2         |

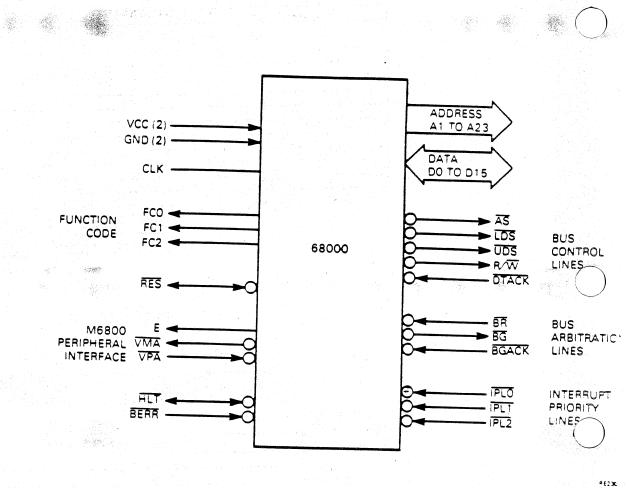

| C-2  | 68000 Input/Output Signals            | C-3         |

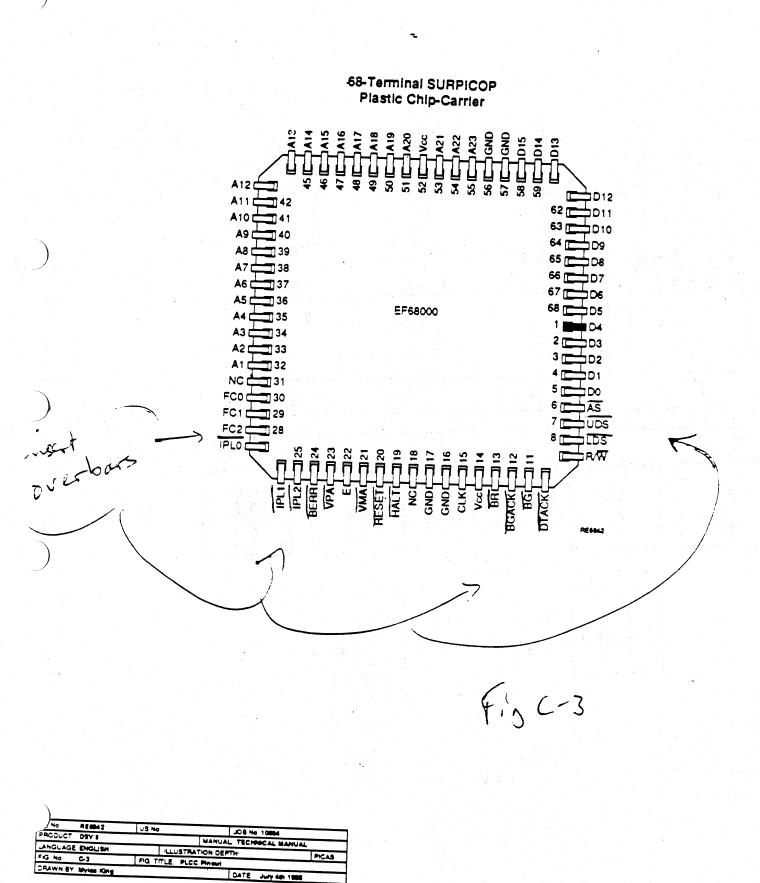

| C-3  | PLCC Pinout                           | C-4         |

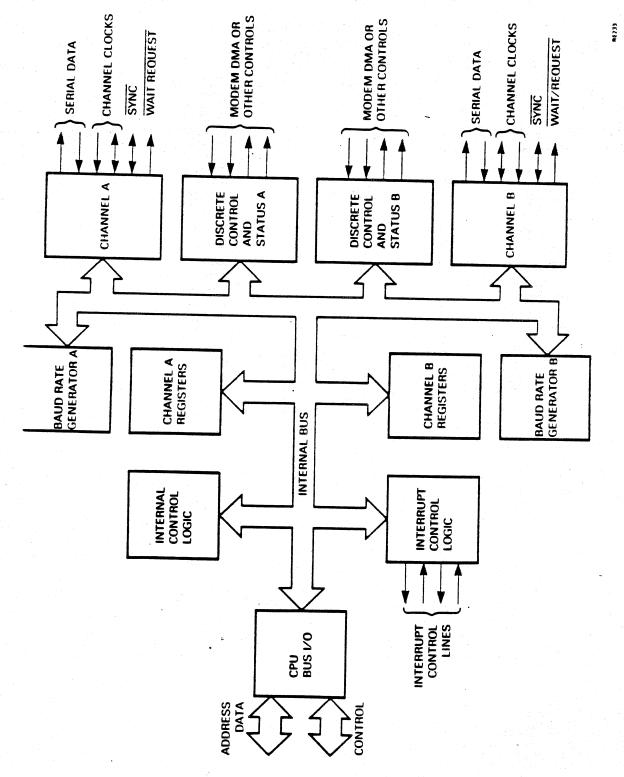

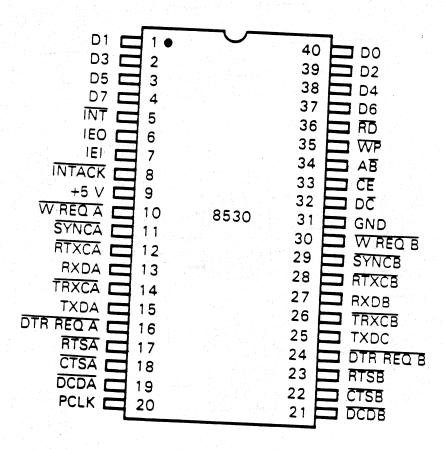

| C-4  | 8530A Architecture                    | C8          |

| C-5  | 8530A Pinout                          | C-10        |

| C6   | 8237A-5 Architecture                  | C-13        |

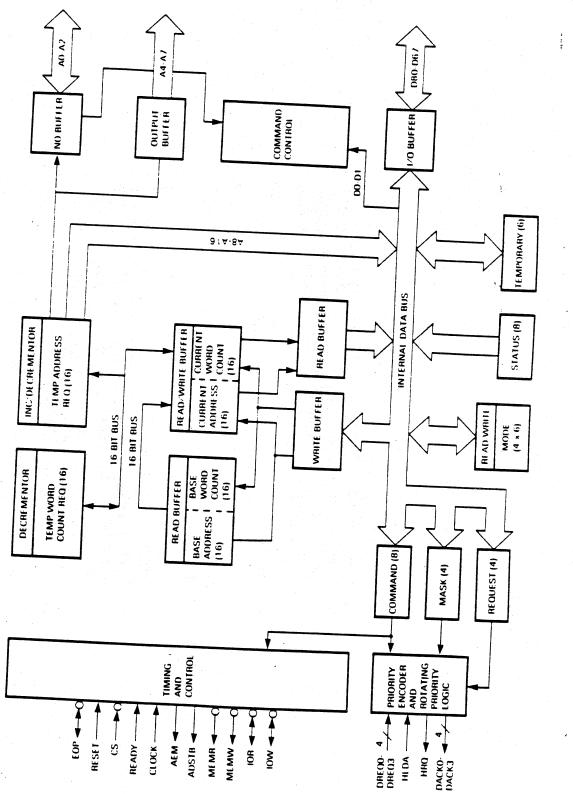

| C-7  | 8237A-5 Pinout                        | <b>C-14</b> |

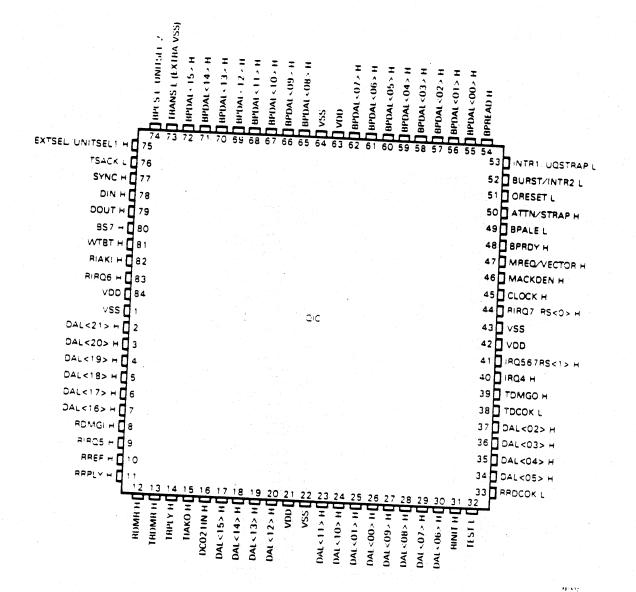

| D-1  | QIC Pinout Diagram                    | D-4         |

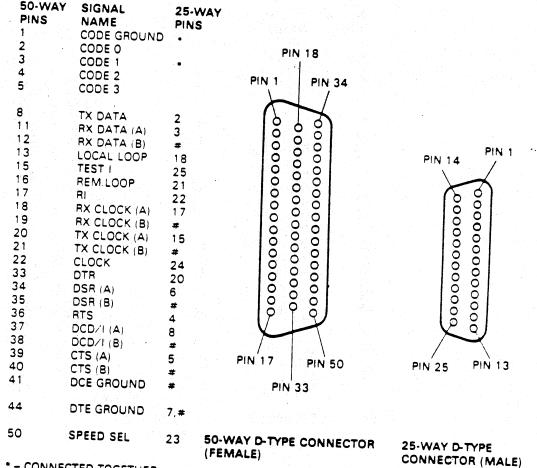

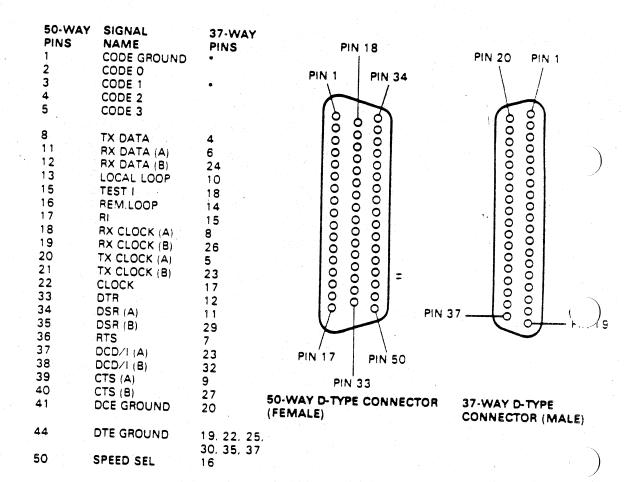

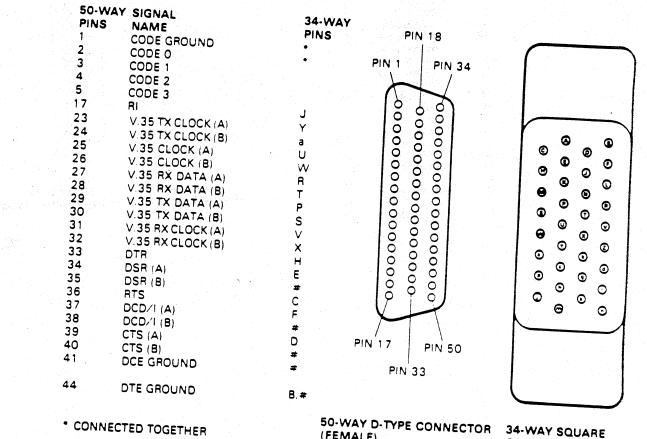

| E-1  | 50-way Sync Connector Pinout          | E2          |

| E-2  | RS-422/V.36 Adapter Cable             | E-7         |

| E-3  | RS-232-C/V.24 Adapter Cable           | E8          |

| E-4  | RS-423 Adapter Cable                  | E-9         |

V.24/RS-232-C Connector .....

E-10

E-11

E--5 E--6

# Tables

| 2-1 | DSV11 Registers                      | 2-2          |

|-----|--------------------------------------|--------------|

| 3-1 | Self-Test Error Codes                | 3-10         |

| 4-1 | Line Receiver Devices                | 4-3          |

| 4-2 | Line Transmitter Devices             | 4-3          |

| 5-1 | ELA/CCITT Signal Relationships       | 5-4          |

| 6-1 | Clock Multiplexing                   |              |

| 6-2 | 68000 Address Space                  | 6–24         |

| 6–3 | Cable Codes                          |              |

| 7–1 | Adapter Cables and Loopbacks         | 7-4          |

| 7–2 | Loopback Connector Limitations       | 7-12         |

| 7–3 |                                      | 7-16         |

| 7-4 | Adapter Cables                       | 7-17         |

| 7-5 | Extension Cables                     | 7-17         |

| A-1 | BISYNC Control Sequence Coding       | A-3          |

| B-1 | Maximum Supported Speeds (K bits/s)  | <b>B-</b> 3  |

| B-2 | DSV11 Interchange Circuits           | В-∠          |

| B-3 | DSV11 Electrical Characteristics     | Б-5          |

| C-1 | 68000 Signal Descriptions            | C-5          |

| C-2 | 8530A Register Summary               | C-9          |

| C-3 | 8530A Signal Descriptions            | <b>C-1</b> 0 |

| C-4 | 8237A-5 Signal Descriptions          | C-15         |

| D-1 | Signal Description                   | D-2          |

| D-2 |                                      | D-6          |

| E-1 | Data-Rate/Cable-Length Relationships | E-3          |

| E-2 | Extension Cables                     | E4           |

| E-3 | RS-232-C/V.24 Incompatibility        | E-4          |

| F-1 | Floating Device Address Assignments  | F-1          |

| F-2 |                                      |              |

| F-3 | Floating Vector Address Assignments  | F-5          |

# Preface

### INTRODUCTION

This guide is a complete technical description of the DSV11 device, and is intended for hardware engineers. field service engineers, and programmers. It provides a full description of the DSV11 device, detailing all DSV11 features and facilities.

## ASSOCIATED DOCUMENTS

The DSV11-M Communications Option Installation Guide (EK-DSV1M-IN) tells you how to install the DSV11-M board in a MicroVAX enclosure.

DSV11-M Communications Option User Guide (EK-DSV1M-UG) tells you how to connect the DSV11-M to a modem.

DSVII-SF Communications Option Installation Guide (EK-DSVI1-IN) tells you how to install the DSVI1-S board in a BA200 series enclosure.

DSV11-S Communications Option User Guide (EK-DSV11-UG) tells you how to connect the DSV11-S to a modem.

# STRUCTURE OF THIS GUIDE

The guide is divided into seven chapters and seven appendixes:

Chapter 1-Introduces and describes the DSV11.

Chapter 2-Describes the registers and commands associated with a DSV11.

Chapter 3-Describes programming procedures.

Chapter 4-Gives a physical description of the DSV11.

Chapter 5-Gives a functional description of the DSV11.

Chapter 6-Gives a technical description of the DSV11.

Chapter 7-Gives maintenance and diagnostic information.

Appendix A-Describes protocol details.

Appendix B—Gives line specifications for the DSV11.

Appendix C-Details the IC descriptions used on the DSV11.

Appendix D-Describes the Q-bus interface chip.

Appendix E-Describes the connectors and cables used on the DSV11.

Appendix F-Describes Floating Addresses.

Appendix G-Is a glossary of terms used in the manual.

# Chapter 1 OVERVIEW OF THE DSV11

## 1.1 General Description of the DSV11

The DSV11 is a synchronous communications controller for Q22-bus systems. It can handle two independent lines simultaneously running at different speeds and with different protocols.

The DSV11 is available in two forms:

- DSV11-S is suitable for insertion in BA200 series enclosures. One quad sized module contains all the active circuitry and line drivers/receivers.

- DSV11-M is suitable for insertion in BA23, BA123, and H9642 enclosures. In this form the DSV11 consists of a module and a distribution panel which are interconnected by ribbon cables.

The DSV11 controller provides the following features:

• Full compatibility with these interface standards:

RS-232-C, RS-232-D, RS-422, RS-423 V.10, V.11, V.24, V.28, V.35, V.36

- The DSV11 has full modern control, including the secondary test leads; Local Loop, Remote Loop, and Test Indicate (CCITT 140, 141, and 142 respectively)

- The DSV11 supports the following synchronous protocols:

DDCMP HDLC (single and double byte addressing) SDLC IBM BISYNC

(SDLC is a subset of HDLC single byte). The DSV11 performs 16-bit CRC generation and checking for each of these protocols.

A microprocessor controls the internal operation of the DSV11. ROM based diagnostics, running on the microprocessor, extensively test the module each time it is powered on or reset. An MDM diagnostic program for MicroVAX systems is also available.

The DSV11 interfaces directly to both the Q- and Q22-buses. Two switches select bus grant continuity for use with Q/Q and Q/CD backplanes. Switches on the module select the Q22-bus base address. All other DSV11 functions and configurations are programmable.

Data is transferred between the memory of the host system and the DSV11's internal data buffers by DMA transfer. Command blocks are used to send instructions to, and receive responses from, the DSV11. Command blocks and responses reside in DSV11 memory and are read and written by the host via three of the registers. The DSV11 has four registers in the Q22-bus I/O space which are used to initiate and monitor command block processing.

# 1.1.1 Configurations

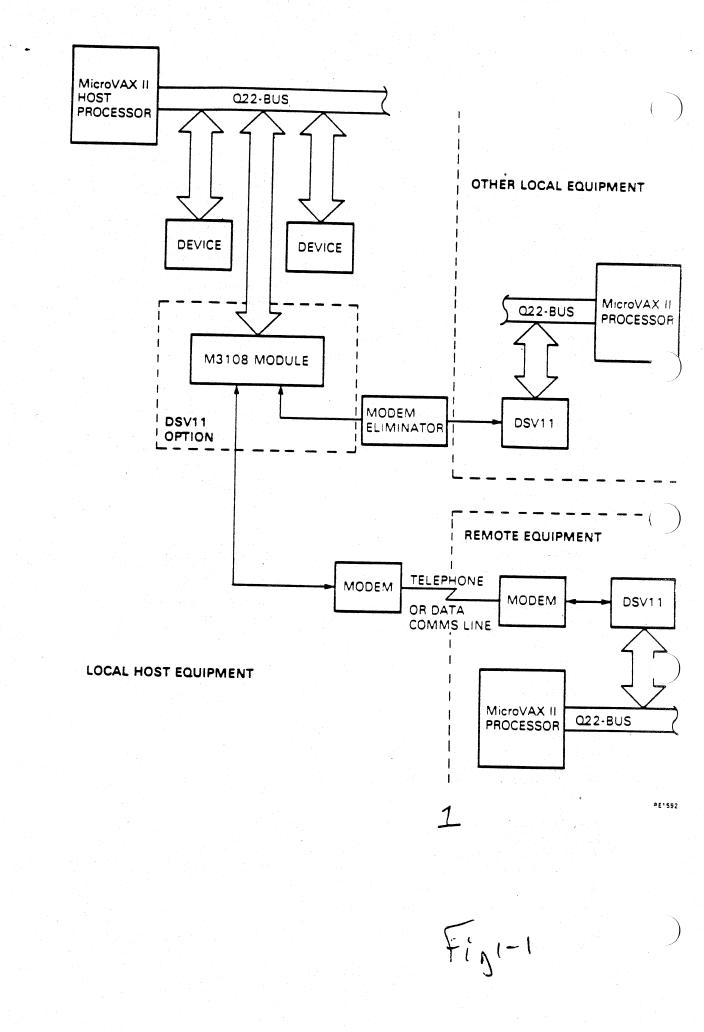

Figure 1-1 shows a possible DSV11 configuration.

Figure 1–1: Example of DSV11 Configuration -

RE159x?

OVERVIEW OF THE DSV11 1-3

# Chapter 2 REGISTERS AND COMMANDS

# 2.1 PROGRAMMING OVERVIEW

The next two chapters describe the control and status registers, and the command structures used to control and monitor the DSV11, and self-test diagnostic. Examples are also given. The following lists the broad functions performed by various parts of the logic and can be used to guide the reader in finding the information needed.

- Device registers (Section 2.2) are used to reset the DSV11 and to control and monitor the command list mechanism.

- The command list structure (Section 2.4) is the mechanism by which the host controls and monitors the communications functions of the DSV11.

- A command list is formed of command list elements (Section 2.5) which are built in DSV11 memory via CSRs.

- Each command list element contains a command function (Section 2.6) which tells the DSV11 exactly what to do.

- Chapter 3—Programming Features—describes how the host can use the command list mechanism to program the DSV11 to do useful work. Some programming examples are also included in Section 3.4.

# 2.2 DEVICE REGISTERS

The host controls and monitors the functions of the DSV11 module using command and response blocks that are built in command memory. Command and response blocks in DSV11 memory are accessed via CSRs.

Device registers on the DSV11 are used to initialize and control this process. These registers are all word length (16-bit) and cannot be accessed by byte-length transfers. Read-modify-write operations are not allowed on these registers.

### 2.2.1 Register Access

The DSV11 occupies four words (eight bytes) of Q-bus memory-mapped I/O space. The position of the four words within the I/O page is switch-selected on the DSV11. In order to access the module, bits <12:3> of an I/O address must match the address coded by the switch.

Table 2-1 lists the DSV11 registers and their addresses. The term base means the lowest I/O address on the module; that is, when the three low-order address bits are 0.

# Table 2-1: DSV11 Registers

| Register                        |           | Address<br>(Hexadecimal) | Туре       |

|---------------------------------|-----------|--------------------------|------------|

| Flag register                   | (FLAG)    | Base                     | Read/Write |

| Command Memory Address Register | (CMAR)    | Base + 2                 | Read/Write |

| Command Memory Data Register    | Low Word  | Base + 4                 | Read/Write |

| Command Memory Data Register    | High Word | Base + 6                 | Read/Write |

1

# 2.2.2 Register Bit Definitions

2.2.2.1 Flag Register (FLAG)

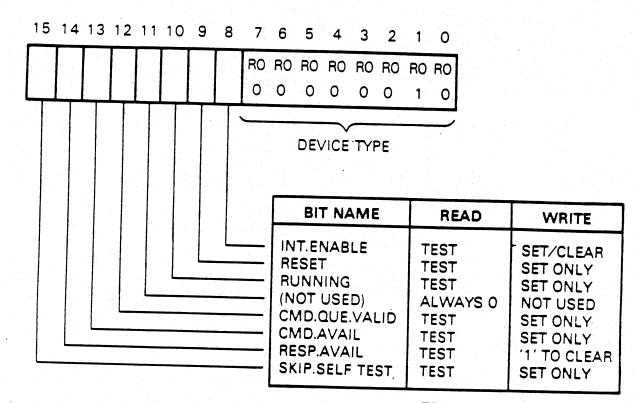

Figure 2-1: DSV11 Flag Register

**RE1600**

No bits in this register are valid until the DSV11 has cleared the RESET bit (FLAG<9>) after initialization.

| Bit        | Name                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <7:0>      | DEVTYPE<br>(Device Type)              | This byte contains a device type code. The DSV11 always returns 02 (hexadecimal).                                                                                                                                                                                                                                                                                                                              |

| 8          | INTENABLE                             | When this bit is set, the DSV11 will generate interrupts when it:                                                                                                                                                                                                                                                                                                                                              |

|            |                                       | • Sets the RESP.AVAIL bit (FLAG<14>)                                                                                                                                                                                                                                                                                                                                                                           |

|            |                                       | • Clears the RUNNING bit (FLAG<10>)                                                                                                                                                                                                                                                                                                                                                                            |

|            |                                       | If this bit is clear, interrupts will be disabled, but the DSV11 will continue to update the<br>response list if command blocks are available. It is possible for an interrupt to be generate<br>after this bit is cleared, because the effect of clearing the bit is not immediate. The host cannot<br>use the interrupt enable bit to synchronize access to the DSV11 or to DSV11 related day<br>structures. |

|            |                                       | This bit is cleared by reset.                                                                                                                                                                                                                                                                                                                                                                                  |

| 9          | RESET (Reset)                         | Setting this bit causes the DSV11 to begin its initialization procedure, including self-test. The host cannot clear this bit, and writing a 1 when it is already set has no effect. Writing a 0 to the bit has no effect at any time.                                                                                                                                                                          |

|            |                                       | This bit is also set by the DSV11 after bus initialization or power-up. It is cleared by the DSV11 after it has completed the self-test and initialization procedure.                                                                                                                                                                                                                                          |

|            |                                       | If SKIP.SELF.TEST (FLAG<15>) is set in the operation which sets this bit, the DSV11 wi<br>skip self-test during its initialization. Initialization will then complete in less than 1 ms. an<br>all the bits in the flag register are reset. (A self-test takes about 8 seconds to complete.)                                                                                                                   |

| To prevent | unexpected Q-bus operations,          | set the reset bit only when the host is certain that no DSV11 Q-bus transfers are in operation                                                                                                                                                                                                                                                                                                                 |

| 10         | RUNNING (Running)                     | This bit can be set by the host to start the DSV11 running and processing the command lis<br>Writing a 0 to the bit has no effect. The host cannot clear this bit.                                                                                                                                                                                                                                             |

|            |                                       | This bit is cleared by the DSV11 if it cannot continue to process the list. If the INT.ENABL bit is also set, this will generate an interrupt.                                                                                                                                                                                                                                                                 |

|            |                                       | Once this bit has been cleared, the DSV11 is restarted by setting up the initialization bloc<br>and then setting the bit again. Any command list elements that are outstanding when this b<br>is cleared are discarded, and not returned as response elements.                                                                                                                                                 |

| 11         | (Not Used)                            |                                                                                                                                                                                                                                                                                                                                                                                                                |

| 12         | CMDLIST.VALID<br>(Command List Valid) | The host must set this bit when it has put one or more command blocks onto the comman<br>list after the initialization block. Writing a 0 to the bit has no effect. The host cannot clea<br>this bit.                                                                                                                                                                                                          |

|            |                                       | The bit is cleared by the DSV11 when it responds to the last block on the command list. Whe this bit is clear, the CMD.AVAIL bit is ignored.                                                                                                                                                                                                                                                                   |

|            |                                       | Once the host receives a response which indicates that the DSV11 has detected the end of the list, it must remake the command list with any commands that have not been completed, an set this bit again. See Section 3.2 for further explanation.                                                                                                                                                             |

| 13         | CMD.AVAIL (Commands<br>Available)     | The host sets this bit each time it adds a new block to the command list. Provided that th CMD.LIST.VALID bit (FLAG<12>) is set, this tells the DSV11 that it needs to access th command list to fetch the next command.                                                                                                                                                                                       |

|            |                                       | The host cannot clear this bit.                                                                                                                                                                                                                                                                                                                                                                                |

| Bit | Name                               | Description                                                                                                                                                                                                                        |

|-----|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14  | RESPAVAIL<br>(Responses Available) | The DSV11 sets this bit each time it adds another response block to the response list. The host should clear this bit, and then process the complete response list. This bit is cleared by writing a 1; writing a 0 has no effect. |

|     |                                    | If the INT.ENABLE bit (FLAG<8>) is set when the DSV11 sets this bit, an interrupt is generated.                                                                                                                                    |

| 15  | SKIP'SELF.TEST                     | If this bit is set in the operation which sets the RESET bit (FLAG<9>), the DSV11 will skip self-test during its initialization.                                                                                                   |

|     |                                    | The host cannot clear this bit.                                                                                                                                                                                                    |

## 2.2.2.2 Command Memory Address Register (CMAR)

| Bit     | Name       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <15:11> | (Not used) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| <10:2>  | Offset     | Read/Write by the host. Specifies the longword base that the Command Memory Data Registers<br>will point to in the command memory. The register can be read from, but the data does not<br>come from the same hardware which controls the offset. The value will normally be that last<br>written by the host as the DSV11 does not intentionally modify it. At the completion of self-<br>test, the DSV11 writes a pattern to the location in Command Memory at offset zero and clears<br>the CMAR, but the value read in this case is the firmware version. |

| <1:0>   | (Not Used) | 에 가장 중요즘 가장 동안에 가장                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

# 2.2.2.3 Command Memory Data Register Low (CMDRL)

| Bit    | Name  | Description                                                                                                                                                                                                            |

|--------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <15:0> | CMDRL | After completion of the self-test (indicated by the clearing of the RESET bit, FLAG<9>), the host can read from this register to determine whether the self-test has passed. The following hexadecimal codes are used: |

|        |       | AAAA Completed successfully                                                                                                                                                                                            |

|        |       | 5555 Completed unsuccessfully                                                                                                                                                                                          |

|        |       | 55AA Self-test skipped                                                                                                                                                                                                 |

|        |       | Any other pattern indicates that either the register could not be written to, or that the fault was<br>so severe that the self-test failed to complete.                                                                |

|        |       | In normal operation, the host uses this register to read from, or to write to, Command Memory.<br>The word accessed will be that as indicated by the CMAR.                                                             |

### 2.2.2.4 Command Memory Data Register High (CMDRH)

| Bit Name     | Description                                                                                                                                                                                                                                                                                    |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <15:0> CMDRH | After the completion of the self-test (indicated by the clearing of the RESET bit FLAG<9>), the host uses this word to read from or to write to Command Memory. The word accessed is the word following that pointed to by the CMAR. This allows CMDRL and CMDRH to be accessed as a longword. |

|              | If the self-test completed unsuccessfully, the host can read a pattern from this register which indicates the test that failed and the reason. These codes and their meanings are described in Section 3.3, MAINTENANCE PROGRAMMING.                                                           |

## 2.3 COMMAND MEMORY

Command memory is the 2048 bytes of DSV11 memory that the host can access via the command memory data register and address register. Command memory is divided into 64 equal units, each 32 bytes long. The first unit is reserved for use as the initialization block, and the remainder are used as the command list elements. To access a particular word in command memory, the host must write the offset required into the command memory address register. The value written is the longword boundary at or before the word required. For example, the value for word 37 (bytes 74 and 75) is 72. The data can then be read from or written to the appropriate command memory data register word. Longword accesses are converted into two word accesses across the Q-bus. The order of word operations in this case is undefined, and you should take care if it is important. In the example case of word 37, the upper command memory data register should be accessed.

# 2.4 COMMAND LIST STRUCTURE

### 2.4.1 Overview

The four Q-bus registers described in Section 2.2 are used to control and monitor the processing of command lists. All control and monitoring of the DSV11 itself (for example, transferring data, and controlling device and channel parameters) is done through the command list mechanism. This section describes the structures used in this mechanism.

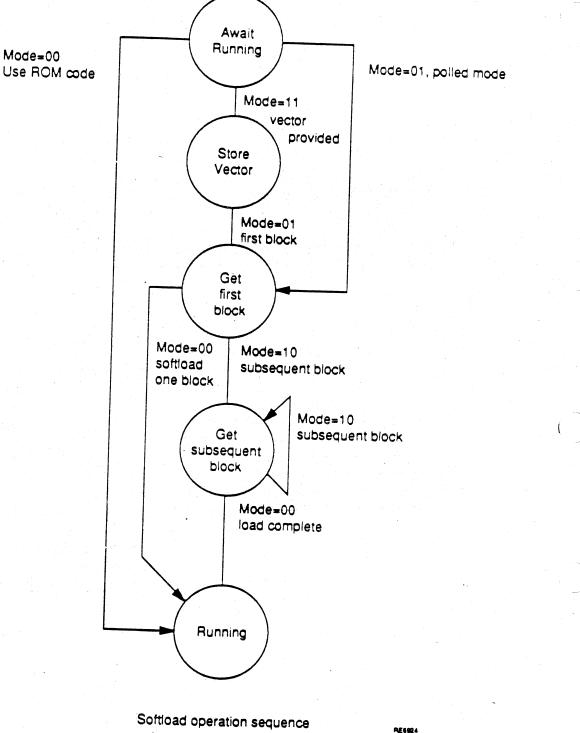

The command list consists of a linked list of elements each made up of 32 bytes (8 longwords). The command list elements are linked by a single pointer which gives the command memory address of the next element in the list. On the response list, a further pointer is used to link the elements together. The next few sections refer to the softload operation; Figure 2-2 shows the softload operation sequence.

### Figure 2-2: DSV11 Softload Operation Sequence

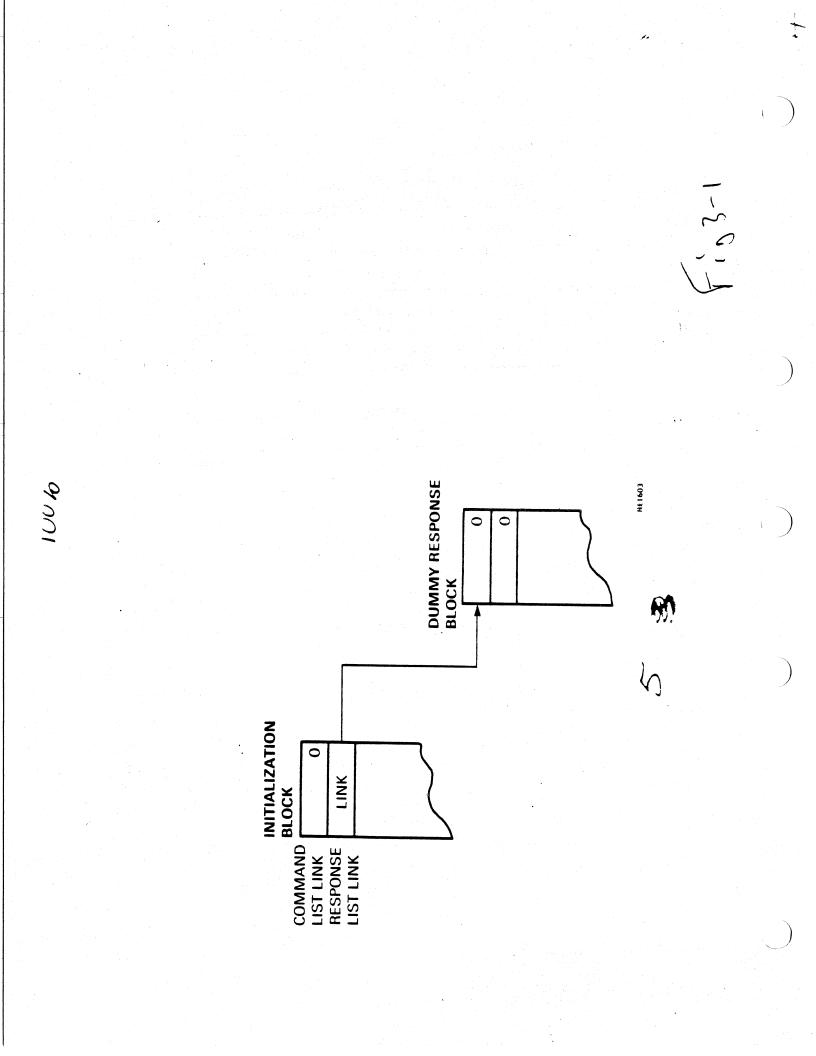

# 2.4.2 The Initialization Block

The first block in the command memory is the initialization block. The host sets up the initialization block by writing zero to the CMAR and then the command and response list pointers to the CMDRs, then 4 to the CMAR and the vector to the CMDRs. The RUNNING (FLAG<10>) bit is then set and the DSV11 will initialize the vector and its command and response lists.

The initialization block contains pointers to the start of both the command list and the response list. It also contains initialization information for the DSV11. The initialization block is eight longwords in length.

The format of the initialization block changes if a softload operation is required. If a softload is required, then only one longword is defined. The two most significant bits of the second longword are used to indicate which stage of the softload operation is to be performed. If both bits are set, then the least significant word contains the vector to be used for interrupt during the softload operation.

The vector is used when the interrupt is generated after each stage of the softload operation.

If only the least significant of the two bits is set (bit  $\langle 30 \rangle$ ), this indicates that the address in the least significant 22 bits is the start of the first block of down load data. The rest of the field is used to indicate the size in pages (512 bytes) of the data block. The value in this field is one less than the number of pages required. A value of zero thus indicates that 1 page is to be transferred.

If only the most significant of the two bits is set (bit  $\langle 31 \rangle$ ) this indicates that the address in the least significant 22 bits is the start of the next block of down load data. The rest of the field is used to indicate the size in pages (512 bytes) of the data block. The value in this field is one less than the number of pages required. A value of zero thus indicates that 1 page is to be transferred.

If neither of the two bits is set then this is an initialize operation.

The first word in the first long word contains the command memory address of the command list start (or zero if the list is empty). This location is used every time as the pointer to the start of the command list when command list valid is set. If the first word value is non-zero and the Running, Command available and Command list valid bits are all set in the initialize operation, the Command list will be processed immediately after the initialization is complete.

If interrupt enable is set, and the commands used generate an immediate response (for example, report board parameters), the host can determine when the initialize operation is complete, as an interrupt will be generated.

The second word contains the command memory address of the response list start. The response list start may contain the address of a response block when the initialization is performed, or zero to indicate the end of the response list. These contents let the host software perform the same tasks when a response is removed from the list. You must always leave the last response on the list, as the response list link field in it is used to add the next response.

If a dummy response is not present at initialization time, then the host does not have a response it can discard when the first real response is added to the list. This means that you must check the list each time a response is removed to ensure that a response still remains. The third and fourth words contain the vector which the device uses on interrupt. The vector longword must contain a valid vector with the most significant bits all zero.

The fifth to eighth words contain the DSV11 wide area network identification when the self-test has finished. This ID can also be determined using the Return Device Parameters described in Section 2.6.1.

#### 2.4.3 The Command List

To give commands to the DSV11, command blocks, each 32 bytes (8 longwords) in length, are set up in command memory. Each block gives the DSV11 an instruction; for example, to transmit a data buffer. or to alter some channel parameters.

The command list is a linked list of such blocks. A single forward pointer in each block is used to link the blocks in a list together. A separate pointer is maintained for commands to the DSV11, and for responses from it.

The host signals the presence of new commands to the DSV11 by setting the CMD.LIST.VALID (FLAG<12>) and the CMD.AVAIL (FLAG<13>) bits in the FLAG register. The DSV11 processes as many commands as it can at the same time. Commands that cannot be processed at the same time are queued by the DSV11.

#### 2.4.4 The Response List

When a command has been processed and completed, or aborted, the DSV11 converts the command block into a response block. To do this it updates some fields in the original command block, and places the block on the response list by adjusting the response list link pointer(s).

The response block includes a status field from which the host can determine whether the command completed successfully or not.

The DSV11 continues to process commands and generate response blocks until it has responded to the last block in the list. It sets a bit in the last command block that indicates *End of command list detected*. The host must then make a new command list and set the CMD.LIST.VALID bit.

### 2.5 COMMAND LIST ELEMENTS

### 2.5.1 Command List Element Structure

Each command list element consists of 8 longwords (32 bytes), and must be aligned on a 16-byte boundary. The structure of a command list element is shown in Figure 2-3.

## Figure 2–3: DSV11 Command List Element Structure

RE1602

The following sections describe each field in this structure.

### 2.5.1.1 Command List Link Address

| Bit    | Name                           | Description                                                                                                                                                                                                                                                       |

|--------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <15:0> | Command List Link Ad-<br>dress | This word contains a reference to the next item in the list. Only bits <11:2> are used: all others must be zero. Because the command list elements are on 32 byte boundaries, bits <4:2> are also normally zero, but the DSV11 does not enforce this restriction. |

|        |                                | This field is zero in the last entry in the list. It must be updated after the next command list element has been filled in, but before the commands available bit is set in the flag register.                                                                   |

### 2.5.1.2 Response List Link Address

| Bit    | Name                   | Description                                                                                                                                                |

|--------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <15:0> | Response List Link Ad- | The DSV11 sets this field to the address of the start of the next element in the response list.                                                            |

|        | dress                  | The DSV11 updates this field before setting the RESPAVAIL bit (FLAG<14>). If the element is the last in the response list, this field is set to all zeros. |

### 2.5.1.3 Function Longword

The bits in this longword can be grouped into four byte-length fields:

| <7:0>   | Command Code      |

|---------|-------------------|

| <15:8>  | Channel Number    |

| <23:16> | Command Status    |

| <31:24> | Completion Status |

|         |                   |

Each field is described in this section.

| Bit                    | Name                            | Description                                                                                                                                                                                                                                                    |  |

|------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| COMMAN                 | ND CODE <7:0>                   |                                                                                                                                                                                                                                                                |  |

| <6:0> Command Function |                                 | The host sets these bits to determine the function of the command element. The codes used are (in hexadecimal):                                                                                                                                                |  |

|                        |                                 | 00 Report device type and parameters                                                                                                                                                                                                                           |  |

|                        |                                 | 01 Return channel parameters                                                                                                                                                                                                                                   |  |

|                        |                                 | 10 Initialize specified channel                                                                                                                                                                                                                                |  |

|                        |                                 | 11 Update channel parameters                                                                                                                                                                                                                                   |  |

|                        |                                 | 13 Reset channel                                                                                                                                                                                                                                               |  |

|                        |                                 | 20 Transmit data from host buffer                                                                                                                                                                                                                              |  |

|                        |                                 | 30 Receive data into host buffer                                                                                                                                                                                                                               |  |

|                        |                                 | 40 Update and report modern status                                                                                                                                                                                                                             |  |

|                        |                                 | 50 Report status change                                                                                                                                                                                                                                        |  |

|                        |                                 | 7F Switch to maintenance mode                                                                                                                                                                                                                                  |  |

|                        |                                 | These command functions are fully described in Section 2.6.                                                                                                                                                                                                    |  |

| 7                      | Not used                        | Must be zero                                                                                                                                                                                                                                                   |  |

|                        |                                 |                                                                                                                                                                                                                                                                |  |

| CHANNE                 | L NUMBER<15:8>                  |                                                                                                                                                                                                                                                                |  |

| <15:8>                 | Channel Number                  | The host sets this byte to specify the channel number to which the command applies. Th DSV11 supports only two channels, 0 and 1; therefore this byte can only contain the value 0 or 01.                                                                      |  |

| COMMA                  | ND STATUS<23:16>                |                                                                                                                                                                                                                                                                |  |

| <19:16>                | (Not used)                      |                                                                                                                                                                                                                                                                |  |

| 20                     | Command Being Pro-<br>cessed    | The DSV11 sets this bit when it starts to process the command. If any fields in the comman block are updated by the DSV11 while it is processing the command, this bit tells the host that those fields are valid.                                             |  |

| 21                     | End of Command List<br>Detected | This bit is set by the DSV11 as part of the response block. It indicates that the DSV1 considers this block to be the last in the current list.                                                                                                                |  |