parallel line interface

DRV11-J parallel line interface user's guide

EK-DRV1J-UG-002

digital equipment corporation • marlboro, massachusetts

11/80-15

Copyright <sup>©</sup> 1979, 1980 by Digital Equipment Corporation

#### All Rights Reserved

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

# This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DIGITAL | DECsystem-10 | MASSBUS      |

|---------|--------------|--------------|

| DEC     | DECSYSTEM-20 | OMNIBUS      |

| PDP     | DIBOL        | <b>OS</b> /8 |

| DECUS   | EduSystem    | RSTS         |

| UNIBUS  | VAX          | RSX          |

| DECLAB  | VMS          | IAS          |

|         |              | MINC-11      |

# CONTENTS

# CHAPTER 1 INTRODUCTION

| GENERAL DESCRIPTION     | 1-1                                                                                                                                                                                                                                                                       |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FEATURES                | 1-1                                                                                                                                                                                                                                                                       |

| DOCUMENTATION           | 1-2                                                                                                                                                                                                                                                                       |

| DIAGNOSTIC SOFTWARE     | 1-2                                                                                                                                                                                                                                                                       |

| SPECIFICATIONS          | 1-2                                                                                                                                                                                                                                                                       |

| Physical Specifications | 1-2                                                                                                                                                                                                                                                                       |

|                         |                                                                                                                                                                                                                                                                           |

|                         |                                                                                                                                                                                                                                                                           |

|                         |                                                                                                                                                                                                                                                                           |

|                         |                                                                                                                                                                                                                                                                           |

|                         |                                                                                                                                                                                                                                                                           |

| Altitude                | 1-3                                                                                                                                                                                                                                                                       |

| INSTALLATION            | 1-3                                                                                                                                                                                                                                                                       |

|                         | FEATURES<br>DOCUMENTATION.<br>DIAGNOSTIC SOFTWARE<br>SPECIFICATIONS.<br>Physical Specifications.<br>Electrical Specifications.<br>Environmental Specifications<br>Operating and Storage Temperature Ranges<br>Relative Humidity.<br>Airflow during Operation.<br>Altitude |

# CHAPTER 2 FUNCTIONAL DESCRIPTION

| 2.1     | GENERAL DESCRIPTION                        | 2-1  |

|---------|--------------------------------------------|------|

| 2.2     | CONTROL/STATUS REGISTERS                   | 2-1  |

| 2.3     | DATA BUFFER REGISTERS                      | 2-1  |

| 2.4     | INTERRUPT CONTROL                          | 2-1  |

| 2.4.1   | Functional Description                     | 2-7  |

| 2.4.2   | Interrupt Controller Interface             |      |

| 2.4.3   | Interrupt Controller Operating Description |      |

| 2.4.4   | Interrupt Control Reset                    |      |

| 2.4.5   | Interrupt Control Register Description     | 2-13 |

| 2.4.5.1 | Status Register                            |      |

| 2.4.5.2 | Command Register                           |      |

| 2.4.5.3 | Mode Register                              |      |

| 2.4.5.4 | Interrupt Request Register (IRR)           |      |

| 2.4.5.5 | Interrupt Service Register (ISR)           |      |

| 2.4.5.6 | Interrupt Mask Register (IMR)              |      |

| 2.4.5.7 | Auto-Clear Register (ACR)                  |      |

| 2.4.5.8 | Vector Address Memory                      |      |

| 2.5     | OPERATING OPTIONS                          |      |

| 2.5.1   | Interrupt Priority Mode Selection          |      |

| 2.5.2   | Individual Vector or Common Vector Mode    | 2-19 |

| 2.5.3   | Interrupt or Polled (Flag) Mode            |      |

| 2.5.4   | Mode Register Bit 3                        |      |

| 2.5.5   | IRQ Polarity Option                        |      |

| 2.5.6   | Register Preselection Option               |      |

| 2.5.7   | Master Mask Option                         |      |

| 2.6     | SYSTEM OPERATING SEQUENCE                  | 2-20 |

| 2.7     | COMMAND DESCRIPTIONS                       | 2-21 |

| 2.7.1   | Reset                                      |      |

| 2.7.2   | Clear IRR and IMR                          |      |

| 2.7.3   | Clear Single IMR and IRR Bit               |      |

| 2.7.4   | Clear IMR                                  |      |

# CONTENTS (Cont)

# Page

| 2.7.5     | Clear Single IMR Bit                         | 2-22 |

|-----------|----------------------------------------------|------|

| 2.7.6     | Set IMR                                      | 2-22 |

| 2.7.7     | Set Single IMR Bit                           | 2-22 |

| 2.7.8     | Clear IRR                                    | 2-22 |

| 2.7.9     | Clear Single IRR Bit                         | 2-22 |

| 2.7.10    | Set IRR                                      | 2-22 |

| 2.7.11    | Set Single IRR Bit                           | 2-23 |

| 2.7.12    | Clear Highest Priority ISR Bit               | 2-23 |

| 2.7.13    | Clear ISR                                    | 2-23 |

| 2.7.14    | Clear Single ISR Bit                         | 2-23 |

| 2.7.15    | Load Mode Bits M0 through M4                 | 2-23 |

| 2.7.16    | Control Mode Bits M5, M6 and M7              | 2-23 |

| 2.7.17    | Preselect IMR for Writing                    | 2-24 |

| 2.7.18    | Preselect ACR for Writing                    | 2-24 |

| 2.7.19    | Preselect Vector Address Memory for Writing  | 2-24 |

| 2.7.20    | Coding B2, B1, B0 Field Commands             | 2-25 |

| CHAPTER 3 | CONFIGURATION                                |      |

| 3.1       | GENERAL DESCRIPTION                          | 3-1  |

| 3.2       | FACTORY CONFIGURATION                        | 3-1  |

| 3.3       | DEVICE ADDRESSES                             | 3-1  |

| 3.4       | DEVICE ADDRESS JUMPERS                       | 3-5  |

| 3.5       | INTERRUPT VECTOR ADDRESSES                   | 3-5  |

| CHAPTER 4 | INTERFACING                                  |      |

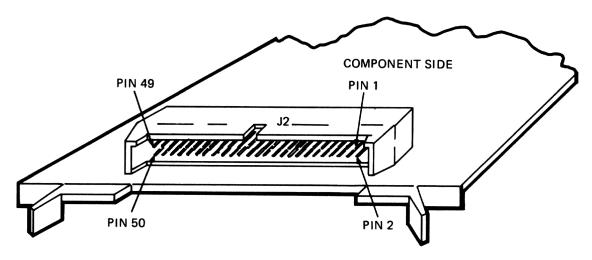

| 4.1       | INTERFACE CONNECTORS                         | 4-1  |

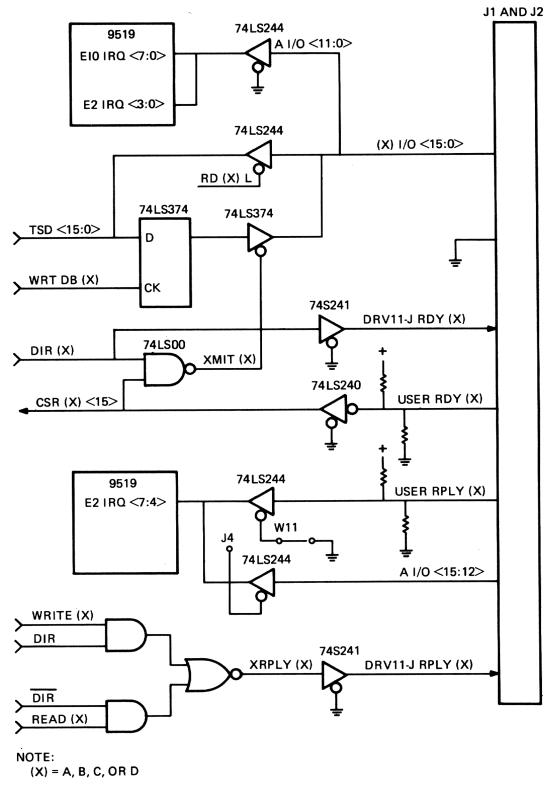

| 4.2       | INPUT/OUTPUT SIGNAL FUNCTIONS                | 4-1  |

| 4.3       | INPUT/OUTPUT SIGNAL ASSERTION LEVELS         | 4-1  |

| 4.4       | INPUT/OUTPUT SIGNAL LOOPBACK CONNECTIONS     | 4-5  |

| 4.5       | INTERFACE CABLE                              | 4-5  |

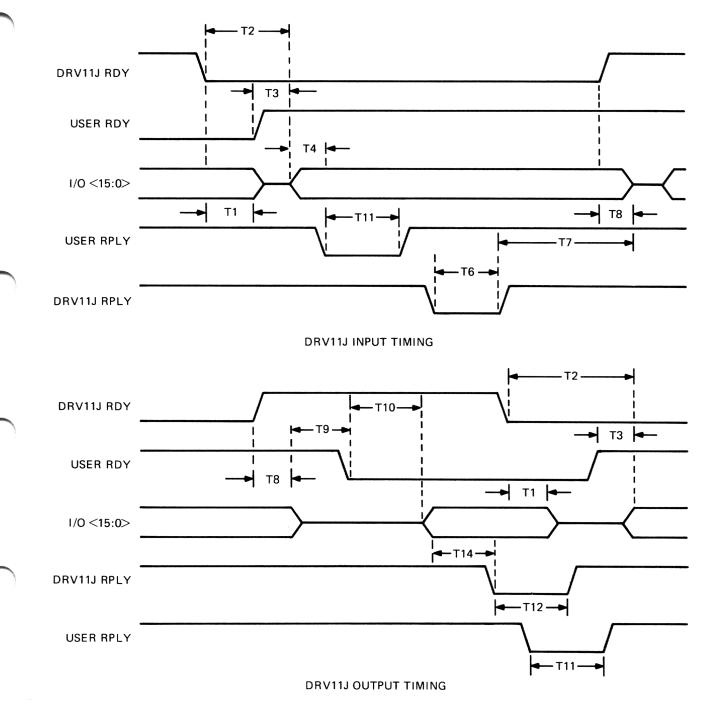

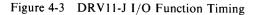

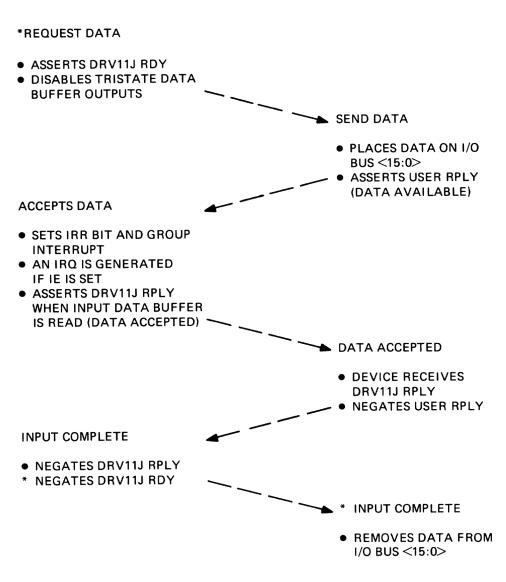

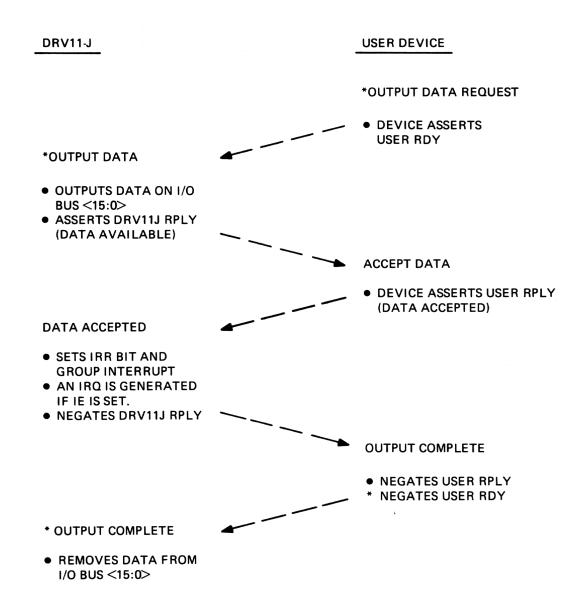

| 4.6       | INPUT/OUTPUT FUNCTION TIMING                 | 4-5  |

| 4.7       | INPUT DATA OPERATION                         | 4-9  |

| 4.8       | OUTPUT DATA OPERATION                        | 4-9  |

| 4.9       | INTERRUPT OPERATION                          | 4-9  |

| CHAPTER 5 | PROGRAMMING EXAMPLES                         |      |

| 5.1       | GENERAL DESCRIPTION                          | 5-1  |

| 5.2       | PROGRAMMED DATA TRANSFER WITHOUT HANDSHAKING | 5-1  |

| 5.3       | PROGRAMMED DATA TRANSFER WITH HANDSHAKING    |      |

| 5.4       | INTERRUPT-DRIVEN TRANSFER                    |      |

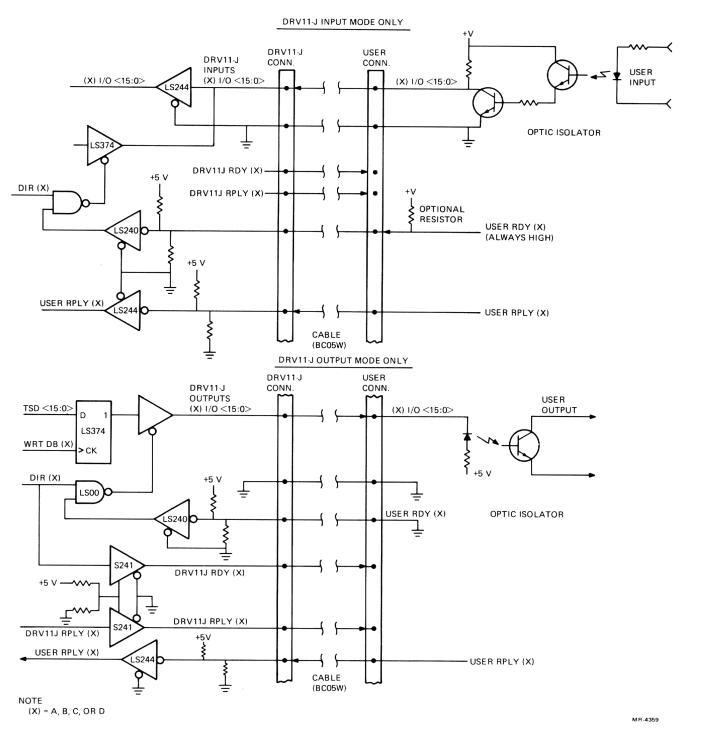

| CHAPTER 6 | OPTIC ISOLATOR INTERFACE EXAMPLE             |      |

|           |                                              |      |

# **FIGURES**

#### Title

#### Page

Page

1-4

2-3

|   | 2-1  | DRV11-J Block Diagram                           | 2-2  |

|---|------|-------------------------------------------------|------|

|   | 2-2  | CSRA Bit Assignments                            | 2-3  |

|   | 2-3  | CSRB Bit Assignments                            | 2-4  |

|   | 2-4  | CSRC Bit Assignments                            | 2-5  |

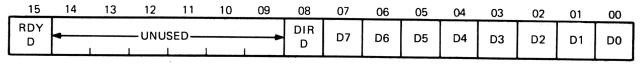

|   | 2-5  | CSRD Bit Assignments                            | 2-6  |

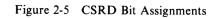

|   | 2-6  | Data Buffer Register Bit Assignments            | 2-7  |

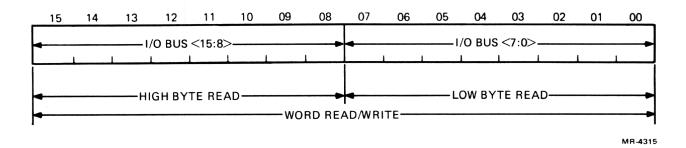

|   | 2-7  | Group 1 and Group 2 Interrupt Controller        |      |

|   |      | Interconnections                                | 2-8  |

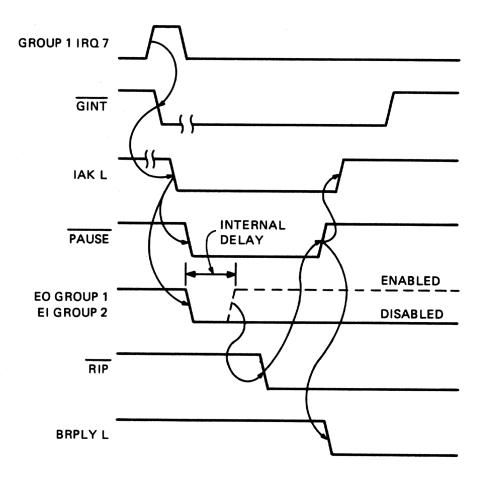

|   | 2-8  | Intergroup Priority Resolution Timing           | 2-10 |

|   | 2-9  | Interrupt Controller Block Diagram.             | 2-11 |

|   | 2-10 | CSRA and CSRC Status Registers' Bit Assignments | 2-14 |

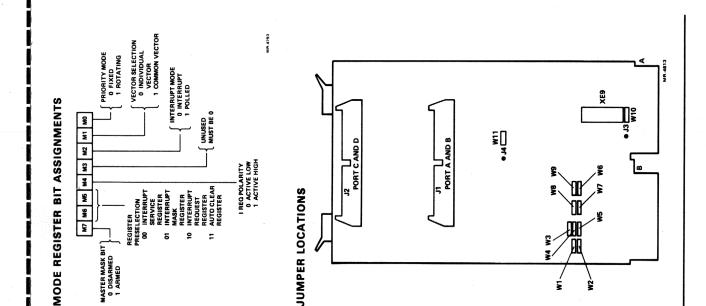

|   | 2-11 | Mode Register Bit Assignments                   | 2-15 |

|   | 2-12 | DRV11-J Vector Address Format                   | 2-17 |

|   | 2-13 | Rotating Priority Mode                          | 2-18 |

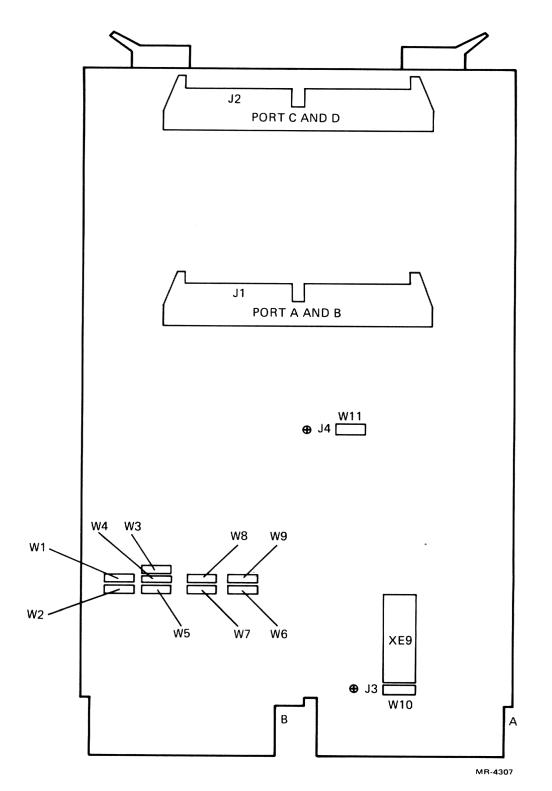

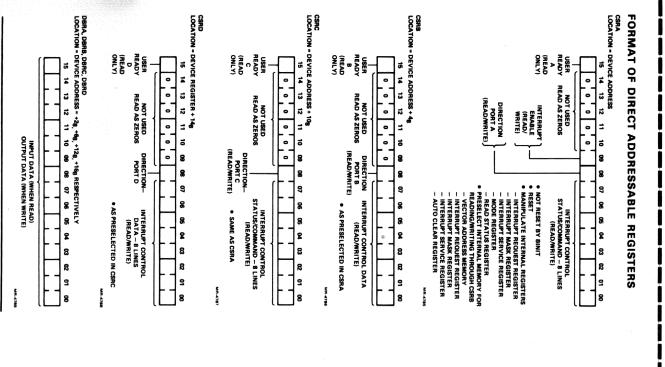

|   | 3-1  | DRV11-J Jumper Locations                        | 3-2  |

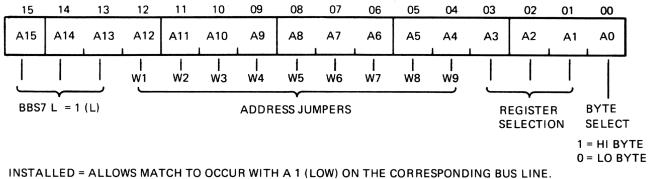

|   | 3-2  | DRV11-J Device Address Format                   | 3-5  |

|   | 4-1  | DRV11-J I/O Connector Pin Locations             | 4-2  |

|   | 4-2  | I/O Bus Interface, Simplified Schematic         | 4-4  |

|   | 4-3  | DRV11-J I/O Function Timing                     | 4-7  |

|   | 4-4  | Input Data Transfer Sequence                    | 4-10 |

|   | 4-5  | Output Data Transfer Sequence                   | 4-11 |

|   | 4-6  | Interrupt Sequence                              | 4-12 |

|   | 5-1  | Example of a Programmed Data Transfer           |      |

|   |      | without Handshaking                             | 5-2  |

|   | 5-2  | Example of a Programmed Data Transfer           |      |

|   |      | with Handshaking                                | 5-3  |

|   | 5-3  | Example of an Interrupt-Driven Output Program   | 5-4  |

|   | 5-4  | Example of an Interrupt-Driven Input Program    | 5-5  |

| ( | 5-1  | Example of an Optic Isolator Interface          | 6-2  |

|   |      |                                                 |      |

# **TABLES**

Title

#### Table No.

1-1

2-1

2-2

Figure No.

# DRV11-J Module Pin Assignment CSRA Bit Functions and Descriptions CSRB Bit Functions and Descriptions

| 2-2 | CSRB Bit Functions and Descriptions           | 2-4              |

|-----|-----------------------------------------------|------------------|

| 2-3 | CSRC Bit Functions and Descriptions           | 2-5              |

| 2-4 | CSRD Bit Functions and Descriptions           | 2-6              |

| 2-5 | Summary of Data Bus Transfers                 | 2-12             |

| 2-6 | Interrupt Control Register and Memory Summary | 2 - 12<br>2 - 13 |

| 2-7 | Fixed Priority Mode                           | 2 - 13<br>2.17   |

| 2-8 | Vector Address Memory Field Coding            | 2-17             |

| 2-9 | Command Register B2, B1, B0 Field Coding      | 2-25             |

|     | <b>U</b>                                      |                  |

#### v

# TABLES (Cont)

# Title

Table No.

# Page

| 2-10 | DRV11-J Command Code Summary         | 2-26 |

|------|--------------------------------------|------|

| 3-1  | DRV11-J Factory Jumper Configuration |      |

| 3-2  | DRV11-J Jumper Functions             | 3-4  |

| 3-3  | DRV11-J Registers                    | 3-4  |

| 4-1  | I/O Connector Pin Assignments        | 4-2  |

| 4-2  | I/O Signal Functions                 | 4-5  |

| 4-3  | DRV11-J Loopback Signal Connections  | 4-6  |

| 4-4  | I/O Function Timing Tolerance        |      |

# CHAPTER 1 INTRODUCTION

#### **1.1 GENERAL DESCRIPTION**

The DRV11-J is a double-height parallel line interface module designed for use in LSI-11 microcomputer systems. It contains four programmable ports designated A, B, C and D. Each port contains 16 I/O lines and is capable of transferring a 16-bit word between the LSI-11 bus and the user device(s). Data word transfers in or out of the DRV11-J are accomplished by the assertion of two control signals at each port of the DRV11-J and two control signals asserted by the user device to its respective port. These control signals must be asserted in a protocol sequence while observing timing constraints to ensure an orderly data transfer. The protocol sequence is described in Chapter 2.

The DRV11-J will also accept interrupt requests from up to 16 I/O lines to generate up to 16 individual vector addresses. This interrupt capability for real-time response makes it useful for sensor I/O applications. The DRV11-J may also be used as a general-purpose interface to custom devices, or two DRV11-Js may be connected together as a link between two LSI-11 buses.

The DRV11-J contains two programmable mode registers that provide a number of operating modes to customize the module configuration for different system applications. The module may be programmed for use in vectored-interrupt-driven systems or software-polled systems. When used in vectored interrupt systems, the module may be programmed to operate in either a fixed priority or a rotating priority resolution mode. In addition, the module may be programmed to generate either a common vector address or individual vector addresses in response to user device(s) interrupt requests. Additional operating options available under program control include the selection of an active high or active low interrupt request polarity, preselection of internal registers, and the selection of a master mask bit to arm or disarm the interrupt capability of the DRV11-J. All of the operating modes and options are described in detail in Chapter 2.

The DRV11-J also contains two RAMs that are used to store programmed interrupt vector addresses. One 8-bit RAM location is used to store each interrupt vector address. One vector address may be programmed for each of the 16 interrupt request inputs.

#### **1.2 FEATURES**

The DRV11-J contains the following features.

- Four 3-state 16-bit parallel I/O ports

- User-assigned device addresses

- Acceptance of up to 16 external interrupt requests

- Programmable interrupt vector addresses

- Program-controlled input/output operations

- Programmable operating modes:

Interrupt Controller Mode – Interrupt-driven Priority Modes – Fixed or Rotating Vector Address Selection – Individual or common vector

1-1

#### **1.3 DOCUMENTATION**

In addition to this user's guide, refer to the *Field Maintenance Print Set*, MP00866, for information on the DRV11-J module.

#### **1.4 DIAGNOSTIC SOFTWARE**

Diagnostic software is available for troubleshooting, fault isolation, and verification at both the module level and system level. Two diagnostics are required for testing at the module level and these must be run in sequence. A DECX11 module diagnostic is required to test the module at the system level. Turnaround cable BC05W-02 must be installed with a half twist to J1 and J2 when running the module- and system-level diagnostics. The diagnostic software is designated as follows.

- CVDRCAO Part 1

- CVDRDAO Part 2

- DECX11 Module CXDRJAO

#### **1.5 SPECIFICATIONS**

The following defines the physical, electrical and environmental specifications for the DRV11-J module.

#### 1.5.1 Physical Specifications

| Identification | M8049                                                                 |  |  |

|----------------|-----------------------------------------------------------------------|--|--|

| Size           | Double-height<br>22.8 cm $\times$ 13.2 cm<br>(8.9 in $\times$ 5.2 in) |  |  |

ac 2 dc 1

#### 1.5.2 Electrical Specifications

Power

+5 Vdc  $\pm$  5% @ 1.8 A (maximum), 1.6 A (typical)

Bus Loads

I/O Signal Electrical Parameters:

| Data Buffer 3-State Outputs                                                                         | Data Buffer Inputs                                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V(OL) = 0.5 V @ I(OL) = 8 mA<br>V(OL) = 0.4 V @ I(OL) = 4 mA<br>V(OH) = 2.4 V @ I(OH) = -2.6 mA     | I(IL) = -0.2  mA @ V(IL) = 0.4  V<br>V(IH) = 20 $\mu$ A @ V(IH) = 2.7 V                                                                                                     |

| Protocol Signal 3-State Outputs<br>V(OL) = 0.55 V @ I(OL) = 64 mA<br>V(OH) = 2.4 V @ I(OH) = -15 mA | Protocol Signal Inputs<br>Termination = $120 \Omega$<br>I(IL) = $-27 \text{ mA} @ \text{V(IL)} = 0.5 \text{ V}$<br>I(IH) = $80 \mu \text{A} @ \text{V(IH)} = 2.7 \text{ V}$ |

1

#### 1.5.3 Environmental Specifications

The DRV11-J module may be operated or stored in the following environmental conditions.

#### **1.5.3.1** Operating and Storage Temperature Ranges

Operating range: $5^{\circ}$  to  $60^{\circ}$  C ( $41^{\circ}$  to  $140^{\circ}$  F)Storage range: $-40^{\circ}$  to  $66^{\circ}$  C ( $-40^{\circ}$  to  $150^{\circ}$  F)

If the module is not within its operating temperature range, move it to an area within the range and allow it to stabilize for a minimum of five minutes before operating. Also, derate the maximum operating temperature by 1° C ( $1.8 \circ F$ ) for each 305 m (1000 ft) of altitude above 2440 m (8000 ft).

#### 1.5.3.2 Relative Humidity

Storage: 10% to 90%, noncondensing

Operating: 10% to 90%, noncondensing

**1.5.3.3** Airflow during Operation – Provide adequate airflow to limit the inlet-to-outlet temperature rise across the module to 5° C (9° F) when the inlet temperature is 60° C (140° F). For operation below 55° C (131° F), limit that rise to 10° C (18° F) maximum.

#### 1.5.3.4 Altitude

Storage: The module will not be mechanically or electrically damaged at altitudes up to 15,240 m (50,000 ft), 90 mm mercury.

Operating: Up to 15,240 m (50,000 ft), 90 mm mercury. Note: Derate the maximum operating temperature by 1° C (1.8° F) for each 305 m (1000 ft) of altitude above 2440 m (8000 ft).

#### **1.6 INSTALLATION**

The DRV11-J is a bus request level 4 module and must be installed in an LSI-11 backplane dual-option slot following the rules for position-dependent interrupt priority configurations. In position-dependent configurations, peripheral devices with the highest priority must be installed closest to the processor and the remaining devices placed in the backplane in decreasing order of priority, with the lowest priority module farthest from the processor.

Before installing the module(s) in the backplane, check that the proper device address jumpers are installed. Three standard LSI-11 bus addresses are reserved for the DRV11-Js. If the application requires more than three DRV11-Js, the additional modules must be assigned addresses located in the user-reserved address space. Chapter 3 describes the address configuration procedure. The standard factory jumper configuration is described in Table 3-1, and Figure 3-2 shows the device address format.

#### CAUTION DC power must not be applied to the backplane when installing or removing modules.

The DRV11-J's functionality must be proved after installation by performing an acceptance test. The acceptance test consists first of running the basic system diagnostics and then running the DRV11-J module-level diagnostics listed in Paragraph 1.4.

# **Module Pin Assignments**

The DRV11-J module pin assignments are described in Table 1-1.

| Connector A      |     |                  | C                | onnector <b>B</b> |                  |

|------------------|-----|------------------|------------------|-------------------|------------------|

| Side 1<br>Signal | Pin | Side 2<br>Signal | Side 1<br>Signal | Pin               | Side 2<br>Signal |

| BIRQ 5 L         | А   | +5 V             | NC               | А                 | +5 V             |

| BIRQ 6 L         | В   | NC               | NC               | В                 | NC               |

| NC               | C   | GND              | NC               | C                 | GND              |

| NC               | D   | NC               | NC               | - D               | NC               |

| NC               | E   | BDOUT L          | NC               | E                 | BDAL 2 L         |

| NC               | F   | BRPLY L          | NC               | F                 | BDAL 3 L         |

| NC               | н   | BDIN L           | NC               | н                 | BDAL4L           |

| NC               | J   | BSYNC L          | NC               | J                 | BDAL5L           |

| NC               | K   | BWTBT L          | NC               | к                 | BDAL6L           |

| NC               | L   | BIRQ 4           | NC               | L                 | BDAL7L           |

| NC               | M   | BIAKIL           | NC               | М                 | BDAL 8 L         |

| NC               | N   | BIAKO L          | NC               | N                 | BDAL9L           |

| NC               | Р   | BBS 7 L          | BIRQ 7 L         | Р                 | BDAL 10 L        |

| NC               | R   | BDMGI L          | NC               | R                 | BDAL 11 L        |

| NC               | S   | BDMGO L          | NC               | S                 | BDAL 12 L        |

| GND              | Т   | BINIT L          | GND              | Т                 | BDAL 13 L        |

| NC               | U   | BDALO L          | NC               | U                 | BDAL 14 L        |

| NC               | v   | BDALI L          | NC               | v                 | BDAL 15 L        |

Table 1-1 DRV11-J Module Pin Assignment

NOTE:

1. Connector A, pin A, side 1 corresponds to bus pin AA1.

2. NC = no connection.

# CHAPTER 2 FUNCTIONAL DESCRIPTION

#### 2.1 GENERAL DESCRIPTION

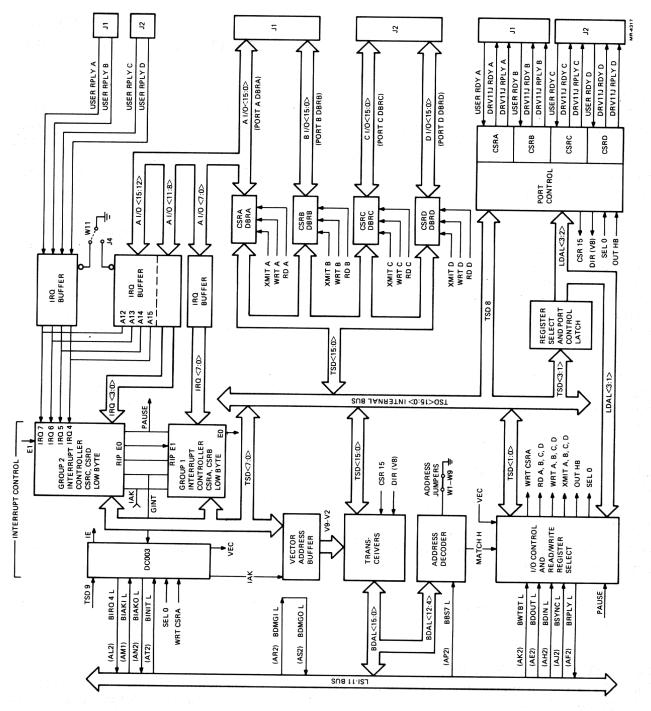

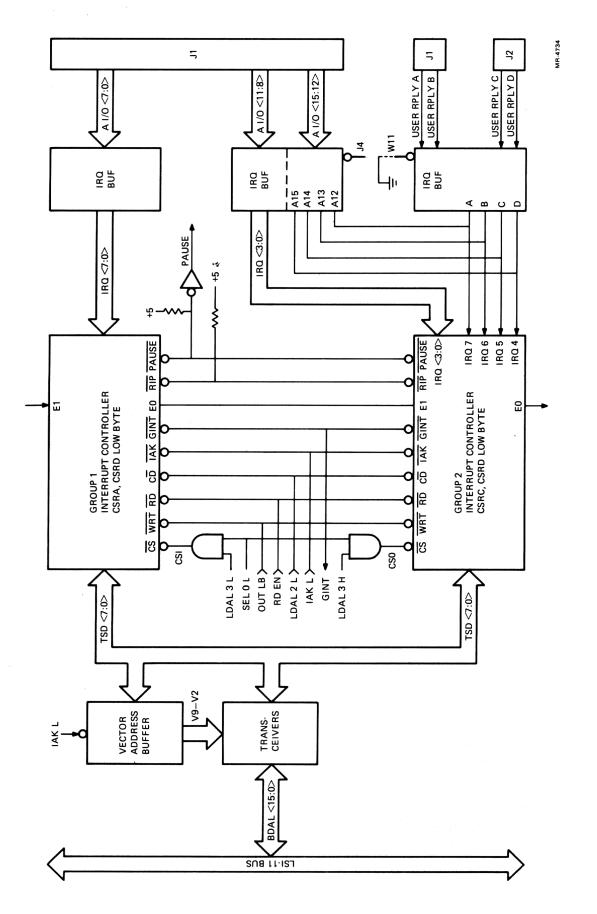

The DRV11-J contains the logic necessary to provide communication between the LSI-11 bus and up to four user devices in 16-bit word lengths via four I/O ports. Four control lines associated with each of the four ports ensure orderly information transfers. Word transfers are executed by programmed I/O operations or interrupt-driven routines. Write data is output by the DRV11-J to the I/O bus through 3-state data latches, and read data is input through unlatched bus buffers. Figure 2-1 shows the main logic functions performed by the DRV11-J module.

All control/status and I/O data transfers take place over a bidirectional internal bus (TSD <15:00>) on the DRV11-J. The module contains four I/O buses, one for each port (A, B, C and D). Each port has an associated control/status register (CSRA, CSRB, CSRC or CSRD) that contains status information when read and command words when written. All ports have 16 bidirectional 3-state lines and perform controlled input/output operations. Note that port A is the only port that will perform bit interrupt functions in addition to input/output data transfers. The 16 external interrupt requests are functionally divided into two groups of eight lines, referred to as group 1 and group 2.

#### 2.2 CONTROL/STATUS REGISTERS

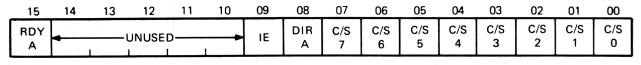

The control/status registers (CSRA, CSRB, CSRC and CSRD) are read/write byte-addressable registers with bit assignments as shown in Figures 2-2, 2-3, 2-4 and 2-5. The function and description of the control/status register bits are described in Tables 2-1, 2-2, 2-3 and 2-4.

#### 2.3 DATA BUFFER REGISTERS

The four data buffer registers (DBRA, DBRB, DBRC and DBRD) are 16-bit word-addressable registers. They are used as latched output data buffers when the DRV11-J is in output mode (write) and as unlatched bus buffers in input mode (read). The contents of the output data buffers may be examined while the DRV11-J is in an output mode by performing a read operation of the input data buffers. This ability to examine the output data buffers in the output mode provides software access to the internal conditions of the DRV11-J.

The latched output data buffer registers DRBA through DBRD are not cleared by BINIT. The bit assignment is the same for all registers and is shown in Figure 2-6.

#### 2.4 INTERRUPT CONTROL

The DRV11-J is capable of monitoring 16 lines to generate 16 vectored interrupts. The interrupt control is performed by a DC003 interrupt logic chip and interrupt controller chips. A functional description of the signals required to initiate interrupts and the DRV11-J registers used for programming, reading and writing the internal registers of the interrupt controllers is given in Paragraph 2.4.1. An operating description of the interrupt controllers is given in Paragraph 2.4.2, and the internal registers of the interrupt controllers are described in Paragraph 2.5

Figure 2-1 DRV11-J Block Diagram

2-2

MR-4310

### Figure 2-2 CSRA Bit Assignments

| Bit   | Name      | Function   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|-----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 07:00 | C/S7–C/S0 | Read/Write | These bits are used in conjunction with CSRB bits<07:00> to program interrupt control group 1. They contain status information when read and command words when written. Unaffected by BINIT. (See Paragraphs 2.4.5.1 and 2.4.5.2 for status and command definitions.)                                                                                                                                                                                                                     |

| 08    | DIR A     | Read/Write | DIRECTION A. Used for controlling DBRA. This bit, in conjunction<br>with the USER RDY signal, controls the direction of data transfer. When<br>the DIR bit is cleared, the DRV11J RDY output signal is asserted and the<br>DRV11-J is the input device. When this bit is set and the USER RDY<br>signal is asserted, the DRV11-J is the output device. The negation of either<br>DIR or USER RDY causes the DRV11-J outputs to remain in their high-<br>impedance state. Cleared by BINIT. |

| 09    | IE        | Read/Write | INTERRUPT ENABLE. Enables the DRV11-J to generate processor in-<br>terrupts when set. Used to enable both group 1 and group 2 interrupts.<br>Cleared by BINIT.                                                                                                                                                                                                                                                                                                                             |

| 14:10 |           |            | Unused. Read as 0s.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 15    | RDY A     | Read Only  | USER READY A. Used for controlling DBRA. When read, this bit yields<br>the state of the USER RDY signal. A 0 means negated and a 1 means<br>asserted. This bit is used in conjunction with the DIR bit to enable DRV11-<br>J output operations. The user device asserts this signal when it desires the<br>DRV11-J to output data. Unaffected by BINIT.                                                                                                                                    |

Table 2-1 CSRA Bit Functions and Descriptions

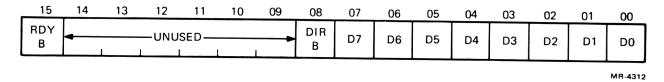

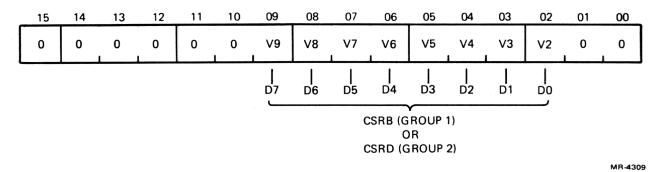

Figure 2-3 CSRB Bit Assignments

| Bit   | Name  | Function   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|-------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 07:00 | D7-D0 | Read/Write | These bits are used in conjunction with CSRA bits <07:00> to program<br>interrupt control group 1. They contain information selected by the com-<br>mand word loaded through CSRA. The registers available are the IRR,<br>ISR, ACR, IMR and the vector address memory. Unaffected by BINIT.<br>(See Paragraphs 2.4.5.4 through 2.4.5.8 for a detailed description of the<br>registers and their functions.)                                                                               |

| 08    | DIR B | Read/Write | DIRECTION B. Used for controlling DBRB. This bit, in conjunction with<br>the USER RDY signal, controls the direction of data transfer. When the<br>DIR bit is cleared, the DRV11J RDY output signal is asserted and the<br>DRV11-J is the input device. When this bit is set and the USER RDY<br>signal is asserted, the DRV11-J is the output device. The negation of either<br>DIR or USER RDY causes the DRV11-J outputs to remain in their high-<br>impedance state. Cleared by BINIT. |

| 14:09 |       |            | Unused. Read as 0s.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 15    | RDY B | Read Only  | USER READY B. Used for controlling DBRB. When read, this bit yields<br>the state of the USER RDY signal. A 0 means negated and a 1 means<br>asserted. This bit is used in conjunction with the DIR bit to enable DRV11-<br>J output operations. The user device asserts this signal when it desires the<br>DRV11-J to output data. Unaffected by BINIT.                                                                                                                                    |

Table 2-2

CSRB Bit Functions and Descriptions

MR-4313

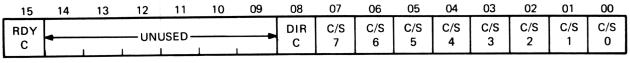

Figure 2-4 CSRC Bit Assignments

| Bit   | Name      | Function   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|-----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 07:00 | C/S7-C/S0 | Read/Write | These bits are used in conjunction with CSRD bits <07:00> to program interrupt control group 2. They contain status information when read and command words when written. Unaffected by BINIT. (See Paragraphs 2.4.5.1 and 2.4.5.2 for status and command definitions.)                                                                                                                                                                                                                    |

| 08    | DIR C     | Read/Write | DIRECTION C. Used for controlling DBRC. This bit, in conjunction with<br>the USER RDY signal, controls the direction of data transfer. When the<br>DIR bit is cleared, the DRV11J RDY output signal is asserted and the<br>DRV11-J is the input device. When this bit is set and the USER RDY<br>signal is asserted, the DRV11-J is the output device. The negation of either<br>DIR or USER RDY causes the DRV11-J outputs to remain in their high-<br>impedance state. Cleared by BINIT. |

| 14:09 |           |            | Unused. Read as 0s.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 15    | RDY C     | Read Only  | USER READY C. Used for controlling DBRC. When read, this bit yields<br>the state of the USER RDY signal. A 0 means negated and a 1 means<br>asserted. This bit is used in conjunction with the DIR bit to enable DRV11-<br>J output operations. The user device asserts this signal when it desires the<br>DRV11-J to output data. Unaffected by BINIT.                                                                                                                                    |

Table 2-3 CSRC Bit Functions and Descriptions

2-5

MR-4314

2

| Bit   | Name  | Function   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|-------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 07:00 | D7-D0 | Read/Write | These bits are used in conjunction with CSRC bits <07:00> to program<br>inter rupt control group 2. They contain information selected by the com-<br>mand word loaded through CSRC. The registers available are the IRR,<br>ISR, ACR, IMR and the vector address memory. (See Paragraphs 2.4.5.4<br>through 2.4.5.8 for a detailed description of the registers and their func-<br>tions.)                                                                                                 |

| 08    | DIR D | Read/Write | DIRECTION D. Used for controlling DBRD. This bit, in conjunction<br>with the USER RDY signal, controls the direction of data transfer. When<br>the DIR bit is cleared, the DRV11J RDY output signal is asserted and the<br>DRV11-J is the input device. When this bit is set and the USER RDY<br>signal is asserted, the DRV11-J is the output device. The negation of either<br>DIR or USER RDY causes the DRV11-J outputs to remain in their high-<br>impedance state. Cleared by BINIT. |

| 14:09 |       |            | Unused. Read as 0s.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 15    | RDY D | Read Only  | USER READY D. Used for controlling DBRD. When read, this bit yields<br>the state of the USER RDY signal. A 0 means negated and a 1 means<br>asserted. This bit is used in conjunction with the DIR bit to enable DRV11-<br>J output operations. The user device asserts this signal when it desires the<br>DRV11-J to output data. Unaffected by BINIT.                                                                                                                                    |

Table 2-4 CSRD Bit Functions and Descriptions

Figure 2-6 Data Buffer Register Bit Assignments

#### 2.4.1 Functional Description

The interrupt control logic shown in Figure 2-1 consists primarily of a DC003 interrupt logic chip and two interrupt controller chips. Five LSI-11 bus control signals (BIRQ 4 L, BIAKI L, BIAKO L, BDIN L and BINIT L) are used by the interrupt control logic for initialization, sending interrupt requests to the processor, receiving the interrupt acknowledge signal from the processor, and sending the vector address to the processor.

Each interrupt controller chip is responsible for monitoring a group of eight interrupt request inputs. Each group of eight interrupt requests is applied via IRQ buffers to an 8-bit interrupt request register (IRR) in the interrupt controller.

The two interrupt controllers (group 1 and group 2) are programmed independently. The group 1 interrupt controller is programmed through the low bytes of CSRA and CSRB while the group 2 interrupt controller is programmed through the low bytes of CSRC and CSRD. The only commonalities of the two groups are priority resolution and the interrupt enable (IE) CSRA bit 9. Both interrupt controllers must operate in the same mode, either interrupt or polled. Each interrupt controller contains an 8-bit interrupt mask register (IMR) that may be used to disable the processing of any undesired interrupt requests.

The group 1 interrupt controller has the higher priority and its enable output is connected to the enable input of group 2. Group 1 must be armed to accept interrupts with the master mask bit set in the mode register. When group 1 is armed, its enable output goes high, thus enabling group 2 interrupts. Therefore, whenever the interrupt mode is selected, group 1 must be armed, even if none of the group 1 interrupt requests are being used in order to pass the enable signal along to group 2.

Group 1 and group 2 may be programmed to respond to either an active high or an active low transition on the interrupt request lines. A bit in the interrupt request register (IRR) is set whenever the corresponding interrupt request line makes an inactive-to-active transition and meets the active pulse width requirements. Active pulse widths 270 ns or greater will set the corresponding IRR bit, while pulse widths 30 ns or less are ignored. Active pulse widths between 30 ns and 270 ns may or may not set the IRR bit.

#### 2.4.2 Interrupt Controller Interface

The interconnections between the group 1 and group 2 interrupt controllers, their relation to the DRV11-J A I/O bus and the LSI-11 bus are shown in Figure 2-7. Latched data address line LDAL 3 L or H, along with the SEL 0 L signal, is used to select group 1 for subsequent reading/writing through the low byte of CSRA or CSRB, or group 2 for reading/writing through CSRC or CSRD. Intergroup priority management is controlled by the enable-in (EI), enable-out (EO) and the response-in-progress (RIP) signals. Note that the IAK L, GINT, RIP, and PAUSE lines are respectively tied together. Group 1 is always enabled because its enable-in (EI) pin is floating high. The enable-out (EO) signal of group 1 is connected to the enable-in (EI) pin of group 2.

Figure 2-7 Group 1 and Group 2 Interrupt Controller Interconnections

2-8

Each interrupt controller group accepts eight IRQ inputs through the IRQ buffers. The timing relationship of the signals involved in intergroup priority resolution is shown in Figure 2-8. For purposes of this discussion, suppose that an active interrupt (IRQ 7) arrives at group 1. When IRQ 7 is applied to group 1, a group interrupt (GINT) will be generated if the request is not masked or the master mask bit has not disarmed the interrupt controller. The GINT signal will generate BIRQ 4 L, if the processor has enabled interrupts, by setting the interrupt enable bit. The processor will accept BIRQ 4 L after executing the current instruction, issue BIAK L, and disable its internal interrupt structure. When the processor returns the BIAK L signal, EO of group 1 goes low. PAUSE goes low to indicate that a data bus transfer operation is presently under way. The rising edge of PAUSE extends the IAK L pulse and is also ANDed with the RPLY signal of the I/O control logic to delay the assertion of BRPLY until the current data transfer is completed.

After the fall of BIAK L, group 1 and group 2 wait until a brief internal delay elapses and then examine EI. If EI is low, internal activity is suspended until EI goes high. If EI is high, the internal circuitry is checked to see if an unmasked interrupt request is pending. In this example, EI of group 1 is always high and EO stays low after the brief internal delay because of IRQ 7. The low EO signal of group 1 therefore disables group 2. The group 1 RIP signal is brought low, and PAUSE is brought high, causing the IAK signal to go high. When the IAK signal goes high, the vector address programmed for IRQ 7 is output through the vector address buffers and transceivers to the LSI-11 bus. Note that the PAUSE output automatically adjusts the position of its rising edge to accommodate the particular intergroup and intragroup priority resolution conditions that occur for each IAK cycle.

The RIP output serves two basic functions within the interrupt system. First, its falling edge informs the other interrupt controller that an interrupt request has been selected and PAUSE may therefore be released. Second, as long as RIP is low, only the interrupt controller that is causing RIP to go low is allowed to respond to IAK L inputs. RIP stays low until the vector address for the selected interrupt has been transferred. Suppose that a new interrupt request arrives at IRQ 0 of the group 2 interrupt controller during the time the vector address of group 1 is being transferred. Without the RIP signal there would be confusion when IRQ 0 arrives at the group 2 interrupt controller. The group 2 interrupt controller treats RIP as an input, and therefore, will not respond to IRQ 0 until RIP goes high.

#### 2.4.3 Interrupt Controller Operating Description

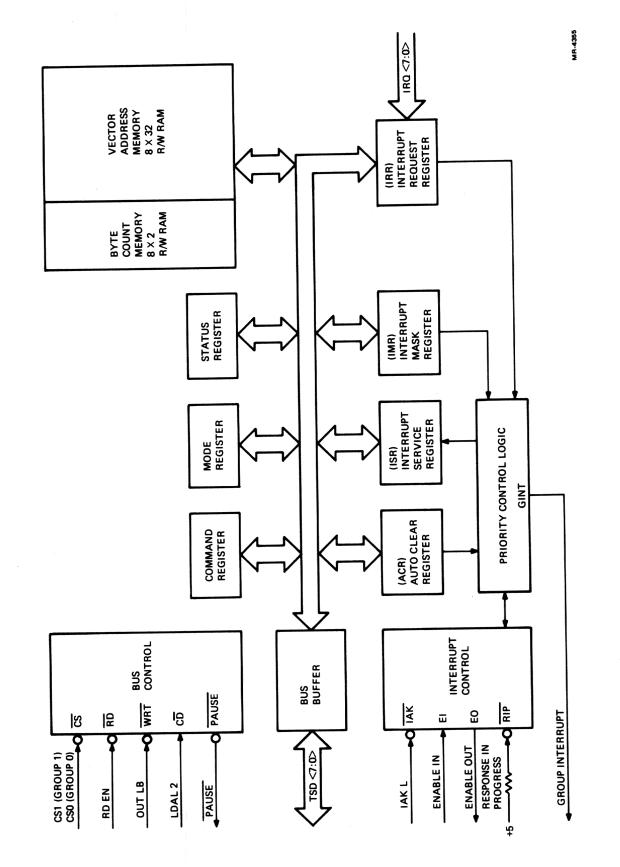

The block diagram Figure 2-9 shows the registers, interface signals and basic information flow of an interrupt controller chip. The interrupt controller chips for group 1 and group 2 are identical and the following description applies to both. Interrupt requests (IRQ <7:0>) are captured and latched in the interrupt request register (IRR). Any requests not masked by the interrupt mask register (IMR) will cause a group interrupt (GINT) output to the processor if the interrupt controller is enabled, armed, and IE (CSRA) bit 9 is set. When the processor is ready to accept the interrupt, it issues an IAK L pulse that initiates two operations. First, the priority of pending interrupts is resolved, and second, the vector address associated with the highest priority interrupt is transferred from the vector address memory to the data bus (TSD <7:0>).

Other interrupt management functions are controlled by the auto-clear register (ACR), the interrupt service register (ISR), and the mode register (MR). The command register is used by the processor to exercise control over the many functions provided by the DRV11-J, while the status register reports on the internal condition of the DRV11-J.

The interrupt controller is addressed by the processor as either a control port or a data port through use of the LDAL 2 bit. The control port provides direct access to the command register and the status register. The data port is used to communicate with all other internal locations.

EI OF GROUP 1 IS OPEN AND ALWAYS ENABLED.

MR-4735

Figure 2-8 Intergroup Priority Resolution Timing

Figure 2-9 Interrupt Controller Block Diagram

2-11

Information is transferred through the interrupt controllers, the DRV11-J I/O bus, and the LSI-11 bus by the eight 3-state bidirectional data bus lines (TSD <7:0>). Control signal configurations for all information transfer operations are described in Table 2-5. The following conventions are assumed: RD EN and OUT LB are mutually exclusive; RD EN, OUT LB, and LDAL 2 have no meaning unless CS1 or CS0 is low; active IAK L pulses occur only when CS1 or CS0 is high.

|            |        | <b>Control Input</b> |        |       |                                                                                       |  |  |  |

|------------|--------|----------------------|--------|-------|---------------------------------------------------------------------------------------|--|--|--|

| CS0<br>CS1 | LDAL 2 | RD EN                | OUT LB | IAK L | - TSD <7:0> Data Bus Operation                                                        |  |  |  |

| 0          | 0      | 0                    | 1      | 1     | Transfer contents of preselected data register to data bus (read).                    |  |  |  |

| 0          | 0      | 1                    | 0      | 1     | Transfer contents of data bus to preselected data register (write).                   |  |  |  |

| 0          | 1      | 0                    | 1      | 1     | Transfer contents of status register to data bus (read).                              |  |  |  |

| 0          | 1      | 1 .                  | 0      | 1     | Transfer contents of data bus to command register (write).                            |  |  |  |

| 1          | x      | x                    | х      | 0     | Transfer contents of selected vector address memory loca-<br>tion to data bus (read). |  |  |  |

| 1          | х      | x                    | x      | 1     | No information transferred.                                                           |  |  |  |

Table 2-5 Summary of Data Bus Transfers

NOTE: X = "don't care" condition; LDAL = 1 = control port; 0 = data port.

The status register is selected directly for reading by the LDAL control input. Other internal registers are read by preselecting the desired register with mode bits 5 and 6, and then executing a data read. The vector address memory can be read only with IAK L pulses.

The command register is selected directly for writing by the LDAL 2 control input. The mask and auto-clear registers are loaded following specific commands to that effect. To load each level (IRQ <7:0>) of the vector address memory, the vector address memory preselect command is issued to select the desired level. A data-write operation is then executed to load that level.

#### 2.4.4 Interrupt Control Reset

The DRV11-J does not include an external hardware reset input for the interrupt control. The reset function is accomplished by software command, or automatically during power-up. The processor may initiate a reset at any time by writing all 0s into the command register of each interrupt controller. Power-up reset circuitry on each interrupt controller integrated circuit is internally triggered by the rising  $V_{CC}$  voltage (IC supply voltage, 5 V) to generate a brief reset pulse when the predetermined threshold is reached. The interrupt controllers are unaffected by a BINIT on the LSI-11 bus.

The vector address memory and byte count register contents are not affected by a software reset, but their contents are unpredictable after a power-up reset. Therefore, if the vector address memory and byte count register are to be used, they must be initialized by the processor after power-up.

The interrupt mask register is set to all 1s by either a software reset or a power-up reset, thus disabling recognition of interrupts by the DRV11-J. The status registers continue to reflect the internal condition of group 1 and group 2 and are not otherwise affected by a reset.

The mode registers are cleared to all 0s to provide the DRV11-J with a reasonable operating environment after a power-up or software reset. The mode registers after reset are assigned the following operating options.

> Interrupt mode Individual vectoring Fixed interrupt priority IRQ polarity active low ISR preselected for reading Interrupt controllers disarmed by master mask bit

#### 2.4.5 Interrupt Control Register Description

The DRV11-J uses the control and operation registers, plus the vector address memories of the interrupt controllers, to perform and manage its many functions. Table 2-6 lists these elements and summarizes their size and number.

| Description                | Register<br>Abbreviation | Bit Size<br>Per<br>Register | Quantity<br>Per<br>DRV11-J |

|----------------------------|--------------------------|-----------------------------|----------------------------|

| Interrupt request register | IRR                      | 8                           | 2                          |

| Interrupt service register | ISR                      | 8                           | 2                          |

| Interrupt mask register    | IMR                      | 8                           | 2                          |

| Auto-clear register        | ACR                      | 8                           | 2                          |

| Status register            | _                        | 8                           | 2                          |

| Mode register              | -                        | 8                           | 2                          |

| Command register           | -                        | 8                           | 2                          |

| Byte count                 | _                        | 2                           | 16                         |

| Vector address memory      | -                        | 8 × 32*                     | 16                         |

| Table 2-6 | Interrupt | Control | Register | and | Memory | Summary |

|-----------|-----------|---------|----------|-----|--------|---------|

|-----------|-----------|---------|----------|-----|--------|---------|

\*Although each interrupt controller contains 32 vector address memory locations of 8 bits each, the DRV11-J uses only 8 of these memory locations.

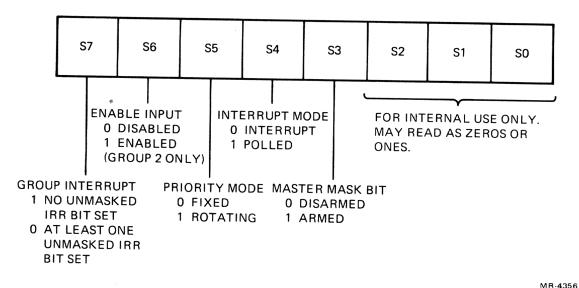

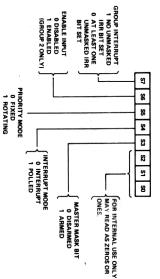

**2.4.5.1** Status Register – Each status register is eight bits wide and contains information describing the internal state of the DRV11-J. The status register is read directly by executing a read operation at CSRA for group 1 or CSRC for group 2. Figure 2-10 shows the status register bit assignments.

The high-order status bit S7 reflects the information state of the group interrupt (GINT) signal. Bit S7 remains valid when interrupts are disabled by the polled mode option, thus permitting the processor to check for interrupts by reading the status register.

Status bit S6 reflects the state of the enable-in (EI) input signal and indicates if group 2 is enabled or disabled. When S6 is high, group 2 can generate an interrupt request. When S6 is low, group 2 interrupt requests are disabled. Group 1 is always enabled.

Status bit S5 reflects the state of the priority mode option as specified by mode register bit M0. When S5 is high, rotating priority is selected. When S5 is low, fixed priority is selected.

Status bit S4 reflects the state of the interrupt mode option as specified by mode register bit 2. When S4 is high, the polled mode is selected and interrupt requests are disabled. When S4 is low, the interrupt mode is selected.

Figure 2-10 CSRA and CSRC Status Registers' Bit Assignments

Status bit S3 reflects the state of the master mask bit as specified by mode register bit M7. When S3 is low, the group is disarmed and IRR bits that are set will not generate interrupt requests. When S3 is high, the group is armed and interrupts can occur.

Status bits S2, S1 and S0 are for internal use by the DRV11-J. These bits may read as zeros or ones and should not be correlated with external events or operational states of the module.

**2.4.5.2** Command Register – Each command register is eight bits wide and is used to store the most recently entered command. The register is loaded directly from the data bus by executing a write operation at CSRA for group 1 or CSRC for group 2. Depending on the specific command opcode that is entered, an immediate internal activity may be initiated, or CSRB and CSRD may be preconditioned for subsequent register transfers. The opcodes for each command operation are described in Paragraph 2.7. (The commands are summarized in Table 2-10.)

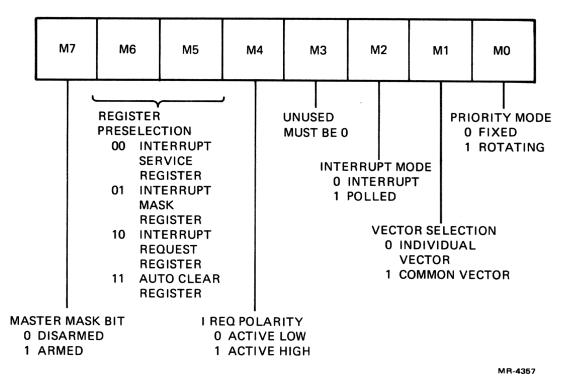

**2.4.5.3** Mode Register – Each mode register is eight bits wide and is used to establish the operating modes and conditions for the many functional features of the DRV11-J. The mode register allows the processor to customize the interrupt system for a particular application. Figure 2-11 shows the mode register bit assignments. No single command or interface operation will load all bits of the mode register in parallel. The five low-order bits (M0 through M4) are loaded in parallel directly from the command register. Mode bits M5, M6 and M7 are controlled by separate commands. The mode register contents cannot be read out on the data bus. However, the conditions of mode bits M0, M2 and M7, which reflect the priority, interrupt and master mask bit modes, are available as part of the status register. The mode register is cleared by a software reset or a power-up reset.

**2.4.5.4** Interrupt Request Register (IRR) – Each IRR is eight bits wide and is used to recognize and store active transitions on the eight interrupt request lines. A bit in the IRR is set whenever the corresponding IRQ input line makes an inactive-to-active transition and meets the minimum active

pulse width requirements. Also, the processor (under program control) may set the IRR bits by using two types of commands. This capability permits software-initiated interrupts and is a useful tool for system testing.

All IRR bits are cleared by a reset. Individual IRR bits are cleared automatically when their interrupts are acknowledged by the processor. Four types of commands, in addition to reset, allow the processor to clear IRR bits.

The IRR may be read onto the data bus by preselecting it in mode register bits M5 and M6 with a load mode register command, followed by a read of CRSB <7:0> for group 1 or CSRD <7:0> for group 2.

Figure 2-11 Mode Register Bit Assignments

**2.4.5.5** Interrupt Service Register (ISR) – Each ISR is eight bits wide and is used to store the acknowledge status of individual interrupts. When the processor acknowledges an interrupt request, the DRV11-J selects the highest priority request that is pending, clears the associated IRR bit, and sets the associated ISR bit. When the ISR bit is programmed for automatic clearing, it is reset by the internal hardware before the end of the acknowledge sequence. When the ISR bit is not programmed for automatic clearing, it must be reset by command from the processor.

The DRV11-J uses the ISR internally to erect a "masking fence." When an ISR bit is set and fixed priority mode is selected, only requests of higher priority will cause a new group interrupt (GINT) output. Thus, requests from lower priority interrupts (and from new requests associated with the set ISR bit) will be "fenced out" and ignored until the ISR bit is cleared. In the rotating priority mode, all requests are fenced out by an ISR bit that is set and no new interrupts will be generated until the ISR bit is cleared. When automatic clearing is specified, no masking fence is erected since the ISR bit is cleared.

If an unmasked interrupt arrives from a device of higher priority than the current ISR, the processor will be interrupted if its interrupt input is enabled. When the new interrupt is acknowledged, the associated higher priority ISR bit is set and the fence moves up to the new priority level. When the new ISR bit is cleared, the fence will then fall back to the previous ISR level. The ISR may be read onto the data bus by preselecting it in mode register bits M5 and M6 with a load mode register command, followed by a read of CSRB <7:0> for group 1 or CSRD <7:0> for group 2.

**2.4.5.6** Interrupt Mask Register (IMR) – Each IMR is eight bits wide and is used to enable/disable the processing of individual interrupts. Only unmasked IRR bits can generate an interrupt. The IMR does not otherwise affect the operation of the IRR. An IRR bit that is set while masked will cause an interrupt when its IMR bit is cleared.

All eight IMR bits for each group may be set, cleared, read or loaded in parallel by the processor. In addition, individual IMR bits may be set or cleared by command. This allows a control routine to enable or disable directly an individual interrupt without disturbing the other mask bits and without knowledge of their state or context.

The IMR polarity is active high for masking; a 0 enables the interrupt and a 1 disables it. The poweron reset and the software reset cause all IMR bits to be set, thus disabling all interrupt requests. The IMR may be read onto the data bus by preselecting it in mode register bits M5 and M6 with a load mode register command, followed by a read of CSRB <7:0> for group 1 or CSRD <7:0> for group 2.

**2.4.5.7** Auto-Clear Register (ACR) – Each ACR is eight bits wide and specifies the automatic clearing option for each of the ISR bits. When an auto-clear bit is set, the corresponding ISR bit set in an interrupt acknowledge (IAK) cycle is cleared by the internal hardware before the end of the IAK sequence. When an auto-clear bit is not set, the corresponding ISR bit that has been set in an IAK cycle is cleared by a command from the processor.

When selected, the auto-clear option provides two related functional effects. First, it eliminates the need for the associated interrupt service routine to issue a command to clear the ISR bit. Second, it eliminates the masking fence that would otherwise have been erected, allowing lower priority interrupts to cause a new interrupt request.

The ACR is loaded in parallel from the data bus by issuing the ACR load preselect command, followed by a write into the data port. The ACR is read onto the data bus by preselecting it in mode register bits M5 and M6 with a load mode register command, followed by a read of CRSB <7:0> for group 1 or CSRD <7:0> for group 2.

**2.4.5.8** Vector Address Memory – The vector addresses are programmed by the vector address memory preselect command, followed by a data-write operation to load the vector address required for each interrupt request level. The vector address memory preselect command is entered directly into the low byte <7:0> of CSRA for group 1 or the low byte <7:0> of CSRC for group 2. Preselect commands entered through CSRA select CSRB for subsequent loading of the vector addresses in group 1. Preselect commands entered through CSRC select CSRD to load the addresses for group 2.

Normally, one vector address is loaded after each preselection command. (Figure 2-12 shows the vector bit positions relative to the loaded byte.) This in turn causes one interrupt to occur for each valid transition on the corresponding IRQ input. Vector addresses are placed on the LSI-11 bus during IAK operation.

Loading the vector address into each new interrupt request level must be preceded by a new vector address memory preselect command. Therefore, 16 preselect commands, each followed by a data-write operation, are required to load 16 vector addresses into the vector address memory.

Note that while the DRV11-J only uses one vector address per interrupt, the interrupt controller chips are capable of handling four vector addresses per interrupt level. To ensure proper operation, the user must always use a byte count of one (BY0 = 0, BY1 = 0) and load only one data byte after each preselect command.

Figure 2-12 DRV11-J Vector Address Format

#### 2.5 OPERATING OPTIONS

The mode register bits are program-controlled to establish the combination of interrupt operating options desired for a particular DRV11-J system application. Refer to Figure 2-11 for the mode register bit assignments. A detailed description of the various options available follows. The master mask bit will affect both group 1 and group 2; all other mode bits affect only their corresponding groups.

#### 2.5.1 Interrupt Priority Mode Selection

Mode register bit M0 specifies either a fixed or rotating priority resolution mode for the DRV11-J. When M0 is low, fixed priority is selected and the eight IRQ inputs for both group 1 and group 2 are assigned a priority based on their physical location at the interface. Group 1 IRQ 0 has the highest priority and group 2 IRQ 7 has the lowest. Table 2-7 lists the priorities assigned to the A I/O <15:0> lines and the USER RPLY lines.

| Group | Connection     | Level | IRR, ISR<br>Bit Assign | Priority |         |

|-------|----------------|-------|------------------------|----------|---------|

| 1     | A I/O 0        | 0     | D0                     | <u>۱</u> | Highest |

| 1     | <b>A</b> I/O 1 | 1     | D1                     |          | •       |

| 1     | A I/O 2        | 2     | D2                     |          |         |

| 1     | A I/O 3        | 3     | D3                     | CSRB     |         |

| 1     | A I/O 4        | 4     | D4                     | CSKB     |         |

| 1     | A I/O 5        | 5     | D5                     |          |         |

| 1     | A I/O 6        | 6     | D6                     |          |         |

| 1     | A I/O 7        | 7     | D7                     | )        |         |

| 2     | A I/O 8        | 0     | D0                     |          |         |

| 2     | A I/O 9        | 1     | D1                     |          |         |

| 2     | A I/O 10       | 2     | D2                     |          |         |

| 2     | A I/O 11       | 3     | D3                     | CSPD     |         |

| 2     | USER RPLY A    | 4*    | D4                     | CSRD     |         |

| 2     | USER RPLY B    | 5*    | D5                     |          |         |

| 2     | USER RPLY C    | 6*    | D6                     |          |         |

| 2     | USER RPLY D    | 7*    | D7                     | J        | Lowest  |

| Table | 2-7 | Fixed | Priority | Mode |

|-------|-----|-------|----------|------|

|-------|-----|-------|----------|------|

\*Jumper (W11) selects either USER RPLY (A:D) or A I/O <15:12> signals.

Interrupt acknowledge operations are initiated by the processor in response to a group interrupt (GINT) output by the interrupt controllers.

Interrupt priority is resolved after the processor initiates the interrupt acknowledge sequence. When the DRV11-J receives an IAK signal, the interrupt controllers perform priority arbitration to select the highest unmasked pending interrupt, and then output a vector address associated with the selected interrupt request. In the fixed priority mode, therefore, devices with a high priority may be serviced many times before a lower priority device is serviced once. In many systems, this is an appropriate method of servicing the interrupting devices. In those systems where this is not an appropriate method, the interrupt masking capability of the DRV11-J may be used to modify the effective priority structure. This may be accomplished by masking out recently serviced high priority devices, thus permitting recognition of lower priority inputs.

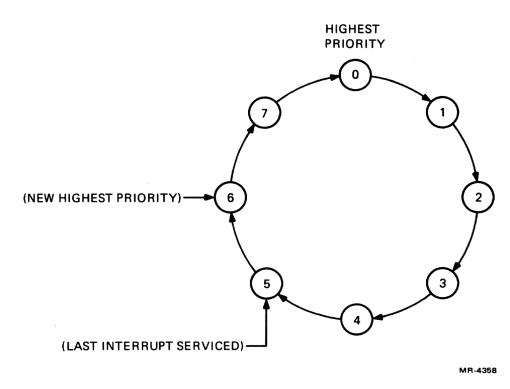

Alternatively, the rotating priority mode may be selected for use in systems where the eight interrupts of each group have similar priority and bandwidth requirements. Mode register bit M0 = 1 selects the rotating priority mode. As shown in Figure 2-13, the relative priorities remain the same as in the fixed mode. In the rotating priority mode, however, the lowest priority position in the circular chain is assigned by the hardware to the most recently serviced interrupt. Priority rotation occurs only within a given group and priority between group 1 and group 2 remains fixed, with group 1 having the higher priority.

Figure 2-13 Rotating Priority Mode

The example shown in Figure 2-13 assumes IRQ 5 has been serviced and is assigned the lowest priority (7). IRQ 6 now occupies the new highest priority position, IRQ 7 next to the highest, etc. If two new interrupts simultaneously arrive at IRQ 1 and IRQ 4, IRQ 1 is selected and becomes the lowest priority. IRQ 4 will then be acknowledged unless an active input of IRQ 2 or IRQ 3 arrives in the meantime.

This rotating scheme prevents any one interrupt request from dominating the system. An interrupt request will not have to wait for more than seven more service cycles before being acknowledged. Priority is resolved when the ISR bit of the presently selected interrupt is cleared.

In the rotating priority mode, inputs other than the one currently serviced are fenced out and will not cause interrupts until the ISR bit is cleared. Thus, only one bit at a time is set in the ISR. Use care when selecting the rotating mode to keep from doing so again when more than one ISR is set.

#### 2.5.2 Individual Vector or Common Vector Mode

Bit M1 of the mode register specifies the vectoring option. When M1 = 0, the individual vector mode is selected and each interrupt request line is associated with its own location in the vector address memory. Each location contains the vector address that was loaded by the program after system power-up.

When M1 = 1, the common vector mode is selected and all vector information is supplied from the vector address memory location associated with interrupt request line 0 (IRQ 0), regardless of which interrupt request line is acknowledged. The common vector mode is useful in systems where several similar devices share a common service routine and direct individual device identification is not important. This may be true because of the nature of the peripheral-system interaction or in the case of a transient system condition that uses the common vector temporarily to save the additional programming overhead required to load the vector address memory twice per group.

#### 2.5.3 Interrupt or Polled (Flag) Mode

Bit 2 of the mode register allows the system to enable or disable interrupt requests. When M2 = 0, the interrupt mode is selected and interrupts are enabled. The interrupt mode may be considered the "normal" mode because it permits full use of the interrupt control and management capabilities of the DRV11-J.

When M2 = 1, the polled mode is selected, which forces the group interrupt (GINT) output of the interrupt controllers to the inactive state and thus prevents the DRV11-J from issuing a bus interrupt request (BIRQ 4 L). Since no bus interrupt requests are supplied, the processor cannot initiate the interrupt acknowledge sequence. Consequently, ISR bits are not set, masking fences are not erected, and IRR bits are not automatically cleared. Polled-mode operation requires the processor to read the status register to determine if requests are pending. Software routines must then be used to determine which input line requested the interrupt. IRR bits may be cleared by the software. The polled mode of operation effectively bypasses the hardware interrupt, vectoring, and fencing functions of the DRV11-J. What remains is the interrupt request latching and masking functions.

#### 2.5.4 Mode Register Bit 3

Bit 3 of the mode register is not used and must be programmed to a 0.

#### 2.5.5 IRQ Polarity Option

Bit 4 of the mode register specifies the polarity of interrupt request inputs to which the DRV11-J will respond. When M4 = 0, the interrupt request inputs are selected as active low and a negative-going transition is required to set the associated IRR bits. When M4 = 1, the interrupt request inputs are selected as active high and a positive-going transition is required to set the associated IRR bits. This polarity option may be used to simplify the design of the DRV11-J interface to the interrupting devices.

#### 2.5.6 Register Preselection Option

Bits 5 and 6 of the mode register specify the internal data register contents that will be output by the DRV11-J during a read operation at the data port. These bits do not affect destinations for write operations. The four registers that may be read are the IRR, ISR, IMR and ACR. Preselect coding for each register is shown in Figure 2-11. The preselection remains in effect for all data transfers until the contents of M5 and M6 are changed.

The ability to examine these operating registers in conjunction with the status register contents provides important information regarding the current internal conditions of the DRV11-J. The processor's access to these registers permits dynamic operating flexibility and provides important diagnostic, testing, and debugging information.

#### 2.5.7 Master Mask Option

Bit 7 of the mode register specifies the armed status of the DRV11-J by way of the master mask control bit. When M7 = 0, the group is disarmed as if all eight bits in the IMR had been set. IRQ inputs will be accepted and latched but will not be sent to the processor. When M7 = 1, the group is armed and any active unmasked interrupt inputs may cause interrupt requests to the processor.

The master mask option permits the system to disarm a group and prevent the processing of interrupts without disturbing the contents of the IMR. Thus, when the group is re-armed, the old IMR conditions are still valid and need not be reloaded. Note that a single command to the master mask bit of the highest priority interrupt group shuts down the entire interrupt system. This is the only mode bit that affects both groups.

#### 2.6 SYSTEM OPERATING SEQUENCE

The management of interrupts by the DRV11-J requires interaction between the processor, the DRV11-J, and the user device. The operations performed by the system are described in the following typical sequence of events. The DRV11-J is initialized, enabled, and ready to run in the interrupt mode. The processor has enabled its internal interrupt structure to accept DRV11-J interrupt requests.

- 1. One (or more) of the IRQ inputs becomes active, indicating that service is desired.

- 2. The requests are captured and latched in the IRR asynchronously. The latching action of the IRR cannot be disabled and active requests will always be stored unless a previous request at the same IRR bit has not been cleared.

- 3. If the active IRR bit is masked by the corresponding bit in the IMR, no further action takes place. When the IRR bit is not masked, an interrupt request will be generated.

- 4. When the processor recognizes an interrupt request, it will complete the execution of its current instruction and then execute an interrupt acknowledge cycle.

- 5. When BIAKI L is received, the DRV11-J begins selection of the highest priority unmasked IRR bit. All interrupts that have become active before the falling edge of BIAK are considered. When selection is complete, the contents of the vector address memory location associated with the selected request are accessed.

- 6. The processor accepts the vector address on the LSI-11 bus and negates IAK.

- 7. In parallel with the transfer of the vector address, the DRV11-J automatically clears the selected IRR bit and sets the selected ISR bit. If the auto-clear function is not in force for the selected interrupt, the ISR bit will cause the erection of a masking fence, and interrupts will be disabled until a higher priority interrupt arrives or until the ISR bit is cleared. The interrupt service routine must clear the ISR bit near the end of the routine if the auto-clear function is not used.

- 8. If a higher priority request arrives while the current request is being serviced, and if the fixed priority mode is in effect, the DRV11-J will output another interrupt request (nested interrupt). The processor will recognize the interrupt signal only if it has enabled its internal interrupt logic. If this new request is acknowledged, the DRV11-J will clear the corresponding IRR bit and set the corresponding ISR bit.

9. When the processor has completed all service associated with the interrupt, it will clear the remaining ISR bit (if the auto-clear capability is not used), enable its internal interrupt system (if it has not already done so), and return to the main program.

#### 2.7 COMMAND DESCRIPTIONS

The DRV11-J command set allows the processor to customize the interrupt operating modes and options for a particular application. Commands are also used to initialize and update the vector address memory locations and to manipulate the internal controlling bits set during interrupt servicing. Commands are entered directly into the command register by writing into the low byte of CSRA for group 1 or CSRC for group 2. Preselection commands entered through CSRA select CSRB for subsequent group 1 register transfers. Preselection commands entered through CSRC select CSRD for subsequent group 2 register transfers. All the available commands are described below and are summarized in Table 2-10. An "X" in any bit position of the command code indicates a "don't care" condition. Any commands that alter the state of the IMR, IRR or master mask bit should be executed with the processor status word at a priority level equal to the DRV11-J to prevent undefined interrupts from occurring.