# DR11-W Direct Memory Interface Module

User's Guide

# DR11-W Direct Memory Interface Module

User's Guide

### Copyright ©1980, 1981 by Digital Equipment Corporation

### All Rights Reserved

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DIGITAL | DECsystem-10     | MASSBUS |

|---------|------------------|---------|

| DEC     | DECSYSTEM-20     | OMNIBUS |

| PDP     | DIBOL            | OS/8    |

| DECUS   | <b>EDUSYSTEM</b> | RSTS    |

| UNIBUS  | VAX              | RSX     |

|         | VMS              | IAS     |

## **CONTENTS**

|           |                                            | Page       |

|-----------|--------------------------------------------|------------|

| CHAPTER 1 | INTRODUCTION                               | . 1-1      |

| 1.1       | GENERAL                                    |            |

| 1.2       | SUPPORTING DOCUMENTATION                   |            |

| 1.3       | FUNCTIONAL DESCRIPTION                     |            |

| 1.4       | MAINTENANCE MODES                          |            |

| 1.5       | COMPATIBILITY OF DR11-B and DR11-W         |            |

| 1.6       | PHYSICAL DESCRIPTION                       |            |

| CHAPTER 2 | SOFTWARE INTERFACE                         | . 2-1      |

| 2.1       | GENERAL                                    |            |

| 2.2       | WORD COUNT REGISTER (WCR)                  |            |

| 2.3       | BUS ADDRESS REGISTER(BAR)                  |            |

| 2.4       | INPUT DATA REGISTER/OUTPUT DATA REGISTER   | 1          |

| 2.1       | (IDR/ODR)                                  | . 2-2      |

| 2.4.1     | Input Data Register (IDR)                  |            |

| 2.4.2     | Output Data Register (ODR)                 | 2-2        |

| 2.5       | CONTROL AND STATUS REGISTER/ERROR AND      | . 2-2      |

| 2.3       | INFORMATION REGISTER (CSR/EIR)             | 2-2        |

| 2.5.1     | Control and Status Register (CSR)          |            |

| 2.5.2     | Error and Information Register (EIR)       | 2-2<br>2-2 |

| 2.3.2     | Error and finormation Register (ETR)       | L-L        |

| CHAPTER 3 | I/O SIGNALS                                | . 3-1      |

| CHAPTER 4 | THEORY OF OPERATION                        |            |

| 4.1       | GENERAL                                    |            |

| 4.2       | PROGRAMMED DATA TRANSFERS                  | 4-1        |

| 4.3       | INTERRUPT OPERATION                        | . 4-5      |

| 4.4       | DMA OPERATION                              | . 4-5      |

| CHAPTER 5 | INTERFACING AND PROGRAMMING CONSIDERATIONS |            |

| 5.1       | USER-DEVICE CABLES                         |            |

| 5.2       | USER-DEVICE SIGNAL INTERFACE               | 5-1        |

| 5.3       | I/O SIGNAL TIMING                          |            |

| 5.4       | SIGNAL INTEGRITY                           | . 5-2      |

| 5.5       | PROGRAMMING CONSIDERATIONS                 |            |

| 5.5.1     | DR11-W Mode                                | . 5-3      |

| 5.5.2     | Timing                                     | . 5-4      |

| 5.5.3     | Programming Example                        | . 5-4      |

| CHAPTER 6 | INSTALLATION                               |            |

| 6.1       | UNPACKING AND INSPECTION                   | 6-1        |

| 6.1.1     | Unpacking                                  | . 6-1      |

| 6.1.2     | Inspection                                 | . 6-1      |

| 6.2       | INSTALLATION PROCEDURE                     | . 6-1      |

| 6.3       | ACCEPTANCE TESTING                         |            |

| CHAPTER 7                                                                                                                         | INTERPROCESSOR LINKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7-1                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| 7.1                                                                                                                               | GENERAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7-1                                                                                                          |

| 7.2                                                                                                                               | OPERATING MODES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7-1                                                                                                          |

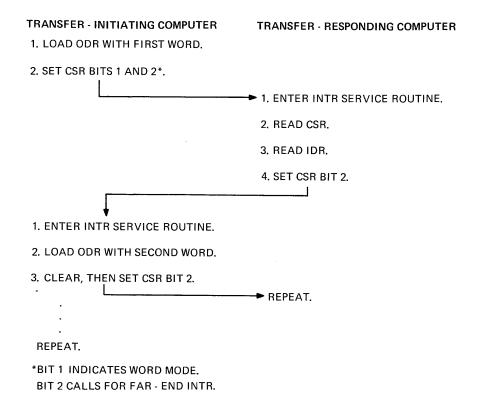

| 7.2.1                                                                                                                             | Word Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7-2                                                                                                          |

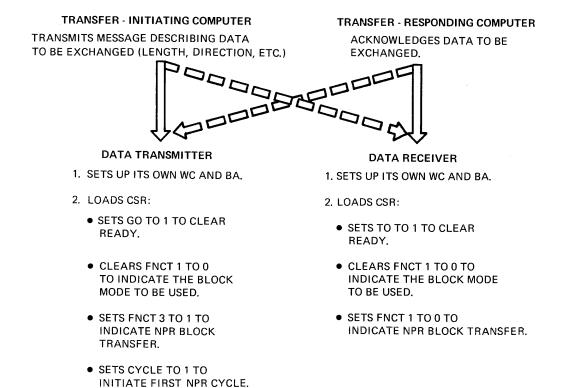

| 7.2.2                                                                                                                             | Block Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7-2                                                                                                          |

| 7.2.3                                                                                                                             | Burst Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7-4                                                                                                          |

| 7.3                                                                                                                               | PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7-4                                                                                                          |

| 7.3.1                                                                                                                             | Word Count Register (WCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7-4                                                                                                          |

| 7.3.2                                                                                                                             | Bus Address Register (BAR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7-4                                                                                                          |

| 7.3.3                                                                                                                             | Output Data Register/Input Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ,                                                                                                            |

| 7.5.5                                                                                                                             | (ODR/IDR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7-4                                                                                                          |

| 7.3.4                                                                                                                             | Control and Status Register (CSR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7-4                                                                                                          |

| 7.3.5                                                                                                                             | Error and Information Register (EIR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7-4                                                                                                          |

| 7.5.5                                                                                                                             | Error and information Register (ETR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7-6                                                                                                          |

| CHAPTER 8                                                                                                                         | MAINTENANCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8-1                                                                                                          |

| 8.1                                                                                                                               | GENERAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                              |

| 8.2                                                                                                                               | ABSTRACTS OF DIAGNOSTIC PROGRAMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8-1                                                                                                          |

| 8.2.1                                                                                                                             | Dragnon for DDD 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8-1                                                                                                          |

|                                                                                                                                   | Programs for PDP-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8-1                                                                                                          |

| 8.2.2                                                                                                                             | Programs for VAX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8-2                                                                                                          |

|                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                              |

| ADDENIDINA                                                                                                                        | I/O CICNIAI DINI ACCIONIMENTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                              |

| APPENDIX A                                                                                                                        | I/O SIGNAL PIN ASSIGNMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | A-l                                                                                                          |

| APPENDIX B                                                                                                                        | SIGNAL CROSS-REFERENCE (DR11-B/DR11-W)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | B-1                                                                                                          |

| APPENDIX C                                                                                                                        | DR11-B/DR11-W FUNCTIONALITY COMPARISON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | C-1                                                                                                          |

|                                                                                                                                   | <b>FIGURES</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                              |

| Figure No.                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Pagg                                                                                                         |

| Figure No.                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Page                                                                                                         |

| Ü                                                                                                                                 | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Ŭ                                                                                                            |

| 1-1                                                                                                                               | Title DR11-W DMA Module M8716                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Ŭ                                                                                                            |

| Ü                                                                                                                                 | Title  DR11-W DMA Module M8716 Simplified Block Diagram of DR11-W Used as                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1-3                                                                                                          |

| 1-1<br>1-2                                                                                                                        | Title  DR11-W DMA Module M8716  Simplified Block Diagram of DR11-W Used as Interface for UNIBUS and User Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1-3                                                                                                          |

| 1-1<br>1-2<br>1-3                                                                                                                 | Title  DR11-W DMA Module M8716  Simplified Block Diagram of DR11-W Used as Interface for UNIBUS and User Device Interface Configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1-3<br>1-4<br>1-5                                                                                            |

| 1-1<br>1-2<br>1-3<br>2-1                                                                                                          | Title  DR11-W DMA Module M8716 Simplified Block Diagram of DR11-W Used as Interface for UNIBUS and User Device Interface Configurations Control and Status Register (CSR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1-3<br>1-4<br>1-5<br>2-3                                                                                     |

| 1-1<br>1-2<br>1-3<br>2-1<br>2-2                                                                                                   | Title  DR11-W DMA Module M8716 Simplified Block Diagram of DR11-W Used as Interface for UNIBUS and User Device Interface Configurations Control and Status Register (CSR) Error and Information Register (EIR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-3<br>1-4<br>1-5<br>2-3<br>2-5                                                                              |

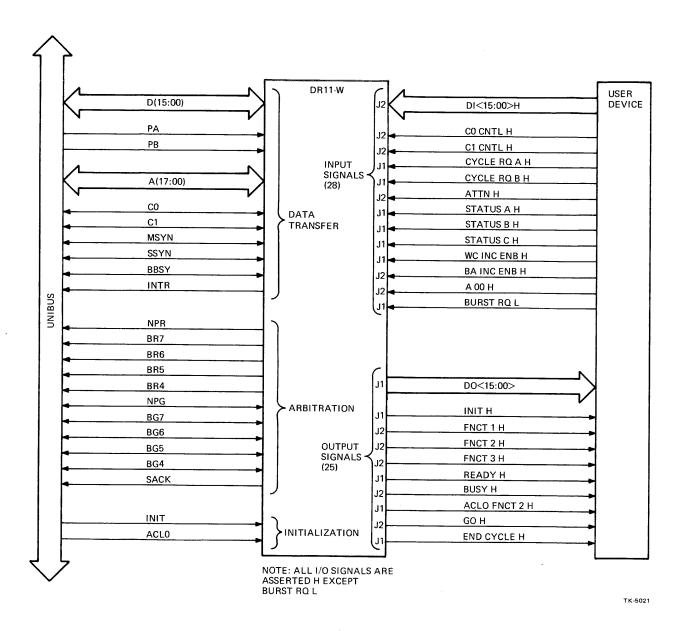

| 1-1<br>1-2<br>1-3<br>2-1<br>2-2<br>3-1                                                                                            | Title  DR11-W DMA Module M8716 Simplified Block Diagram of DR11-W Used as Interface for UNIBUS and User Device Interface Configurations Control and Status Register (CSR) Error and Information Register (EIR) DR11-W I/O Lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1-3<br>1-4<br>1-5<br>2-3<br>2-5<br>3-2                                                                       |

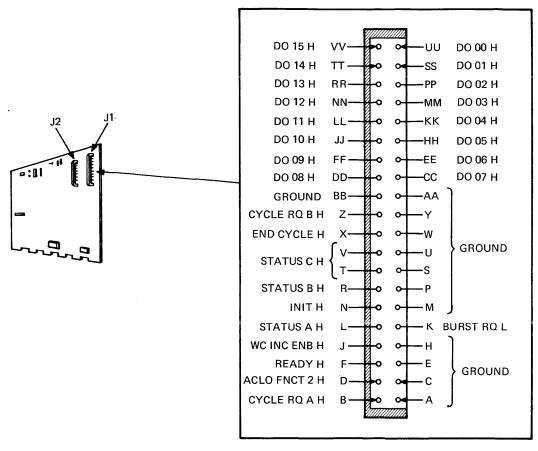

| 1-1<br>1-2<br>1-3<br>2-1<br>2-2<br>3-1<br>3-2                                                                                     | Title  DR11-W DMA Module M8716 Simplified Block Diagram of DR11-W Used as Interface for UNIBUS and User Device Interface Configurations Control and Status Register (CSR) Error and Information Register (EIR) DR11-W I/O Lines Output Connector J1: Signal Pin Assignments                                                                                                                                                                                                                                                                                                                                                                                                                              | 1-3<br>1-4<br>1-5<br>2-3<br>2-5<br>3-2<br>3-5                                                                |

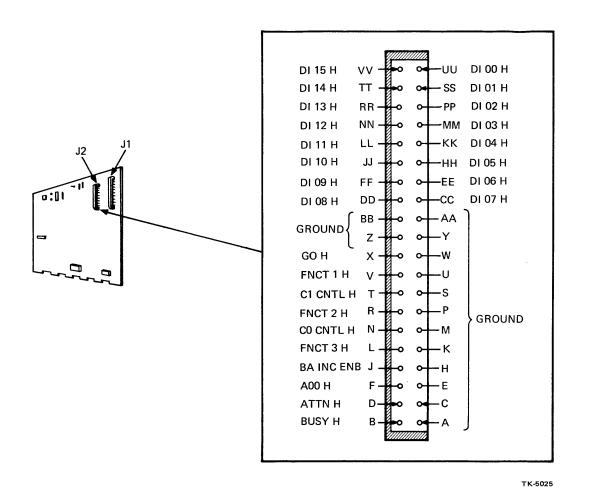

| 1-1<br>1-2<br>1-3<br>2-1<br>2-2<br>3-1<br>3-2<br>3-3                                                                              | Title  DR11-W DMA Module M8716 Simplified Block Diagram of DR11-W Used as Interface for UNIBUS and User Device Interface Configurations Control and Status Register (CSR) Error and Information Register (EIR) DR11-W I/O Lines Output Connector J1: Signal Pin Assignments Input Connector J2: Signal Pin Assignments                                                                                                                                                                                                                                                                                                                                                                                   | 1-3<br>1-4<br>1-5<br>2-3<br>2-5<br>3-2<br>3-5<br>3-6                                                         |

| 1-1<br>1-2<br>1-3<br>2-1<br>2-2<br>3-1<br>3-2<br>3-3<br>4-1                                                                       | Title  DR11-W DMA Module M8716 Simplified Block Diagram of DR11-W Used as Interface for UNIBUS and User Device Interface Configurations Control and Status Register (CSR) Error and Information Register (EIR) DR11-W I/O Lines Output Connector J1: Signal Pin Assignments Input Connector J2: Signal Pin Assignments DR11-W Block Diagram                                                                                                                                                                                                                                                                                                                                                              | 1-3<br>1-4<br>1-5<br>2-3<br>2-5<br>3-2<br>3-5<br>4-2                                                         |

| 1-1<br>1-2<br>1-3<br>2-1<br>2-2<br>3-1<br>3-2<br>3-3<br>4-1<br>4-2                                                                | Title  DR11-W DMA Module M8716 Simplified Block Diagram of DR11-W Used as Interface for UNIBUS and User Device Interface Configurations Control and Status Register (CSR) Error and Information Register (EIR) DR11-W I/O Lines Output Connector J1: Signal Pin Assignments Input Connector J2: Signal Pin Assignments DR11-W Block Diagram Addressing Decoding Logic                                                                                                                                                                                                                                                                                                                                    | 1-3<br>1-4<br>1-5<br>2-3<br>2-5<br>3-2<br>3-5<br>3-6<br>4-2<br>4-4                                           |

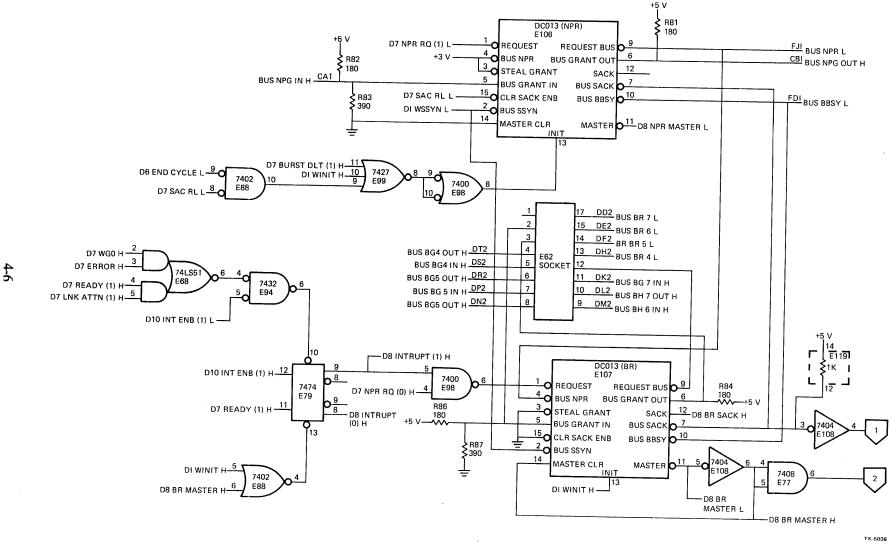

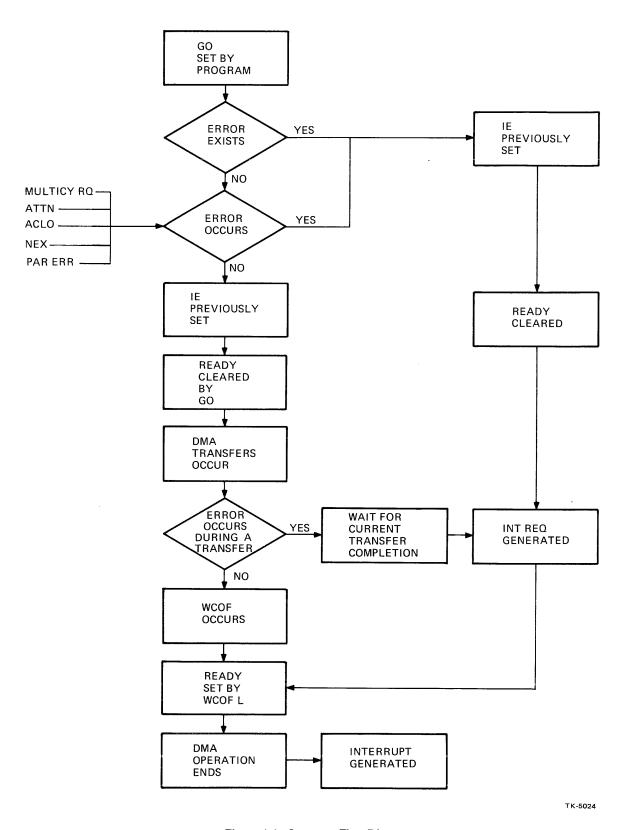

| 1-1<br>1-2<br>1-3<br>2-1<br>2-2<br>3-1<br>3-2<br>3-3<br>4-1<br>4-2<br>4-3                                                         | Title  DR11-W DMA Module M8716 Simplified Block Diagram of DR11-W Used as Interface for UNIBUS and User Device Interface Configurations Control and Status Register (CSR) Error and Information Register (EIR) DR11-W I/O Lines Output Connector J1: Signal Pin Assignments Input Connector J2: Signal Pin Assignments DR11-W Block Diagram Addressing Decoding Logic Interrupt Logic                                                                                                                                                                                                                                                                                                                    | 1-3<br>1-4<br>1-5<br>2-3<br>2-5<br>3-2<br>3-5<br>3-6<br>4-2<br>4-4                                           |

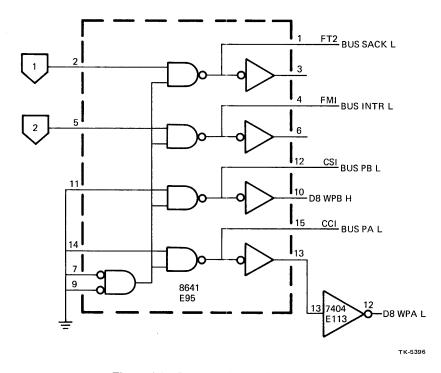

| 1-1<br>1-2<br>1-3<br>2-1<br>2-2<br>3-1<br>3-2<br>3-3<br>4-1<br>4-2<br>4-3<br>4-4                                                  | Title  DR11-W DMA Module M8716 Simplified Block Diagram of DR11-W Used as Interface for UNIBUS and User Device Interface Configurations Control and Status Register (CSR) Error and Information Register (EIR) DR11-W I/O Lines Output Connector J1: Signal Pin Assignments Input Connector J2: Signal Pin Assignments DR11-W Block Diagram Addressing Decoding Logic Interrupt Logic Interrupt Flow Diagram                                                                                                                                                                                                                                                                                             | 1-3<br>1-4<br>1-5<br>2-3<br>2-5<br>3-2<br>3-5<br>3-6<br>4-2<br>4-4                                           |

| 1-1<br>1-2<br>1-3<br>2-1<br>2-2<br>3-1<br>3-2<br>3-3<br>4-1<br>4-2<br>4-3                                                         | Title  DR11-W DMA Module M8716 Simplified Block Diagram of DR11-W Used as Interface for UNIBUS and User Device Interface Configurations Control and Status Register (CSR) Error and Information Register (EIR) DR11-W I/O Lines Output Connector J1: Signal Pin Assignments Input Connector J2: Signal Pin Assignments DR11-W Block Diagram Addressing Decoding Logic Interrupt Logic Interrupt Flow Diagram Interface Circuits for Optimizing DR11-W                                                                                                                                                                                                                                                    | 1-3<br>1-4<br>1-5<br>2-3<br>2-5<br>3-2<br>3-5<br>3-6<br>4-2<br>4-4<br>4-6                                    |

| 1-1<br>1-2<br>1-3<br>2-1<br>2-2<br>3-1<br>3-2<br>3-3<br>4-1<br>4-2<br>4-3<br>4-4<br>5-1                                           | Title  DR11-W DMA Module M8716 Simplified Block Diagram of DR11-W Used as Interface for UNIBUS and User Device Interface Configurations Control and Status Register (CSR) Error and Information Register (EIR). DR11-W I/O Lines Output Connector J1: Signal Pin Assignments Input Connector J2: Signal Pin Assignments DR11-W Block Diagram Addressing Decoding Logic Interrupt Logic Interrupt Flow Diagram Interface Circuits for Optimizing DR11-W Signal-To-Noise Margin                                                                                                                                                                                                                            | 1-3<br>1-4<br>1-5<br>2-3<br>2-5<br>3-2<br>3-5<br>3-6<br>4-2<br>4-4<br>4-6<br>4-8                             |

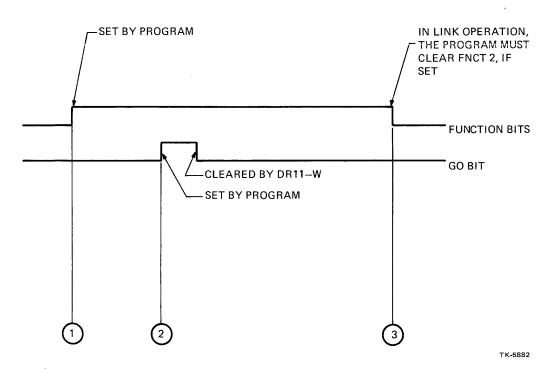

| 1-1<br>1-2<br>1-3<br>2-1<br>2-2<br>3-1<br>3-2<br>3-3<br>4-1<br>4-2<br>4-3<br>4-4<br>5-1                                           | Title  DR11-W DMA Module M8716 Simplified Block Diagram of DR11-W Used as Interface for UNIBUS and User Device Interface Configurations Control and Status Register (CSR) Error and Information Register (EIR) DR11-W I/O Lines Output Connector J1: Signal Pin Assignments Input Connector J2: Signal Pin Assignments DR11-W Block Diagram Addressing Decoding Logic Interrupt Logic Interrupt Flow Diagram Interface Circuits for Optimizing DR11-W Signal-To-Noise Margin Setting and Clearing FNCT2 and GO Bits                                                                                                                                                                                      | 1-3<br>1-4<br>1-5<br>2-3<br>3-2<br>3-5<br>3-6<br>4-2<br>4-4<br>5-3<br>5-4                                    |

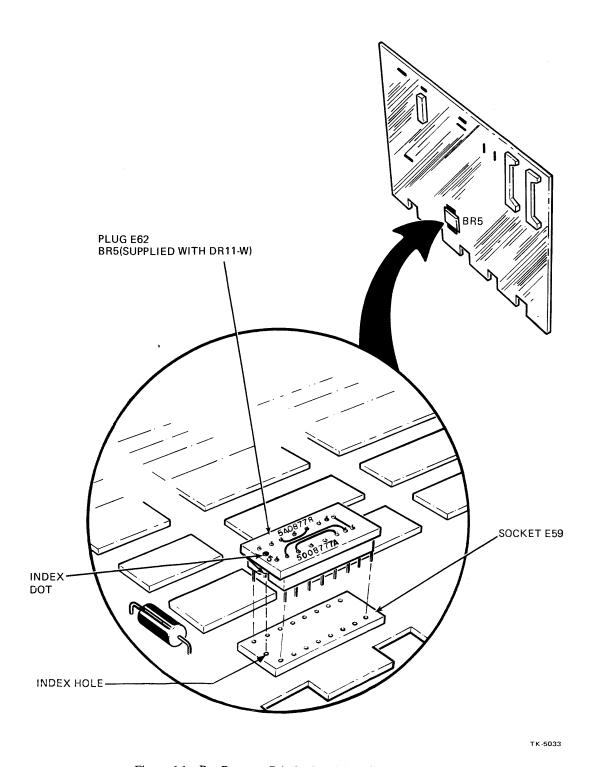

| 1-1<br>1-2<br>1-3<br>2-1<br>2-2<br>3-1<br>3-2<br>3-3<br>4-1<br>4-2<br>4-3<br>4-4<br>5-1<br>5-2<br>6-1                             | Title  DR11-W DMA Module M8716 Simplified Block Diagram of DR11-W Used as Interface for UNIBUS and User Device Interface Configurations Control and Status Register (CSR) Error and Information Register (EIR) DR11-W I/O Lines Output Connector J1: Signal Pin Assignments Input Connector J2: Signal Pin Assignments. DR11-W Block Diagram Addressing Decoding Logic Interrupt Logic Interrupt Flow Diagram Interface Circuits for Optimizing DR11-W Signal-To-Noise Margin Setting and Clearing FNCT2 and GO Bits. Bus-Request, Priority-Level Plug/Socket Assembly                                                                                                                                   | 1-3<br>1-4<br>1-5<br>2-3<br>2-5<br>3-2<br>3-5<br>4-2<br>4-4<br>4-6<br>5-3<br>5-4                             |

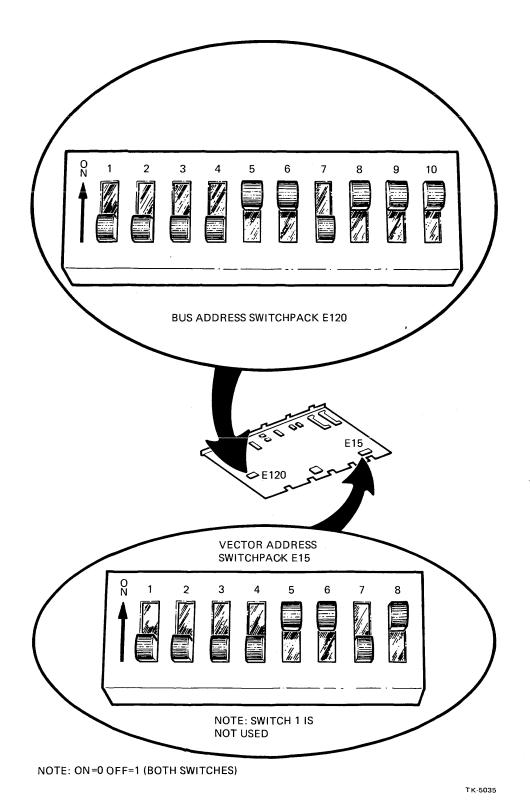

| 1-1<br>1-2<br>1-3<br>2-1<br>2-2<br>3-1<br>3-2<br>3-3<br>4-1<br>4-2<br>4-3<br>4-4<br>5-1<br>5-2<br>6-1<br>6-2                      | Title  DR11-W DMA Module M8716 Simplified Block Diagram of DR11-W Used as Interface for UNIBUS and User Device Interface Configurations Control and Status Register (CSR) Error and Information Register (EIR). DR11-W I/O Lines Output Connector J1: Signal Pin Assignments. Input Connector J2: Signal Pin Assignments. DR11-W Block Diagram Addressing Decoding Logic Interrupt Logic Interrupt Flow Diagram Interface Circuits for Optimizing DR11-W Signal-To-Noise Margin Setting and Clearing FNCT2 and GO Bits. Bus-Request, Priority-Level Plug/Socket Assembly. Bus Address and Vector Address Switchpacks                                                                                     | 1-3<br>1-4<br>1-5<br>2-3<br>2-5<br>3-2<br>3-5<br>3-6<br>4-2<br>4-4<br>4-6<br>5-3<br>5-4<br>6-3               |

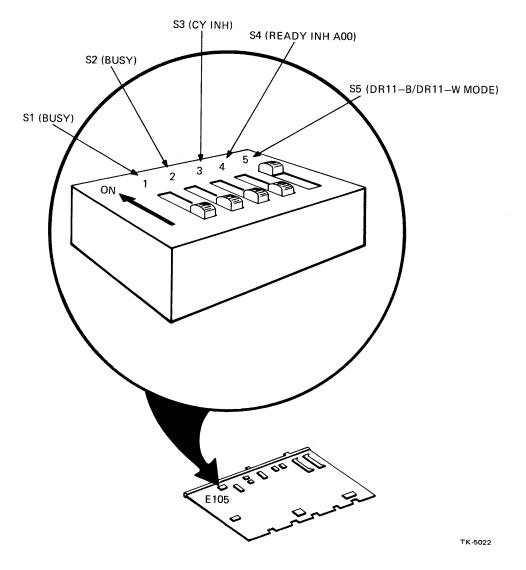

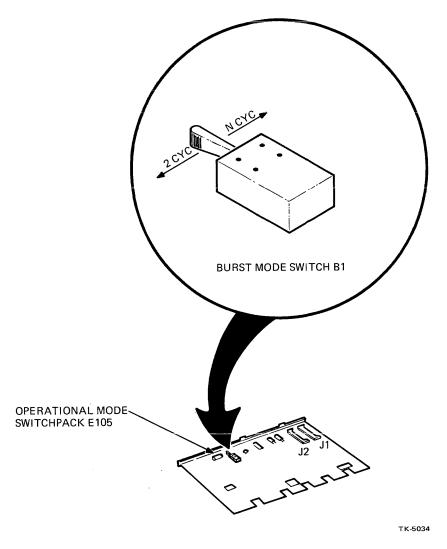

| 1-1<br>1-2<br>1-3<br>2-1<br>2-2<br>3-1<br>3-2<br>3-3<br>4-1<br>4-2<br>4-3<br>4-4<br>5-1<br>5-2<br>6-1<br>6-2<br>6-3               | Title  DR11-W DMA Module M8716 Simplified Block Diagram of DR11-W Used as Interface for UNIBUS and User Device Interface Configurations Control and Status Register (CSR) Error and Information Register (EIR). DR11-W I/O Lines Output Connector J1: Signal Pin Assignments. Input Connector J2: Signal Pin Assignments DR11-W Block Diagram Addressing Decoding Logic Interrupt Logic Interrupt Flow Diagram Interface Circuits for Optimizing DR11-W Signal-To-Noise Margin Setting and Clearing FNCT2 and GO Bits. Bus-Request, Priority-Level Plug/Socket Assembly Bus Address and Vector Address Switchpacks Operational Mode Switchpack E105                                                      | 1-3<br>1-4<br>1-5<br>2-3<br>2-5<br>3-2<br>3-5<br>3-6<br>4-2<br>4-4<br>4-6<br>6-3<br>6-4<br>6-7               |

| 1-1<br>1-2<br>1-3<br>2-1<br>2-2<br>3-1<br>3-2<br>3-3<br>4-1<br>4-2<br>4-3<br>4-4<br>5-1<br>5-2<br>6-1<br>6-2<br>6-3<br>6-4        | Title  DR11-W DMA Module M8716 Simplified Block Diagram of DR11-W Used as Interface for UNIBUS and User Device Interface Configurations Control and Status Register (CSR) Error and Information Register (EIR). DR11-W I/O Lines Output Connector J1: Signal Pin Assignments Input Connector J2: Signal Pin Assignments DR11-W Block Diagram Addressing Decoding Logic Interrupt Logic Interrupt Flow Diagram Interface Circuits for Optimizing DR11-W Signal-To-Noise Margin Setting and Clearing FNCT2 and GO Bits. Bus-Request, Priority-Level Plug/Socket Assembly Bus Address and Vector Address Switchpacks Operational Mode Switchpack E105 Burst Mode Switch B1                                  | 1-3<br>1-4<br>1-5<br>2-3<br>2-5<br>3-2<br>3-5<br>4-4<br>4-6<br>4-8<br>5-3<br>6-4<br>6-7<br>6-8               |

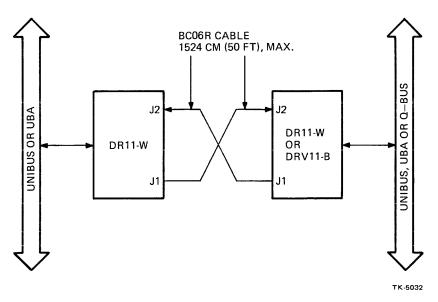

| 1-1<br>1-2<br>1-3<br>2-1<br>2-2<br>3-1<br>3-2<br>3-3<br>4-1<br>4-2<br>4-3<br>4-4<br>5-1<br>5-2<br>6-1<br>6-2<br>6-3<br>6-4<br>7-1 | Title  DR11-W DMA Module M8716 Simplified Block Diagram of DR11-W Used as Interface for UNIBUS and User Device Interface Configurations Control and Status Register (CSR) Error and Information Register (EIR) DR11-W I/O Lines Output Connector J1: Signal Pin Assignments Input Connector J2: Signal Pin Assignments DR11-W Block Diagram Addressing Decoding Logic Interrupt Logic Interrupt Flow Diagram Interface Circuits for Optimizing DR11-W Signal-To-Noise Margin Setting and Clearing FNCT2 and GO Bits Bus-Request, Priority-Level Plug/Socket Assembly Bus Address and Vector Address Switchpacks Operational Mode Switchpack E105 Burst Mode Switch B1 Interprocessor Link Block Diagram. | 1-3<br>1-4<br>1-5<br>2-3<br>3-2<br>3-5<br>3-6<br>4-2<br>4-4<br>4-6<br>4-8<br>5-3<br>6-4<br>6-7<br>6-8<br>7-1 |

| 1-1<br>1-2<br>1-3<br>2-1<br>2-2<br>3-1<br>3-2<br>3-3<br>4-1<br>4-2<br>4-3<br>4-4<br>5-1<br>5-2<br>6-1<br>6-2<br>6-3<br>6-4        | Title  DR11-W DMA Module M8716 Simplified Block Diagram of DR11-W Used as Interface for UNIBUS and User Device Interface Configurations Control and Status Register (CSR) Error and Information Register (EIR). DR11-W I/O Lines Output Connector J1: Signal Pin Assignments Input Connector J2: Signal Pin Assignments DR11-W Block Diagram Addressing Decoding Logic Interrupt Logic Interrupt Flow Diagram Interface Circuits for Optimizing DR11-W Signal-To-Noise Margin Setting and Clearing FNCT2 and GO Bits. Bus-Request, Priority-Level Plug/Socket Assembly Bus Address and Vector Address Switchpacks Operational Mode Switchpack E105 Burst Mode Switch B1                                  | 1-3<br>1-4<br>1-5<br>2-3<br>3-2<br>3-5<br>3-6<br>4-2<br>4-4<br>4-6<br>4-8<br>5-3<br>6-4<br>6-7<br>7-1<br>7-3 |

## **TABLES**

| Table No.   | Title                                           | Page          |

|-------------|-------------------------------------------------|---------------|

| 1-1         | DR11-W Performance Specifications               | . 1-2         |

| 1-2         | Nominal Transfer Rates for Typical Processor    |               |

|             | Configurations                                  | . 1-4         |

| 2-1         | CSR Register - Bit Functions                    | . 2-3         |

| 2-2         | EIR Register - Bit Functions                    | . 2-5         |

| 3-1         | Input Signals from User Device                  | . 3-3         |

| 3-2         | Output Signals to User Device                   |               |

| 6-1         | Available Bus-Request Priority-Level Plugs      | . 6-5         |

| 6-2         | Switch Settings for Bus-Address Switchpack E120 | . 6-5         |

| 6-3         | Switch Settings for Vector Address              |               |

|             | Switchpack E15                                  | 6-6           |

| 6-4         | Switch Settings for Operational Mode            |               |

|             | Switchpack E105                                 | 6-6           |

| 7-1         | Correlation of CSR Function and Status Bits     |               |

|             | in Interprocessor Link Operation                | . 7-2         |

| B-1         | Signal Cross-Reference DR11-B DR11-W            | . B-1         |

| C-1         | DR11-B/DR11-W Functionality Comparison          | . <b>C</b> -1 |

|             | EXAMPLES                                        |               |

| Example No. | Title                                           | Page          |

| 5-1         | Typical VMS Coding Sequence for Loading the CSR |               |

|             | in a DR11-W/VAX System Configuration            | . 5-5         |

| 5-2         | Typical VMS Coding Sequence for Reading the     |               |

|             | DR11-W CSR After Interrupt in the DR11-W/VAX    |               |

|             | System Configuration                            | . 5-6         |

| 5-3         | Typical Coding Sequence for Loading the DR11-W  |               |

|             | CSR in a DR11-W/PDP-11 System Configuration     | . 5-7         |

| 5-4         | Typical Coding Sequence for Reading the CSR     |               |

|             | After Interrupt in the DR11-W/PDP-11 System     |               |

|             | Configuration                                   | 5-8           |

|             |                                                 |               |

### CHAPTER 1 INTRODUCTION

### 1.1 GENERAL

The DR11-W DMA Interface Module M8716 User's Guide provides the following information:

- General Introduction

- Programming Details (Software Interface)

- Description of I/O Signals

- Theory of Operation

- Interface Considerations

- Installation Procedures

- Interprocessor Lines (Link Mode Operation)

- Corrective-Maintenance Diagnostics Listing

### 1.2 SUPPORTING DOCUMENTATION

Two support documents are available for use with this User's Guide:

- 1. Field Maintenance Print Set (MP00693)

- 2. *PDP-11 Bus Handbook* (EB17525-20/79-07-14-55)

### 1.3 FUNCTIONAL DESCRIPTION

The DR11-W is a general-purpose, UNIBUS, direct memory access (DMA) device whose principal performance characteristics are listed in Table 1-1. The DR11-W (Figures 1-1 and 1-2):

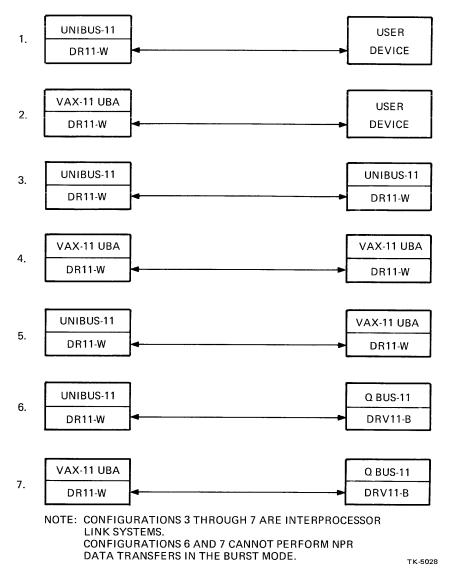

- 1. Provides the means to connect a user device to the UNIBUS of a PDP-11 or VAX computer in either single- or multiple-DR11-W system configurations.

- 2. Provides the means to link a PDP-11 or VAX system with other PDP-11 or VAX systems.

- 3. Can be connected to a DRV11-B to provide a UNIBUS to O-Bus system link.

An unlimited number of DR11-Ws can be used in a system if the addresses and vector selected for each device do not conflict with the addresses and vectors of other devices.

The DR11-W is designed for installation in a single hex small peripheral controller (SPC) slot of a system backplane located within the same enclosure, and is connected to the user device, a DRV11-B, or another DR11-W by not more than 50 feet of cable.

In response to software commands, the DR11-W is capable of crossing 32K boundaries to transfer a maximum block of 64K 16-bit words. Table 1-2 gives nominal transfer rates for typical processor configurations (Figure 1-3.)

Table 1-1 DR11-W Performance Specifications

| Item                                                        | Description                                                                                                  |  |  |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|--|

| Data Transfer:                                              |                                                                                                              |  |  |

| Format                                                      | 16-bit word (parallel transfer)                                                                              |  |  |

| Modes                                                       | Programmed data DMA block (1 cycle, 2 cycles or N cycles per bus grant)                                      |  |  |

| Types                                                       | DATI (Read word) DATIP (Read word with Write to same address to follow) DATO (Write word) DATOB (Write byte) |  |  |

| Addressing capacity                                         | 128K words                                                                                                   |  |  |

| Maximum block size                                          | 64K words (can cross 32K UNIBUS boundaries)                                                                  |  |  |

| Transfer rate                                               | See Table 1-2                                                                                                |  |  |

| User Burst Data Late Timeout                                | Adjustable from 4 to 40 $\mu$ sec to accommodate input data rate (10 to 15 usec is a nominal setting)        |  |  |

| Bus Timeout                                                 | 18 μsec, nominal                                                                                             |  |  |

| Bus Interrupt Priority                                      | Plug selectable for BR4 to BR7 (BR5 is supplied with DR11-W)                                                 |  |  |

| Switchpacks:                                                |                                                                                                              |  |  |

| Operational Mode Selection<br>Bus Address<br>Vector Address | Switchpack E105 - 5 switches Switchpack E120 - 10 switches Switchpack E15 - 8 switches                       |  |  |

| I/O Signal Lines:                                           |                                                                                                              |  |  |

| To User Device<br>From User Device                          | 25<br>28                                                                                                     |  |  |

| Cables:                                                     |                                                                                                              |  |  |

| DR11-W/User Device<br>Interconnect                          | 2 BC06R-XX 40-conductor, 120-ohm, 1524 cm (50 ft), max.                                                      |  |  |

| Maintenance Wraparound                                      | 1 BC05L-1C 40-conductor, 120-ohm 38 cm (15 in.)                                                              |  |  |

| Temperature:                                                |                                                                                                              |  |  |

| Ambient Operating<br>Storage                                | 5 to 50°C (41 to 122°F)<br>-40 to 66°C (-40 to 151°F)                                                        |  |  |

| Humidity                                                    | 10 to 90% noncondensing with max. wet bulb 32°C (90°F) and minimum dew point 2°C (36°F)                      |  |  |

| DC Power                                                    | +5 Vdc @ 3.7 A, nominal                                                                                      |  |  |

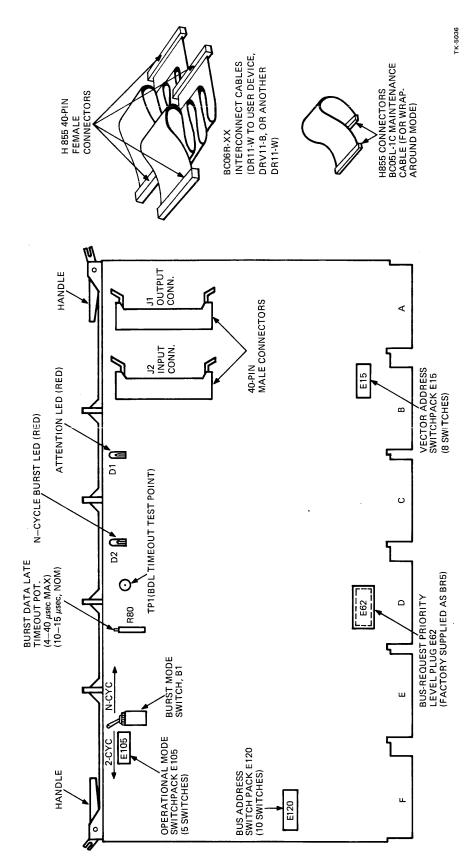

Figure 1-1 DR11-W DMA Module M8716

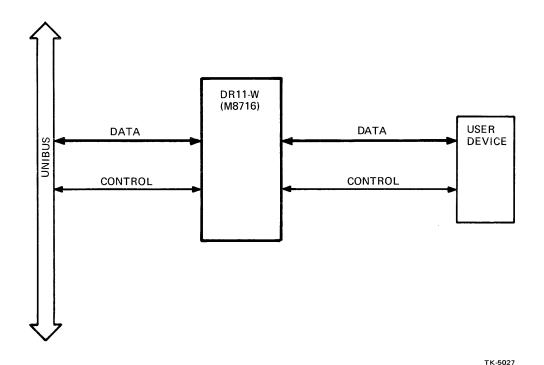

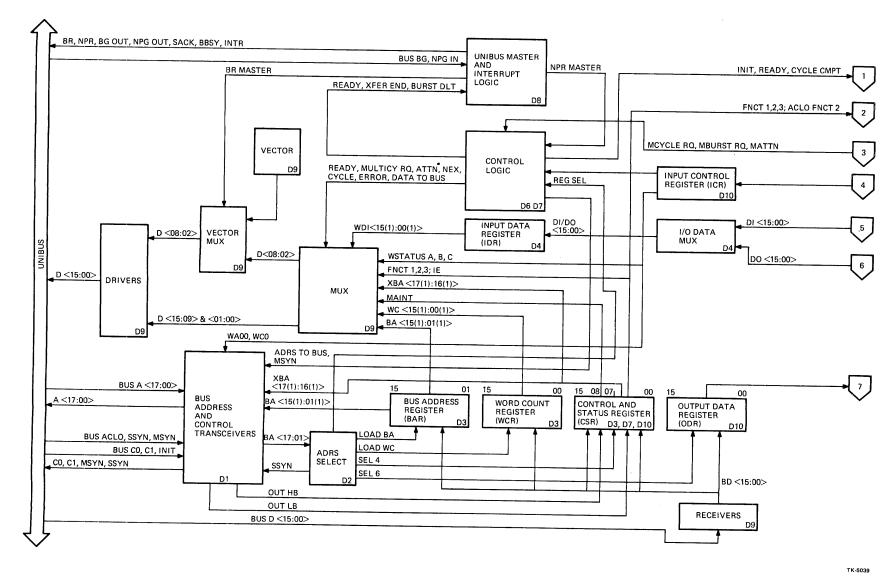

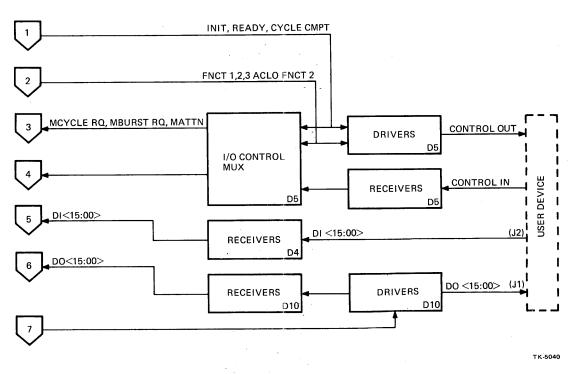

Figure 1-2 Simplified Block Diagram of DR11-W Used as Interface for UNIBUS and User Device

Table 1-2 Nominal Transfer Rates for Typical Processor Configurations

|                    | DR11-W<br>UNIBUS | DR11-W<br>UBA | DRV11-B<br>LSI Bus |  |

|--------------------|------------------|---------------|--------------------|--|

| DR11-W<br>ŲNIBUS   | 500K wps         | 300K wps      | 250K wps           |  |

| DR11-W<br>UBA      | 300K wps         | 400K wps      | 250K wps           |  |

| DRV11-B<br>LSI BUS | 250K wps         | 250K wps      | Not applicable     |  |

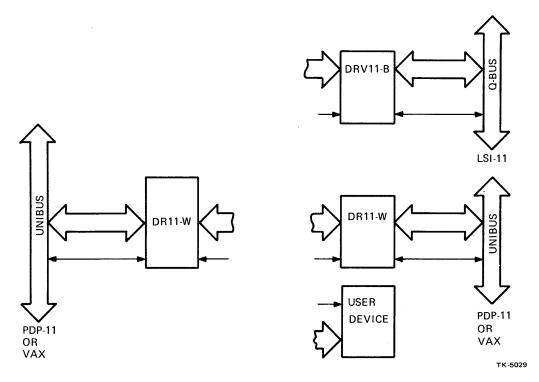

Figure 1-2 is a simplified block diagram showing the DR11-W used in a configuration with a UNIBUS and a user device. Figure 1-3 summarizes the DR11-W's use in more complex arrangements that enable use of a VAX or PDP-11 with another VAX or PDP-11. Figure 1-4 is a simplified functional block diagram for these applications of the DR11-W.

The DR11-W can be operated in either a programmed I/O or DMA mode. In programmed I/O, data is moved to or from the user device under CPU program control. When operated in DMA mode, the DR11-W becomes bus master via an NPR request and operates directly on the memory to satisfy requests originated at the user device.

Figure 1-3 Interface Configurations

A normal DMA operation transfers one word per UNIBUS arbitration. However, DMA operation can be extended to include transfers in either standard or nonstandard burst modes. In the standard burst mode, two words are transferred at the completion of each UNIBUS arbitration in which the DR11-W is granted the bus. In nonstandard burst mode operation, an unlimited number of words can be transferred after receipt of each bus grant.

The DR11-W detects memory parity errors during DATI (read word) and DATIP (read word with intent to write same address) DMA transfers only. Error detection generates an interrupt at the end of the current cycle and terminates the DMA operation. The error is cleared at the start of the next DMA transfer.

For burst mode operation, optimization of DMA latency for each application is individually effected using a screwdriver-adjusted potentiometer on the M8716 board.

DR11-W interruption of the CPU at any one of four priority levels (BR4 – BR7) is possible. A BR plug (normally supplied as BR5 for the DR11-W) provides this interrupt capability.

Figure 1-4 Simplified Block Diagram for DR11-W Used in Typical Configurations

### 1.4 MAINTENANCE MODES

The DR11-W can be tested in either of two maintenance modes:

- 1. Logic wraparound

- 2. Cable wraparound

In logic wraparound testing, UNIBUS data applied to the module is gated back to the UNIBUS for comparison checking. In this mode, all DR11-W components, except the I/O connectors and transceivers, are checked for satisfactory operation.

### **NOTE**

Since random external patterns are generated during this operation, the user device may need to be isolated from the DR11-W until testing is completed.

In cable wraparound testing, a BCO5L test cable (see Paragraph 1.6) is installed between the J2 input connector and the J1 output connector, so that data is looped back to the module. This provision checks the I/O connectors and transceivers of the DR11-W.

### 1.5 COMPATIBILITY OF DR11-B AND DR11-W

The DR11-W has two modes of operation: DR11-B mode and DR11-W mode. Both modes are set by DIP switch 5 (E105 in Figure 1-1). In its DR11-B mode, the DR11-W is both functionally and software compatible with the DR11-B; refer to Appendix C for minor differences between the two interface modules.

The DR11-W mode provides additional error-condition monitoring and enables the interprocessor link capability. Programming the device in DR11-W mode is only slightly different from its programming in the DR11-B mode.

For PDP-11, the DR11-W is supported in both modes by diagnostics for the User-Device and interprocessor-link applications. Like the DR11-B, there is no operating system support for the DR11-W.

For VAX, the DR11-W is supported (in DR11-W mode only) by diagnostics and the VAX/VMS operating system.

### 1.6 PHYSICAL DESCRIPTION

Figure 1-1 shows the relative location of the DR11-W components whose adjustment or indicator status is significant to the user during operational setup and troubleshooting. The DR11-W is configured as a standard hex-height, multilayer, high-density module carrying the designation M8716.

The DR11-W connects to the user device via two BC06R-XX cables. Each end of each cable is terminated by a 40-pin connector; cable impedance is 120 ohms. The BC06R-XX cable is 1524 cm (50 ft) long, the maximum recommended length for this application.

### NOTE

Approved interface cables other than DEC standard BC06R-XX (bare cable DIGITAL P/N 17-00034-00) are Tensolite (P/N) 81-25-00-4000) or an equivalent cable from Spectrastrip, 3m, or Brand Rex.

The DR11-W components whose settings or status indications are of interest to the user during installation, operation, and troubleshooting are (Figure 1-1):

1. Three dual in-line switchpacks:

E15 - vector address (eight switches, but switch 1 not used)

E105 - operational mode (five switches)

E120 - bus address (ten switches)

- 2. Burst mode toggle switch B1 (2 Cycle/N cycle)

- 3. N-cycle burst LED (Red)

- 4. ATTENTION LED (Red)

- 5. E62 priority jumper (normally supplied for BR5 priority)

- 6. Burst data late timeout potentiometer

- 7. Burst data late calibration test point (TP1)

- 8. Six programmable registers:

### Address

| 7XXXX0 | word count register (WCR)                               |

|--------|---------------------------------------------------------|

| 7XXXX2 | bus address register (BAR)                              |

| 7XXXX4 | control and status register (CSR)                       |

| 7XXXX4 | error and information register (EIR) (DR11-W mode only) |

| 7XXXX6 | input data register (IDR)                               |

| 7XXXX6 | output data register (ODR)                              |

The names of the vector address switchpack (E15), and the bus address switchpack (E120), denote their functions. The operational mode switchpack (E105) permits user selection of BUSY, CYCLE IN-HIBIT, READY, and DR11-B/DR11-W mode.

The burst mode toggle switch is set for standard (2-cycle) or nonstandard (N-cycle) mode, as desired. The switch position for each mode is indicated by lettering on the component side of the board adjacent to the switch.

The N-cycle burst LED illuminates whenever the burst mode switch is set to the N-cycle position and an NPR transfer is in progress.

The ATTENTION LED illuminates whenever a user device generates an attention signal, or the DR11-W input cable is disconnected from the DR11-W or the user device.

The burst data late timeout potentiometer is adjustable over the range of 4 to 40 µsec.

### NOTE

For the VAX operating system to handle UBA zero-vector interrupts, timeout should not exceed 20 µsec.

Priority plug E62 enables selection of priority level BR4, 5, 6 or 7. BR5 is the standard plug supplied with the DR11-W module.

### CHAPTER 2 SOFTWARE INTERFACE

### 2.1 GENERAL

The DR11-W uses six programmable registers (see Paragraph 1.5 for their respective addresses). The IDR and ODR, being at the same physical address, are grouped under a single main heading below. For the same reason, the CSR and EIR are grouped under a common main heading. The WCR and BAR, at different addresses, are discussed under separate main headings.

### 2.2 WORD COUNT REGISTER (WCR)

The WCR is the first register on the DR11-W. If the DR11-W is addressed at 772410, the WCR address is also 772410. The WCR can be read or written by the CPU, and is cleared during initialization.

Prior to a data transfer, the WCR is loaded with the two's complement of the total number of words to be transferred. During subsequent transfers, the WCR is incremented by one for each word transferred. Upon transfer of the last word, the WCR overflows and causes the READY flip-flop in the DR11-W control logic to set, an action that tells the user that his transfer is complete. If DR11-W interrupts are enabled, an interrupt occurs at this time.

### 2.3 BUS ADDRESS REGISTER (BAR)

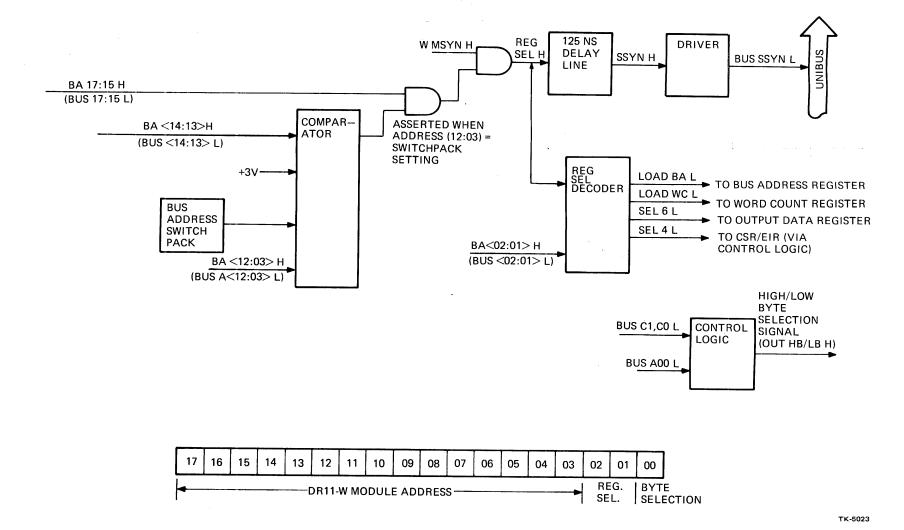

The BAR, like the WCR, is word-addressable only. Continuing our example of the addressing hierarchy (see Paragraph 2.2), if the DR11-W is addressed at 772410, the address of the BAR will be 772412. The BAR can be read or written by the CPU, and is cleared during initialization. This register supplies 15 of the 18 bits used as the UNIBUS address during NPR transfers by the DR11-W. The full 18-bit address, BA(17:00), is derived as follows:

- 1. Bits BA(17:16) are provided by CSR bits 5 (XBA17) and 4 (XBA16), respectively.

- 2. Bits BA(15:01) are provided by BAR bits (15:01), respectively.

- 3. BA(00) is generated by the User Device as A00.

In link operation, the READY output of each DR11-W is coupled to the A00 input of the other DR11-W. To prevent operation at an odd address, switch 4 of the operational mode switchpack E105 is set to ON, thereby grounding the A00 input.

The BAR is normally incremented by two after an NPR data transfer, so that succeeding transfers are made to consecutive words; i.e., the bus address is advanced by two byte-address increments after each transfer. A user device can also select byte transfers by sending the following control signals to the DR11-W: A00 H, C0 CNTL H, and BA INC ENB H.

When the BAR overflows to all 0's, extended bus address bits XBA17 and XBA16 are incremented. This provision enables transfers across 32K word boundaries.

### 2.4 INPUT DATA REGISTER/OUTPUT DATA REGISTER (IDR/ODR)

The input and output data registers share the same address. Continuing our example (in Paragraphs 2.2 and 2.3), if the DR11-W is addressed at 772410, the address of the IDR/ODR is 772416. Writing to this address loads the ODR; reading from this address gives the contents of the IDR. This register is cleared during initialization.

### 2.4.1 Input Data Register (IDR)

During writes to the memory, the IDR buffers data received from the user device. In the programmed I/O mode, the program can obtain this data by reading the IDR. The IDR is read to the bus as DI(15:00).

Upon completion of a data transfer, the CPU can examine the last word transferred by reading the IDR. This can only be done by writing a 1 to bit 15 of the CSR register to set the EIR ENB flip-flop in the control logic. If the IDR is read with EIR ENB cleared, new data will be sampled from the user device and clocked into the IDR. The CPU then reads this new data. Note that EIR functionality is available in the DR11-W mode only (it is inhibited in DR11-B mode to effect compatibility).

During operation in the maintenance-logic wraparound mode, the contents of the ODR are clocked into the IDR at the end of the DATI cycle. This data is therefore available for the subsequent DATO cycle.

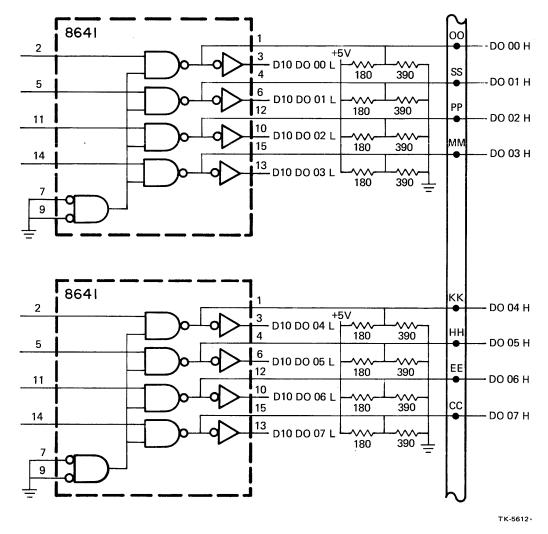

### 2.4.2 Output Data Register (ODR)

The ODR can be written to, but not read. When the CPU writes to the IDR/ODR address, the ODR is loaded. This register is also loaded during NPR transfers whenever the DR11-W reads from memory. The ODR contents are read to a user device as DO(15:00) H. The ODR is cleared during initialization.

# 2.5 CONTROL AND STATUS REGISTER/ERROR AND INFORMATION REGISTER (CSR/EIR)

The CSR and EIR share the same address. Continuing our example (Paragraphs 2.2, 2.3 and 2.4), if the DR11-W is addressed at 772410, the CSR/EIR address is 772414. Writing to this address always writes to the CSR; the EIR is a read-only register. Reading from this address accesses the content of either the CSR or EIR, as described below. Note again that the EIR is enabled in DR11-W mode only.

In writing to bit 15, the following rules apply:

- 1. Writing a 0 results in:

- a. The CSR bits are read

- b. Bit 0 from this address always reads 0

- 2. Writing a 1 results in:

- a. The EIR bits are read

- b. Bit 0 always reads as a 1.

### 2.5.1 Control and Status Register (CSR)

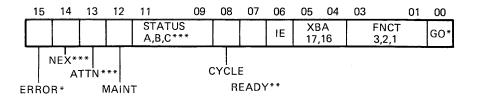

Figure 2-1 shows the bit configuration of the CSR; the name and function of each bit is given in Table 2-1.

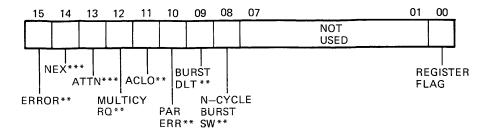

### 2.5.2 Error and Information Register (EIR)

Figure 2-2 shows the bit configuration of the EIR; the name and function of each bit is given in Table 2-2.

### NOTES:

- 1. BITS WITH NO ASTERISK ARE READ/WRITE

- 2. BITS WITH A SINGLE ASTERISK CAN BE WRITTEN AS "1" BUT ARE ALWAYS READ AS ZERO ("0")

- 3. BITS WITH A DOUBLE ASTERISK ARE READ ONLY

- 4. BITS WITH A TRIPLE ASTERISK ARE READ/CLEAR.

TK-5030

Figure 2-1 Control and Status Register (CSR)

Table 2-1 CSR Register: Bit Functions

| Bit   | Name                       | Function                                                                                                                                                                                                                                                                                                                                                           |

|-------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00    | GO                         | This bit is written under program control and is always read to the bus as zero. Setting this bit causes the DR11-W to begin its transfer.                                                                                                                                                                                                                         |

| (3:1) | FNCT 3<br>FNCT 2<br>FNCT 1 | These function bits are user-defined, and specify the operation the user intends to perform. They are read/write, and cleared during initialization.                                                                                                                                                                                                               |

| (5:4) | XBA17<br>XBA16             | These bits generate extended BUS A(17:16) for NPR transfers, and are incremented when the bus address register overflows. They are read/write, and cleared during initialization.                                                                                                                                                                                  |

| 6     | IE                         | The interrupt enable (IE) bit, when set, allows an interrupt to occur if:                                                                                                                                                                                                                                                                                          |

|       |                            | • A GO pulse is generated after an error has been detected.                                                                                                                                                                                                                                                                                                        |

|       |                            | • The word count register overflows at the end of a transfer.                                                                                                                                                                                                                                                                                                      |

|       |                            | <ul> <li>An error condition signal is detected (i.e, ERROR, NEX, ATTN, ACLO, MULTICY<br/>RQ, or PAR ERROR) during an NPR transfer.</li> </ul>                                                                                                                                                                                                                      |

|       |                            | • A user device error signal (ATTN) is sent to the DR11-W.                                                                                                                                                                                                                                                                                                         |

|       |                            | IE is a read/write bit and is cleared during initialization.                                                                                                                                                                                                                                                                                                       |

| 7     | READY                      | READY is a read/write bit. When set, it indicates that the DR11-W has completed the previous operation and is ready to accept a new command. The ERROR bit must be checked to determine whether or not the transfer was successful. Any error condition must be cleared before a new command can be executed. READY is cleared by setting GO or by initialization. |

Table 2-1 CSR Register: Bit Functions (Cont)