EK-DMR11-TM-002

# DMR11 synchronous controller technical manual

digital equipment corporation • merrimack, new hampshire

1st Edition, May 1980 2nd Printing, September 1980 2nd Edition, January 1981

Copyright <sup>©</sup> 1980, 1981 by Digital Equipment Corporation

•

1

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DIGITAL | DECsystem-10 | MASSBUS      |

|---------|--------------|--------------|

| DEC     | DECSYSTEM-20 | OMNIBUS      |

| PDP     | DIBOL        | <b>OS</b> /8 |

| DECUS   | EDUSYSTEM    | RSTS         |

| UNIBUS  | VAX          | RSX          |

| UNIDOS  | VMS          | IAS          |

## CONTENTS

#### PREFACE

#### CHAPTER 1 INTRODUCTION

| 1.1   | SCOPE                                       | <b>1-</b> 1 |

|-------|---------------------------------------------|-------------|

| 1.2   | DMR11 GENERAL DESCRIPTION                   |             |

| 1.3   | DMR11 SYSTEM OPERATION                      |             |

| 1.3.1 | Command Structure                           |             |

| 1.3.2 | Input Commands                              |             |

| 1.3.3 | Output Commands                             | 1-4         |

| 1.3.4 | DMR11 Operation Sequencing                  |             |

| 1.3.5 | Maintenance Mode Operation                  | 1-5         |

| 1.4   | GENERAL SPECIFICATIONS                      |             |

| 1.4.1 | Power Requirements                          | 1-5         |

| 1.4.2 | Environmental Requirements - A11 DMR11s     |             |

| 1.5   | EIA STANDARDS OVERVIEW (RS-449 vs RS-232-C) | 1-7         |

## CHAPTER 2 INSTALLATION

| 2.1     | SCOPE                                |      |

|---------|--------------------------------------|------|

| 2.2     | UNPACKING AND INSPECTION             |      |

| 2.3     | INSTALLATION CONSIDERATIONS          | 2-1  |

| 2.4     | PREINSTALLATION CONSIDERATIONS       | 2-1  |

| 2.4.1   | System and Device Placement          | 2-2  |

| 2.4.1.1 | System Placement                     | 2-2  |

| 2.4.1.2 | Device Placement                     | 2-3  |

| 2.4.2   | System Requirements                  | 2-3  |

| 2.5     | MICROPROCESSOR INSTALLATION          |      |

| 2.5.1   | Backplane Considerations             |      |

| 2.5.2   | M8207-RA Considerations              |      |

| 2.5.3   | M8207-RA Insertion                   | 2-6  |

| 2.6     | LINE UNIT INSTALLATION               | 2-7  |

| 2.6.1   | M8203 Considerations                 |      |

| 2.6.2   | M8203 Insertion                      |      |

| 2.7     | DMR11 SYSTEM TESTING                 | 2-28 |

| 2.7.1   | Functional Diagnostic Testing        |      |

| 2.7.2   | DECX11 System Exerciser              |      |

| 2.7.3   | Final Cable Connections              | 2-32 |

| 2.7.4   | DMR11 Link Testing                   | 2-32 |

| 2.8     | DMR11-XX INSTALLATION CHECK-OFF LIST | 2-37 |

## CHAPTER 3 PROGRAMMING

| 3.1   | INTRODUCTION                 | 3-1 |

|-------|------------------------------|-----|

| 3.2   | COMMAND STRUCTURE            |     |

| 3.2.1 | Control and Status Registers |     |

| 3.2.2 | Initialization               |     |

| 5.2.2 | Initialization               |     |

## **CONTENTS (CONT)**

| 3.2.3     | Input Commands Overview                               | 3-6   |

|-----------|-------------------------------------------------------|-------|

| 3.2.3.1   | Input Command Handshaking                             |       |

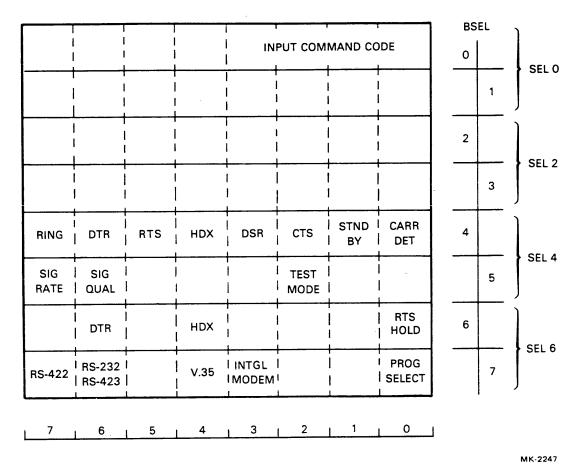

| 3.2.3.2   | Modem Status Read                                     |       |

| 3.2.4     | Output Commands Overview                              | 3_13  |

| 3.2.4.1   | Output Command Handshaking                            |       |

| 3.3       | INPUT COMMANDS                                        | 3_14  |

| 3.3.1     | Base In                                               |       |

| 3.3.2     | Control In                                            |       |

|           |                                                       |       |

| 3.3.3     | Receive Buffer Address/Character Count In (RBA/CCI)   |       |

| 3.3.4     | Transmit Buffer Address/Character Count In (TBA/CCI)  |       |

| 3.3.5     | Halt Request Command                                  |       |

| 3.4       | OUTPUT COMMANDS                                       |       |

| 3.4.1     | Receive Buffer Address/Character Count Out (RBA, CCO) |       |

| 3.4.2     | Transmit Buffer Address/Character Count Out (TBA/CCO) |       |

| 3.4.3     | Control Out                                           |       |

| 3.5       | PROGRAMMING TECHNIQUES                                |       |

| 3.5.1     | Input Command Sequence                                |       |

| 3.5.2     | Base In Command with Resume Feature                   |       |

| 3.5.3     | Distinguishing DMR11 from DMC11                       |       |

| 3.5.4     | DDC P Maintenance Mode Operation                      |       |

| 3.5.4.1   | Data Transfer                                         |       |

| 3.5.4.2   | Unattended System Control                             | 3-30  |

| 3.6       | BASE TABLE COUNTERS                                   |       |

| 3.7       | MODEM CONTROL                                         |       |

| 3.7.1     | Modem Control Implemented in M8203                    | 3-34  |

| 3.7.1.1   | Modem Ready Lockout of RTS                            | 3-34  |

| 3.7.1.2   | Half-Duplex Mode                                      | 3-34  |

| 3.7.2     | Modem Control Implemented in DMR11 Microprogram       | 3-34  |

| 3.7.2.1   | Auto-Answer                                           | 3-34  |

| 3.7.2.2   | Data Set Ready Glitch                                 | 3-35  |

| 3.7.2.3   | RTS – CTS Delay                                       |       |

| 3.7.2.4   | Loss of Carrier Detect                                |       |

| 3.7.2.5   | Receiver Inactive Check                               |       |

| 3.7.2.6   | Modem Status Read During Input Command                |       |

| 3.7.2.7   | Data Terminal Ready Control                           |       |

| 3.8       | DMR11 DATA LINK FUNCTIONS                             |       |

| CHAPTER 4 | SERVICE                                               |       |

| CHAFTER 4 | SERVICE                                               |       |

| 4.1       | SCOPE                                                 | 4-1   |

| 4.2       | MAINTENANCE PHILOSOPHY                                |       |

| 4.3       | MAINTENANCE FUNCTIONS/MAINTENANCE MODES               | 4-1   |

| 4.3.1     | Maintenance Register (BSEL1)                          | 4-1   |

| 4.3.2     | Maintenance Modes.                                    | 4-1   |

| 4.3.2.1   | Maintenance Modes                                     | 4-2   |

| 4.3.2.2   | System Test                                           | 4-2   |

| 4.3.2.3   | Single Step Internal Maintenance Mode                 | 4-2   |

| 4.3.2.4   | System Test Internal Maintenance Mode                 | 4_2   |

| 4.3.2.5   | External Maintenance Mode                             | 4.7   |

| 7.3.4.3   |                                                       | ····· |

# CONTENTS (CONT)

## APPENDIX D MICROCODE OVERVIEW

•

|       | INTRODUCTION                      | D-1 |

|-------|-----------------------------------|-----|

| D.1   | INTRODUCTION                      |     |

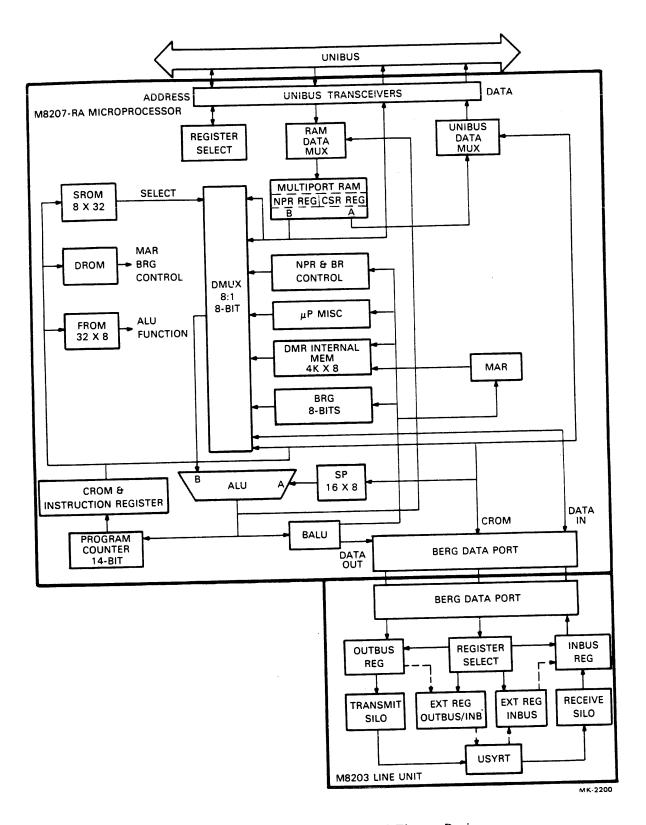

| D.2   | FUNCTIONAL HARDWARE               |     |

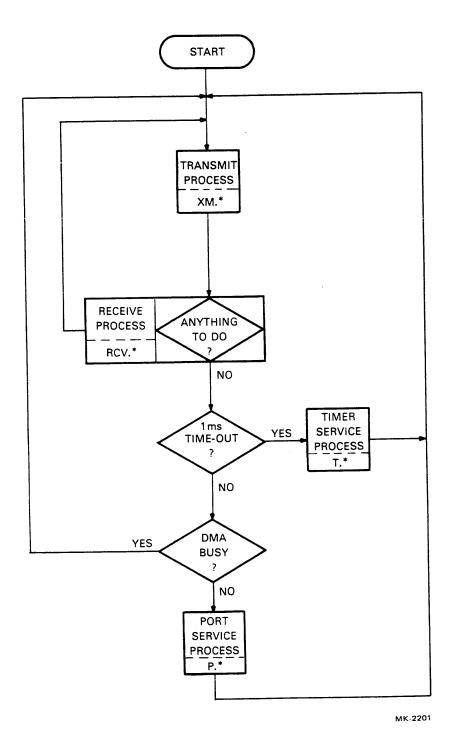

| D.3   | DMR11 MICROPROGRAM                | D-1 |

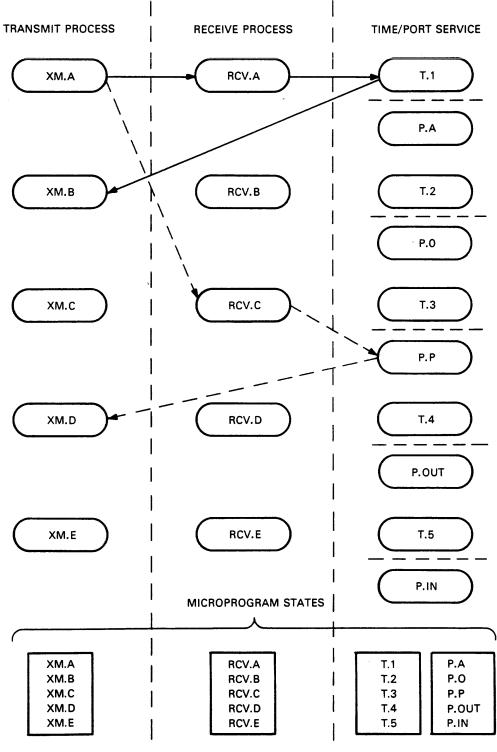

|       | Microprogram Message Processing   |     |

| D.3.1 | Whet optogram wessage in beessing | D 4 |

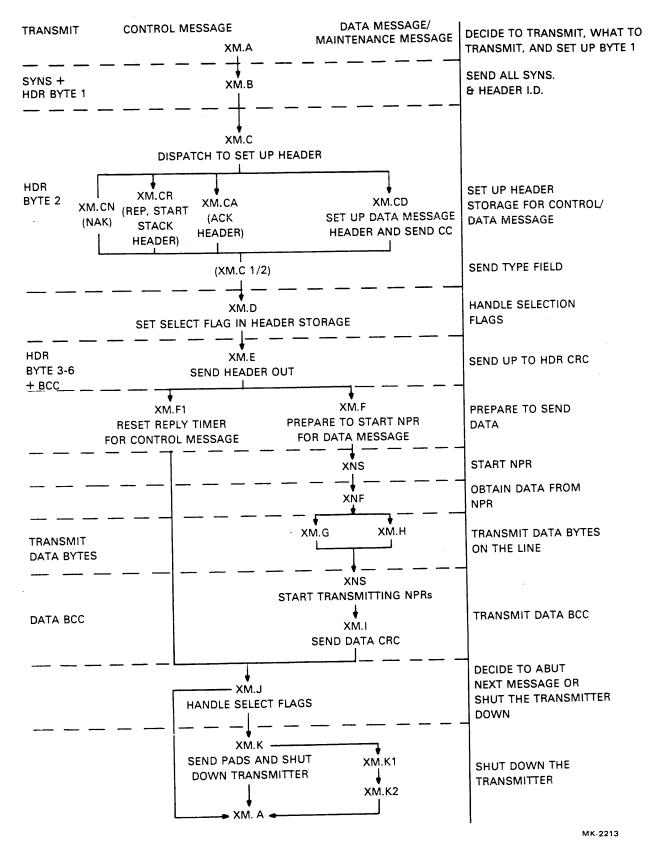

| D.3.2 | Transmit Process                  |     |

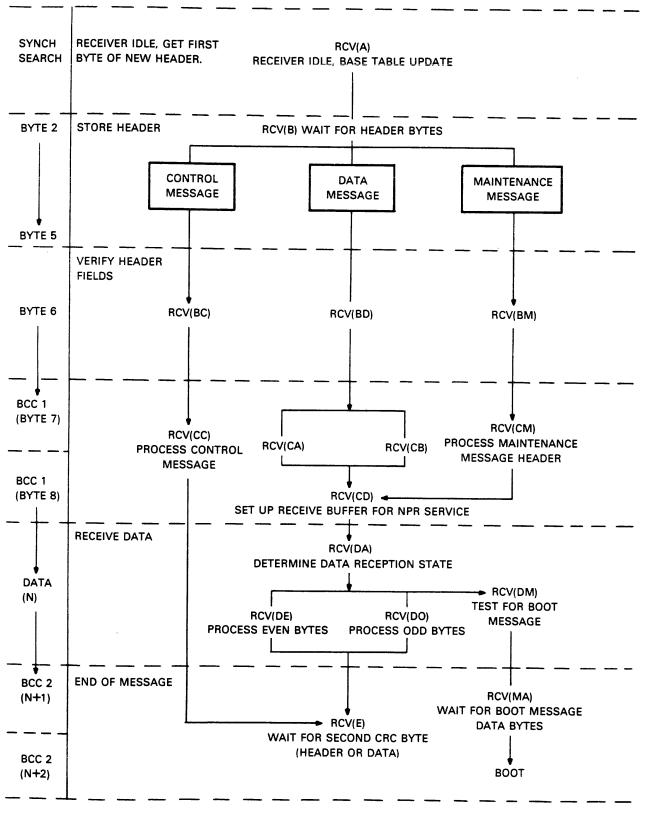

| D.3.3 | Receive Process                   | D-4 |

| 0.0.0 |                                   |     |

# APPENDIX E BOOTSTRAP TEST UNDER ITEP

| F 1   | REMOTE LOAD DETECT                              | E-1         |

|-------|-------------------------------------------------|-------------|

| E.1   | REMOTE LOAD DETECT                              | F_1         |

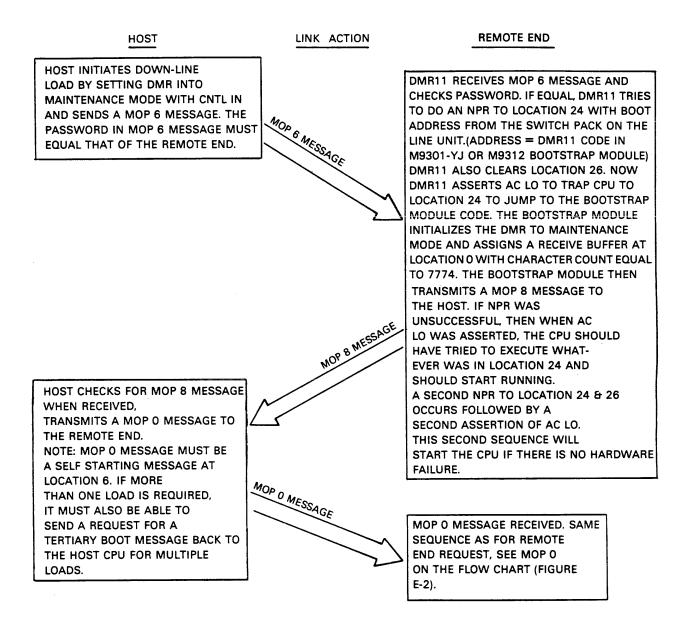

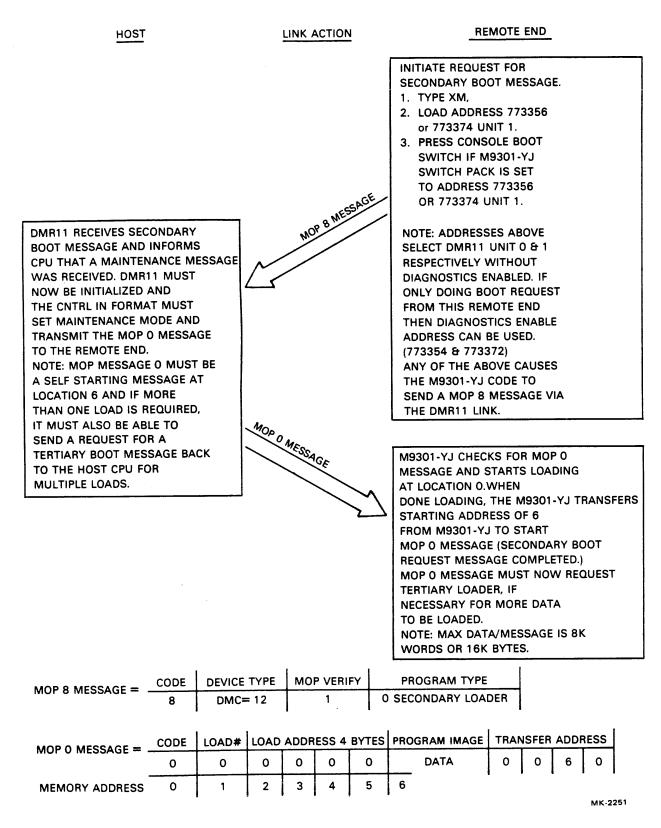

| E.2   | DMR11 SETUP FOR REMOTE LOAD DETECT              | L-1<br>E 1  |

| E.2.1 | DMR11 Addressing                                | E-I         |

| E.2.2 | DMR11 Line Unit Setun                           | <b>C-</b> I |

| E.3   | PROCEDURE TO TEST REMOTE LOAD DETECT UNDER ITEP | E-2         |

| E.4   | PROCEDURE TO TEST DOWN-LINE LOAD UNDER ITEP     | E-4         |

#### GLOSSARY

## FIGURES

## Figure No.

#### Title

## Page

|     | Typical PDP-11 Applications                               |      |

|-----|-----------------------------------------------------------|------|

| 1-1 | Typical PDP-11 Applications                               | 1-3  |

| 1-2 | Typical VAX-11/780 Applications                           | 1-6  |

| 1-3 | DMR11 Operation Sequencing                                | 2_5  |

| 2-1 | M8207-PA Microprocessor Switch / Jumper Locations         |      |

| 2-2 | M8203 Switch / Jumper Locations                           |      |

| 2-3 | Microprocessor / Line Unit Installation                   |      |

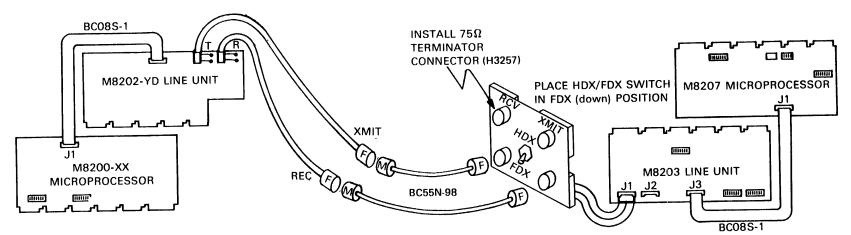

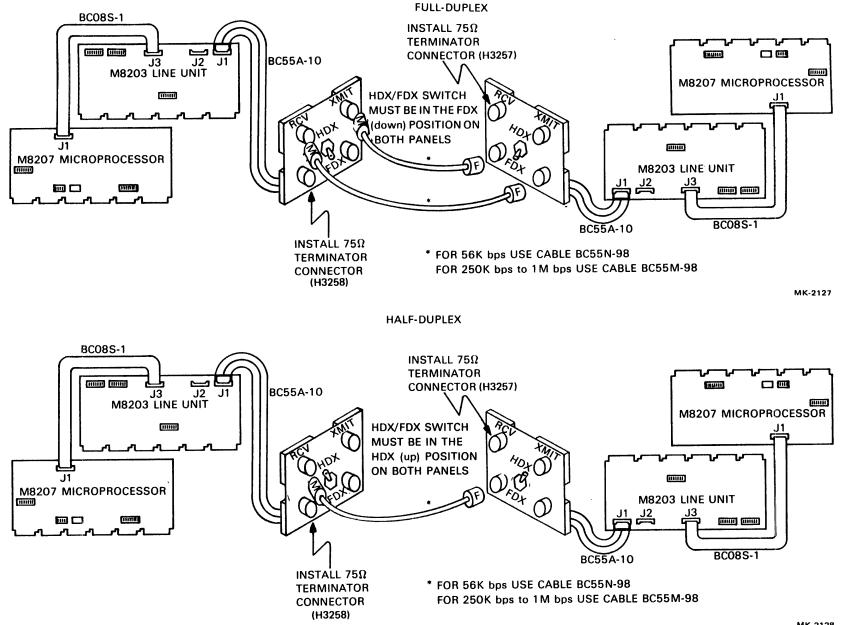

| 2-4 | DMP11 Cable Drawings                                      |      |

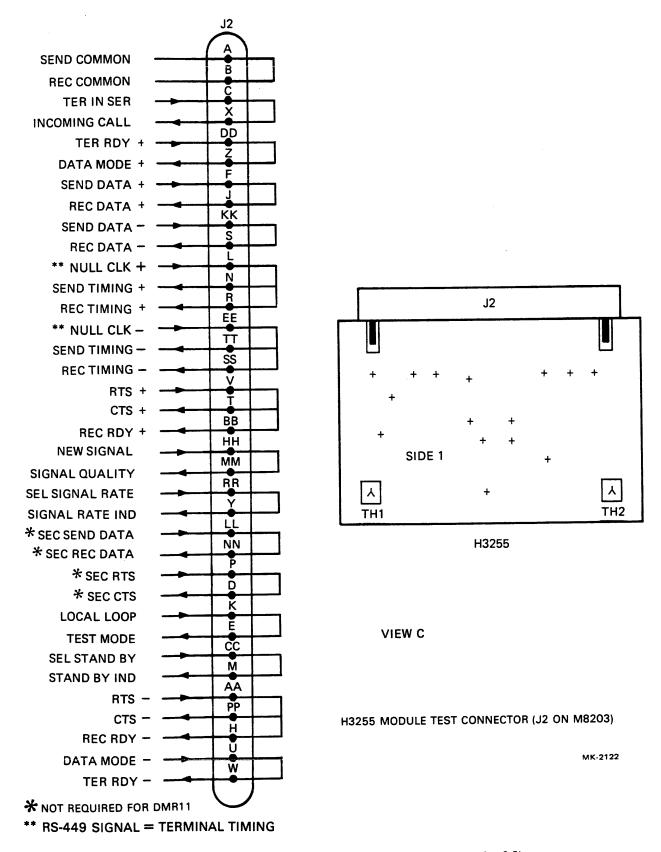

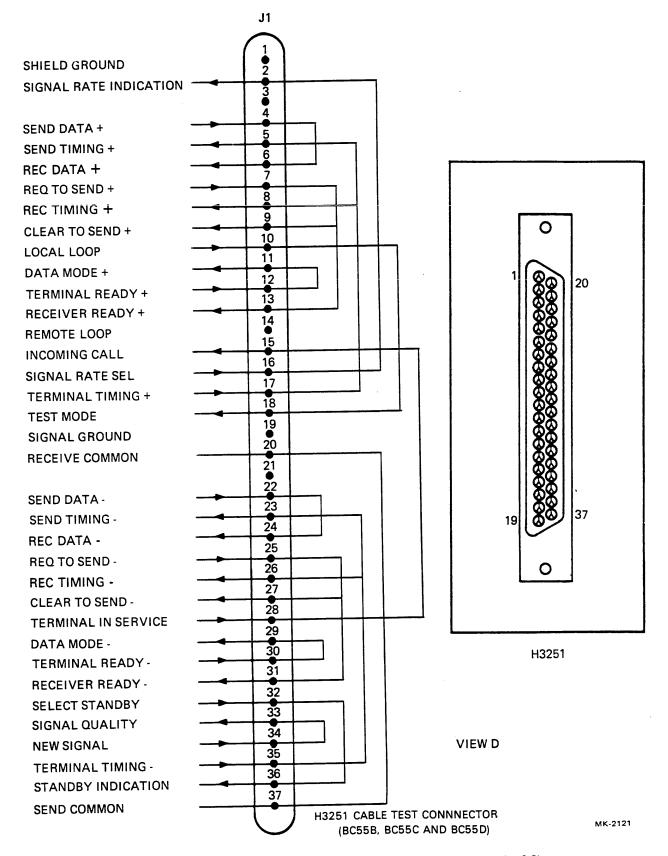

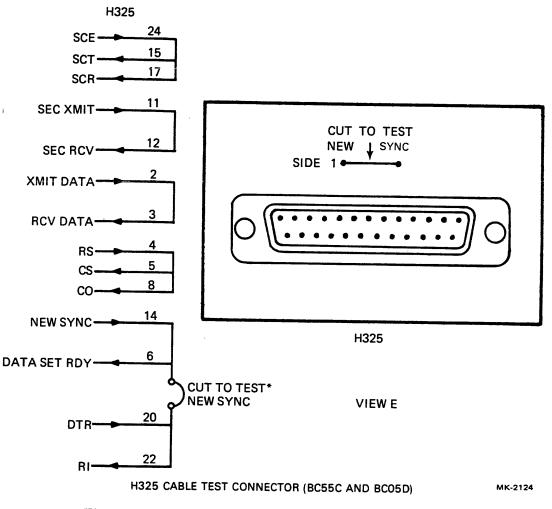

| 2-5 | DMR11 Turnaround Test Connectors                          |      |

| 2-6 | DMP11 Remote System Cabling Diagram                       |      |

| 2-0 | DMC11 to DMR11 Integral (Local) Modem Cabling Diagram     |      |

| 2-7 | DMD11 to DMD11 Integral (Local) Modem Cabling Diagram     |      |

|     | LINIDUS Control and Status Registers Format Overview      | J-+  |

| 3-1 | Programming Example for Input Commands                    | 3-9  |

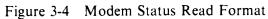

| 3-2 | Input Command Servicing                                   |      |

| 3-3 | Input Command Servicing                                   | 3-11 |

| 3-4 | Modem Status Read Format                                  | 3_14 |

| 3-5 | Summary of Control Out Status                             |      |

| 3-6 | Summary of Control Out Status<br>Output Command Servicing |      |

| 3-7 | Rase In Command Format                                    |      |

| 3-8 | Control In Command Format                                 |      |

| 3-9 | Start/Stack Sequence Timer                                | 3-19 |

# **CONTENTS** (CONT)

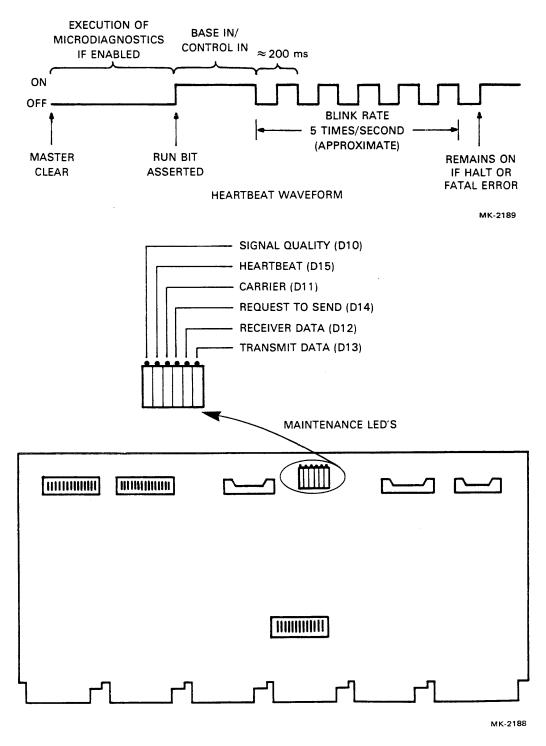

| 4.3.3                                                                                             | Maintenance (LED) Indicators                                                                                                                                                                                                                                                                                                                                                          |                                                                                                       |

|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| 4,4                                                                                               | PREVENTIVE MAINTENANCE (PM)                                                                                                                                                                                                                                                                                                                                                           |                                                                                                       |

| 4.5                                                                                               | CORRECTIVE MAINTENANCE ON A PDP-11 PROCESSOR                                                                                                                                                                                                                                                                                                                                          |                                                                                                       |

| 4.5.1                                                                                             | CZDMP*/CZDMQ*                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                       |

| 4.5.2                                                                                             | CZDMR*/CZDMS*                                                                                                                                                                                                                                                                                                                                                                         | 4-8                                                                                                   |

| 4.5.3                                                                                             | CZDMI*                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                       |

| 4.5.4                                                                                             | DMR11 Microdiagnostic Error Reporting                                                                                                                                                                                                                                                                                                                                                 |                                                                                                       |

| 4.5.5                                                                                             | ZDMO <sup>**</sup> – DMC11/DMR11 Overlay for Interprocessor                                                                                                                                                                                                                                                                                                                           |                                                                                                       |

| 1.2.2                                                                                             | Test Program (ITEP)                                                                                                                                                                                                                                                                                                                                                                   | 4-12                                                                                                  |

| 4.5.6                                                                                             | DEC/X11 DMC11 Module                                                                                                                                                                                                                                                                                                                                                                  | 4-13                                                                                                  |

| 4.5.7                                                                                             | Soft Error Reports Under DEC/X11                                                                                                                                                                                                                                                                                                                                                      | 4-16                                                                                                  |

| 4.5.8                                                                                             | Examination of DMR11 Internal Components                                                                                                                                                                                                                                                                                                                                              | 4-16                                                                                                  |

| 4.6                                                                                               | CORRECTIVE MAINTENANCE ON A VAX-11/780                                                                                                                                                                                                                                                                                                                                                | 4-18                                                                                                  |

| 4.6.1                                                                                             | EVDXA COMM Microprocessor Repair Level                                                                                                                                                                                                                                                                                                                                                |                                                                                                       |

| 4.0.1                                                                                             | Diagnostics                                                                                                                                                                                                                                                                                                                                                                           | 4-19                                                                                                  |

| 4.6.2                                                                                             | Diagnostics<br>EVDMA Repair Level Diagnostics                                                                                                                                                                                                                                                                                                                                         | 4-23                                                                                                  |

| 4.6.3                                                                                             | EVDCA REV *.* VAX-11/780 Synchronous Link Level Two                                                                                                                                                                                                                                                                                                                                   |                                                                                                       |

| 4.0.5                                                                                             | Diagnostics                                                                                                                                                                                                                                                                                                                                                                           | 4-24                                                                                                  |

| 4.6.4                                                                                             | Examination of DMR11 Internal Components                                                                                                                                                                                                                                                                                                                                              | 4_24                                                                                                  |

| 4.0.4                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                       |

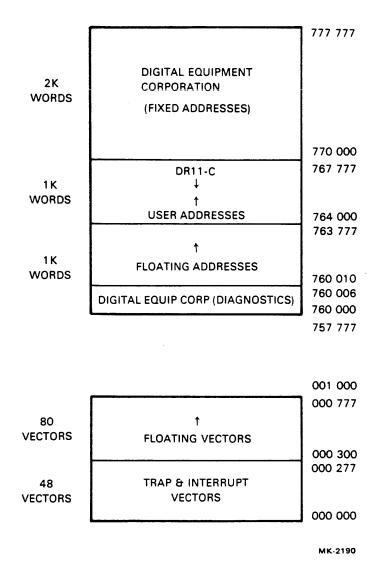

| APPENDIX A                                                                                        | FLOATING DEVICE ADDRESSES AND VECTORS                                                                                                                                                                                                                                                                                                                                                 |                                                                                                       |

| A.1                                                                                               | FLOATING DEVICE ADDRESSES                                                                                                                                                                                                                                                                                                                                                             | Δ_1                                                                                                   |

| A.2                                                                                               | FLOATING VECTOR ADDRESSES                                                                                                                                                                                                                                                                                                                                                             |                                                                                                       |

| A.3                                                                                               | EXAMPLES OF DEVICE AND VECTOR ADDRESS ASSIGNMENT                                                                                                                                                                                                                                                                                                                                      |                                                                                                       |

| 2 8                                                                                               | ERAMILES OF DEVICE AND VECTOR ADDRESS ASSIGNMENT                                                                                                                                                                                                                                                                                                                                      |                                                                                                       |

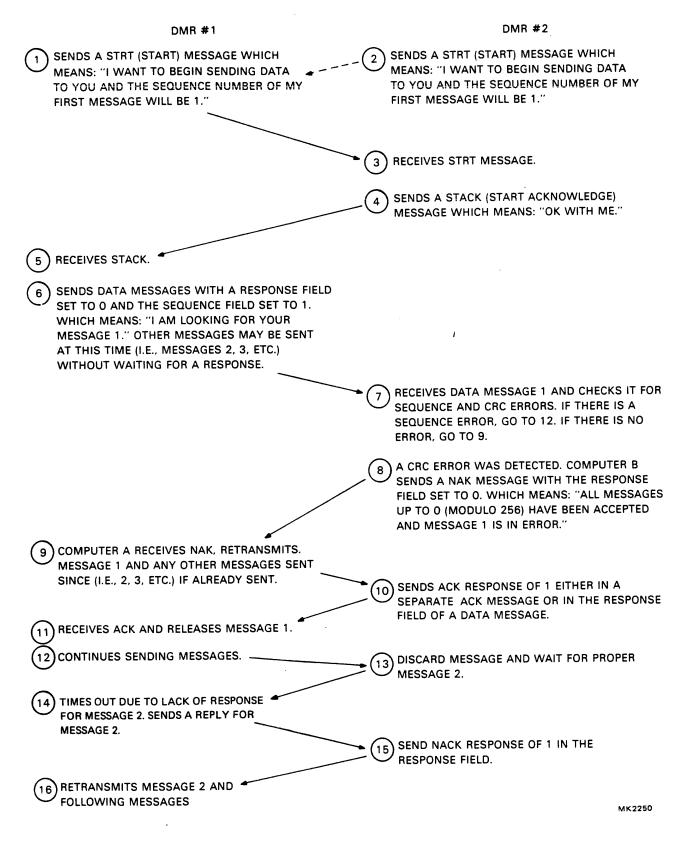

| APPENDIX B                                                                                        | DDCMP IN A NUTSHELL                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                       |

| <b>B</b> .1                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                       |

|                                                                                                   | DDCMP                                                                                                                                                                                                                                                                                                                                                                                 | B-1                                                                                                   |

| B.1.1                                                                                             | DDCMP<br>Controlling Data Transfers                                                                                                                                                                                                                                                                                                                                                   | B-1<br>B-1                                                                                            |

| B.1.1<br>B.1.2                                                                                    | Controlling Data Transfers                                                                                                                                                                                                                                                                                                                                                            | B-1                                                                                                   |

| B.1.2                                                                                             | Controlling Data Transfers<br>Error Checking and Recovery                                                                                                                                                                                                                                                                                                                             | B-1<br>B-1                                                                                            |

| B.1.2<br>B.1.3                                                                                    | Controlling Data Transfers<br>Error Checking and Recovery<br>Character Coding                                                                                                                                                                                                                                                                                                         | B-1<br>B-1<br>B-3                                                                                     |

| B.1.2<br>B.1.3<br>B.1.4                                                                           | Controlling Data Transfers<br>Error Checking and Recovery<br>Character Coding<br>Data Transparency                                                                                                                                                                                                                                                                                    | B-1<br>B-1<br>B-3<br>B-3<br>B-3                                                                       |

| B.1.2<br>B.1.3<br>B.1.4<br>B.1.5                                                                  | Controlling Data Transfers<br>Error Checking and Recovery<br>Character Coding<br>Data Transparency<br>Data Channel Utilization                                                                                                                                                                                                                                                        | B-1<br>B-1<br>B-3<br>B-3<br>B-3<br>B-3                                                                |

| B.1.2<br>B.1.3<br>B.1.4                                                                           | Controlling Data Transfers<br>Error Checking and Recovery<br>Character Coding<br>Data Transparency                                                                                                                                                                                                                                                                                    | B-1<br>B-3<br>B-3<br>B-3<br>B-3<br>B-3<br>B-3                                                         |

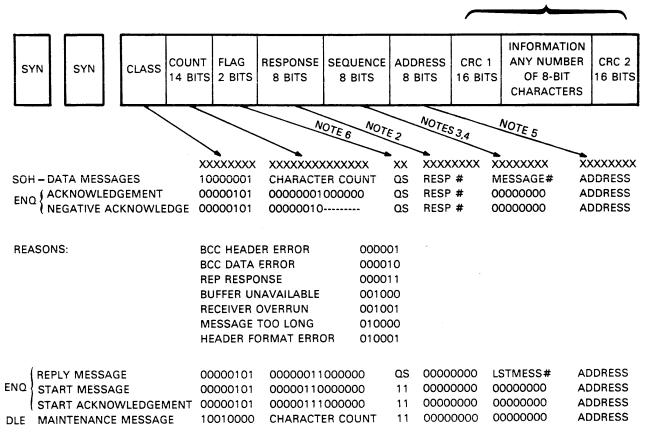

| B.1.2<br>B.1.3<br>B.1.4<br>B.1.5<br>B.2<br>B.3                                                    | Controlling Data Transfers<br>Error Checking and Recovery<br>Character Coding<br>Data Transparency<br>Data Channel Utilization<br>PROTOCOL DESCRIPTION<br>MESSAGE FORMAT                                                                                                                                                                                                              | B-1<br>B-3<br>B-3<br>B-3<br>B-3<br>B-3<br>B-3                                                         |

| B.1.2<br>B.1.3<br>B.1.4<br>B.1.5<br>B.2                                                           | Controlling Data Transfers<br>Error Checking and Recovery<br>Character Coding<br>Data Transparency<br>Data Channel Utilization<br>PROTOCOL DESCRIPTION                                                                                                                                                                                                                                | B-1<br>B-3<br>B-3<br>B-3<br>B-3<br>B-3<br>B-3                                                         |

| B.1.2<br>B.1.3<br>B.1.4<br>B.1.5<br>B.2<br>B.3<br>APPENDIX C                                      | Controlling Data Transfers<br>Error Checking and Recovery<br>Character Coding<br>Data Transparency<br>Data Channel Utilization<br>PROTOCOL DESCRIPTION<br>MESSAGE FORMAT<br>DIAGNOSTIC SUPERVISOR SUMMARY                                                                                                                                                                             | B-1<br>B-3<br>B-3<br>B-3<br>B-3<br>B-3<br>B-3<br>B-3<br>B-6                                           |

| B.1.2<br>B.1.3<br>B.1.4<br>B.1.5<br>B.2<br>B.3                                                    | Controlling Data Transfers<br>Error Checking and Recovery<br>Character Coding<br>Data Transparency<br>Data Channel Utilization<br>PROTOCOL DESCRIPTION<br>MESSAGE FORMAT                                                                                                                                                                                                              | B-1<br>B-3<br>B-3<br>B-3<br>B-3<br>B-3<br>B-3<br>B-6                                                  |

| B.1.2<br>B.1.3<br>B.1.4<br>B.1.5<br>B.2<br>B.3<br>APPENDIX C<br>C.1                               | Controlling Data Transfers<br>Error Checking and Recovery<br>Character Coding<br>Data Transparency<br>Data Channel Utilization<br>PROTOCOL DESCRIPTION.<br>MESSAGE FORMAT<br>DIAGNOSTIC SUPERVISOR SUMMARY<br>INTRODUCTION                                                                                                                                                            | B-1<br>B-3<br>B-3<br>B-3<br>B-3<br>B-3<br>B-3<br>B-6<br>C-1<br>C-1                                    |

| B.1.2<br>B.1.3<br>B.1.4<br>B.1.5<br>B.2<br>B.3<br>APPENDIX C<br>C.1<br>C.2                        | Controlling Data Transfers<br>Error Checking and Recovery<br>Character Coding<br>Data Transparency<br>Data Channel Utilization<br>PROTOCOL DESCRIPTION<br>MESSAGE FORMAT<br>DIAGNOSTIC SUPERVISOR SUMMARY<br>INTRODUCTION<br>VERSIONS OF THE DIAGNOSTIC SUPERVISOR<br>LOADING AND RUNNING A SUPERVISOR DIAGNOSTIC                                                                     | B-1<br>B-3<br>B-3<br>B-3<br>B-3<br>B-3<br>B-3<br>B-6<br>C-1<br>C-1<br>C-1                             |

| B.1.2<br>B.1.3<br>B.1.4<br>B.1.5<br>B.2<br>B.3<br>APPENDIX C<br>C.1<br>C.2<br>C.3                 | Controlling Data Transfers<br>Error Checking and Recovery<br>Character Coding<br>Data Transparency<br>Data Channel Utilization<br>PROTOCOL DESCRIPTION<br>MESSAGE FORMAT<br>DIAGNOSTIC SUPERVISOR SUMMARY<br>INTRODUCTION<br>VERSIONS OF THE DIAGNOSTIC SUPERVISOR<br>LOADING AND RUNNING A SUPERVISOR DIAGNOSTIC<br>Five Steps to Run a Supervisor Diagnostic                        | B-1<br>B-3<br>B-3<br>B-3<br>B-3<br>B-3<br>B-3<br>B-6<br>C-1<br>C-1<br>C-1<br>C-1<br>C-2               |

| B.1.2<br>B.1.3<br>B.1.4<br>B.1.5<br>B.2<br>B.3<br>APPENDIX C<br>C.1<br>C.2<br>C.3<br>C.3.1        | Controlling Data Transfers<br>Error Checking and Recovery<br>Character Coding<br>Data Transparency<br>Data Channel Utilization<br>PROTOCOL DESCRIPTION<br>MESSAGE FORMAT<br>DIAGNOSTIC SUPERVISOR SUMMARY<br>INTRODUCTION<br>VERSIONS OF THE DIAGNOSTIC SUPERVISOR<br>LOADING AND RUNNING A SUPERVISOR DIAGNOSTIC<br>Five Steps to Run a Supervisor Diagnostic<br>SUPERVISOR COMMANDS | B-1<br>B-3<br>B-3<br>B-3<br>B-3<br>B-3<br>B-3<br>B-6<br>C-1<br>C-1<br>C-1<br>C-1<br>C-2<br>C-3        |

| B.1.2<br>B.1.3<br>B.1.4<br>B.1.5<br>B.2<br>B.3<br>APPENDIX C<br>C.1<br>C.2<br>C.3<br>C.3.1<br>C.4 | Controlling Data Transfers<br>Error Checking and Recovery<br>Character Coding<br>Data Transparency<br>Data Channel Utilization<br>PROTOCOL DESCRIPTION<br>MESSAGE FORMAT<br>DIAGNOSTIC SUPERVISOR SUMMARY<br>INTRODUCTION<br>VERSIONS OF THE DIAGNOSTIC SUPERVISOR<br>LOADING AND RUNNING A SUPERVISOR DIAGNOSTIC<br>Five Steps to Run a Supervisor Diagnostic                        | B-1<br>B-3<br>B-3<br>B-3<br>B-3<br>B-3<br>B-3<br>B-6<br>C-1<br>C-1<br>C-1<br>C-1<br>C-2<br>C-3<br>C-4 |

# FIGURES (CONT)

| Figure No. | Title                                                       | Page        |

|------------|-------------------------------------------------------------|-------------|

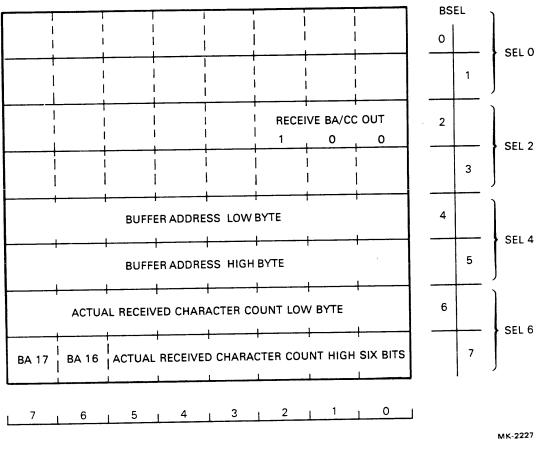

| 3-10       | Receive Buffer Address/Character Count In Command Format    | 3-20        |

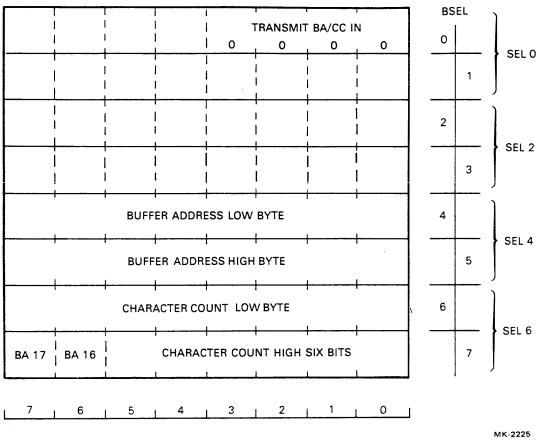

| 3-11       | Transmit Buffer Address/Character Count In Command Format   | 3-21        |

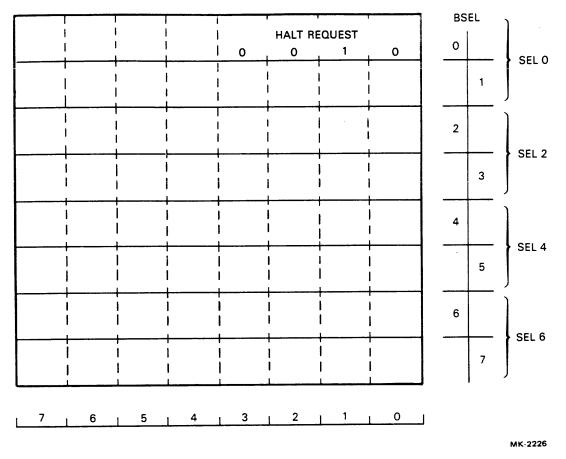

| 3-12       | Halt Request Command Format                                 | 3-22        |

| 3-13       | Receive Buffer Address/Character Count Out Command Format   | 3-23        |

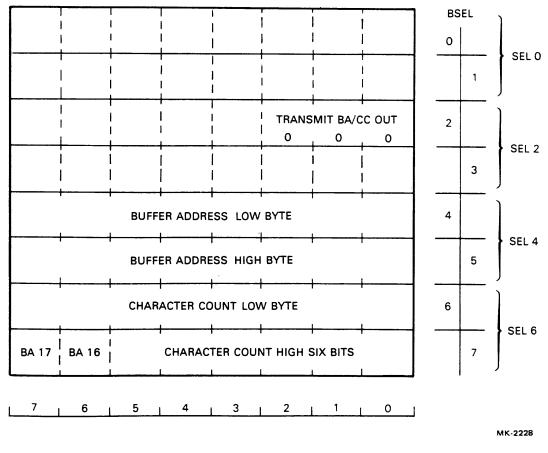

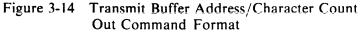

| 3-14       | Transmit Buffer Address/Character Count Out Command Format  | 3-24        |

| 3-15       | Control Out Command Format                                  | 3-25        |

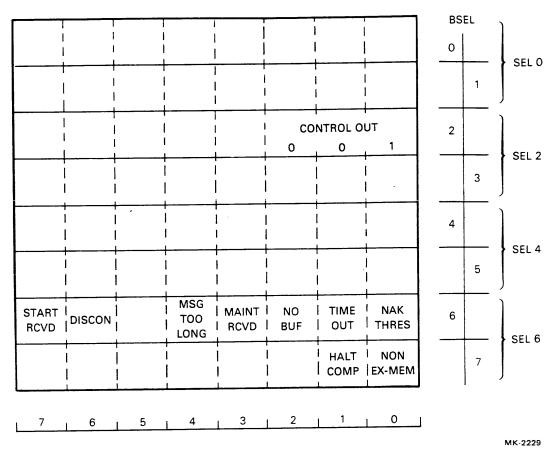

| 3-16       | DMR11 Protocol State Diagram                                | 3-28        |

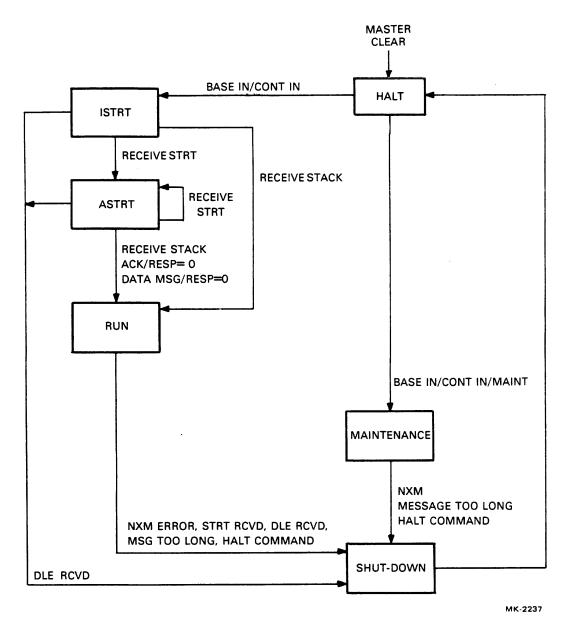

| 3-17       | Down-Line Load Procedure to Remote Station                  | 3-32        |

| 3-18       | DMR11 Base Table Error Counters                             | 3-33        |

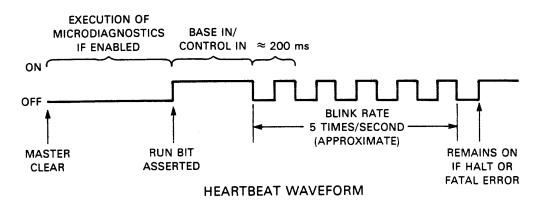

| 4-1        | M8203 Maintenance LED Locations/Heartbeat Waveform          | 4-7         |

| 4-2        | DMR11 Base Table Lavout                                     | 4-20        |

| A-1        | UNIBUS Address Map                                          | A-2         |

| B-1        | DDCMP Data Message Format                                   | B-1         |

| B-2        | DDCMP Sample Handshaking Procedure                          | B-2         |

| B-3        | DDCMP Message Format in Detail                              | B-5         |

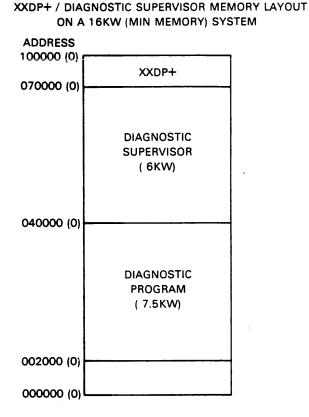

| C-1        | XXDP+/Diagnostic Supervisor Memory Layout on a (Min Memory) |             |

|            | 16K w System                                                | C-2         |

| D-1        | Data and Control Flow - Basic                               | D-2         |

| D-2        | Executive Flow Diagram                                      | D-5         |

| D-3        | Typical DMR11 Message Processing                            | D-0         |

| D-4        | Transmit Process Flow Diagram                               | <b>D</b> -7 |

| D-5        | Receive Process Flow Diagram                                | D-8         |

| E-1        | Down-Line Load to Remote End Using Remote Load Detect       | E-5         |

| E-2        | Remote End Request for Down-Line Load                       | E-6         |

## TABLES

#### Title

Table No.

Page

| 1-1        | DMR11 Options                                       |                                        |

|------------|-----------------------------------------------------|----------------------------------------|

|            | DMR11 Performance Parameters                        | 1-7                                    |

| 1-2        | DMR11 Performance Parameters                        | ······································ |

| .2-1       | DMR11 Option Packing List                           |                                        |

| 2-2        | DMR11 Voltage Chart                                 |                                        |

| 2-3        | M8207-RA DMR11 lumper Chart                         |                                        |

| 2-4        | Switch Pack E127 Selections                         |                                        |

| 2-4        | Switch Pack E28 Selections                          | 2-9                                    |

| 2-6        | Switch Selectable Features                          |                                        |

| 2-0<br>2-7 | Normal M8203 Configuration (Bootstrap Not Selected) |                                        |

|            | M8203 Jumper Functions                              | 2-12                                   |

| 2-8        | M8205 Jumper Functions.                             | 2 1 2                                  |

| 2-9        | Switch Pack E39 (Z) Selections                      |                                        |

| 2-10       | Switch Pack E121 (Y) Selections                     |                                        |

| 2-10       | Switch Pack E134 (X) Selections                     |                                        |

|            |                                                     | 2_18                                   |

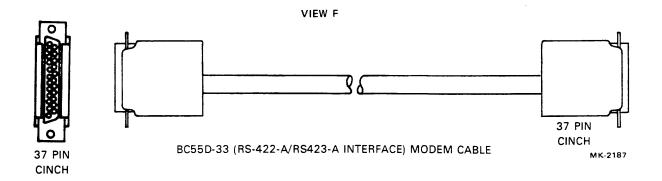

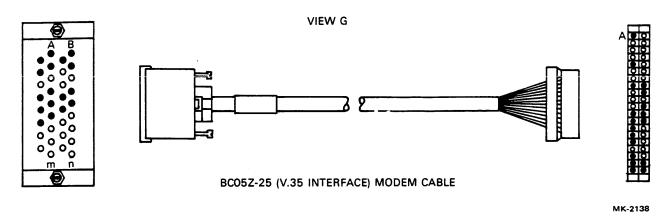

| 2-12       | Cable Description                                   | 2-10                                   |

|            |                                                     |                                        |

# TABLES (CONT)

## Title

Table No.

## Page

| 2-13 | Modem Option Jumper Functions                     |      |

|------|---------------------------------------------------|------|

| 3-1  | SEL 0 Bit Functions                               |      |

| 3-2  | BSEL 2 Bit Functions                              | 3-5  |

| 3-3  | Input Commands                                    |      |

| 3-4  | Modem Status Bit Descriptions                     |      |

| 3-5  | Data Port Descriptions with Control In            |      |

| 3-6  | Data Port Bit Descriptions with Control Out       | 3-26 |

| 3-7  | DMR11 Command Sequence                            |      |

| 3-8  | Invalid Enter MOP Message Response                |      |

| 4-1  | BSEL 1 Bit Descriptions<br>Maintenance Indicators |      |

| 4-2  | Maintenance Indicators                            |      |

| 4-3  | CZDMP* Diagnostic Summary                         |      |

| 4-4  | DZDMQ* Diagnostic Summary                         |      |

| 4-5  | CZDMR* Diagnostic Summary                         |      |

| 4-6  | CZDMS* Diagnostic Summary                         |      |

| 4-7  | CZDMI* Diagostic Summary                          |      |

| 4-8  | DDCMP Message Decode for DMR11**                  |      |

| D-1  | Major Functional Areas                            | D-3  |

## PREFACE

This manual describes in detail the installation requirements, programming considerations, and servicing procedures, including diagnostic support, for the DMR11 Synchronous Controller. A variety of appendices are also provided to supplement the above.

Other publications which support the DMR11 Synchronous Controller are:

- M8207 Microprocessor Technical Manual (EK-M8207-TM-001)

- M8203 Line Unit Technical Manual (EK-M8203-TM-001)

- DMR11 Print Set (MP-00911)

- Electronic Industries Association (EIA) Specifications

•

## CHAPTER 1 INTRODUCTION

#### 1.1 SCOPE

This chapter contains a brief introduction to DMR11 operation. The term DMR11, as used throughout this manual, denotes the communication subsystem which consists of a microprocessor module and a line unit module.

#### **1.2 DMR11 GENERAL DESCRIPTION**

The DMR11 is designed to be used in a network link for high performance interconnection of VAX-11/780 or PDP-11 computers. It is a microprocessor-based, intelligent synchronous communications controller which employs the DIGITAL Data Communications Message Protocol (DDCMP). The DMR11 is program compatible with DMC11 and line compatible with either DMC11 or any device that uses DDCMP version 4.0.

Features of the DMR11 include:

- Extensive error reporting,

- Down-line and remote load detect to attended or unattended PDP-11 processors (requires bootstrap option),

- Modem control,

- Auto-answering capabilities,

- DMC11 program compatibility.

- Switch selection of DMC11 line compatibility mode or DDCMP V4.0 compatibility mode,

- Comprehensive diagnostic tests,

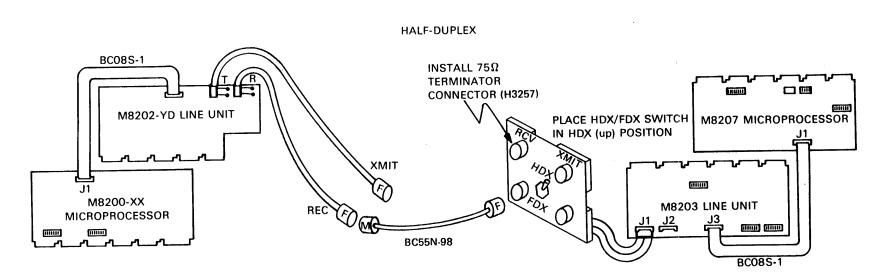

- Support for local or remote, full-duplex or half-duplex configurations,

- 16-bit non-processor request (NPR), direct memory access (DMA) transfers, and

- DDCMP implementation which handles message sequencing and error correction by automatic retransmission.

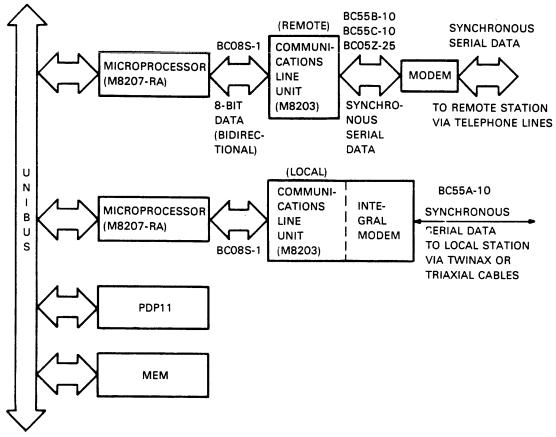

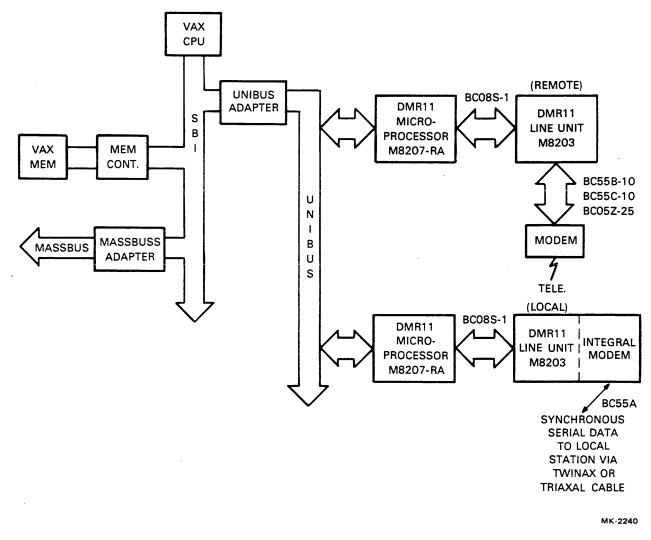

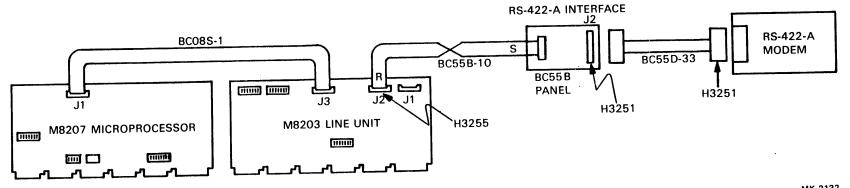

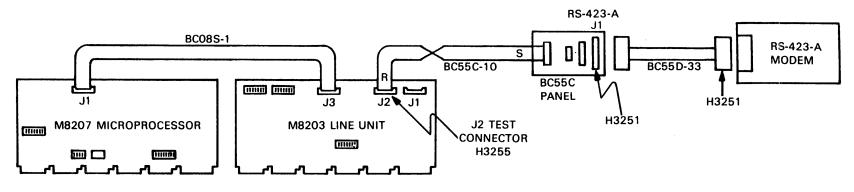

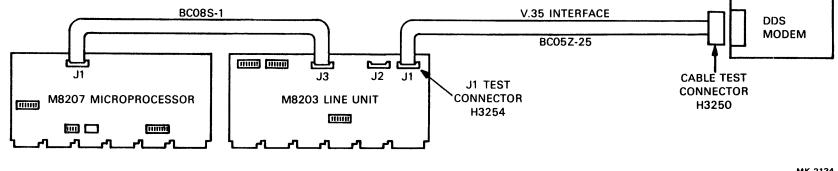

The DMR11 basic unit consists of the M8207-RA microprocessor and the M8203 line unit. The microprocessor serves as a parallel data interface between the central processor (VAX-11/780 or PDP-11) and the M8203 line unit. This line unit/microprocessor combination permits either remote or local computer applications. (For remote operations, computers are connected through external modems that use common carrier facilities.) See Figure 1-1 for PDP-11 applications and Figure 1-2 for VAX-11/780 applications.

MK-2241

Figure 1-1 Typical PDP-11 Applications

The DMR11 system consists of a basic subsystem and four options which allow it to accommodate standard and special interface configurations. With these options, DMR11 systems can operate with speeds ranging from 2.4K bits per second (b/s) to 1M b/s (see Table 1-1).

| Option   | Interface                                    | Line Speed                        |

|----------|----------------------------------------------|-----------------------------------|

| DMR11-AA | EIA RS-232-C*<br>EIA RS-423-A/<br>CCITT V.10 | Up to 19.2K b/s<br>Up to 56K b/s‡ |

| DMR11-AB | ISO 2593/CCITT V.35†                         | Up to 1M b/s                      |

| DMR11-AC | Integral Modem                               | 56K, 250K, 500K, 1M b/s           |

| DMR11-AE | EIA RS-422-A/<br>CCITT V.11                  | Up to 1M b/s                      |

| Table | 1-1 | DMR11 | Ontions |

|-------|-----|-------|---------|

| LADIC | 1-1 |       |         |

\*EIA – Electronic Industries Association

†ISO – International Standards Organization

CCITT – Comite Consultatif Internationale de Telegraphic et Telephone ‡ Limited to 20K b/s by RS-449 and 9600 b/s by ISO 4902

Figure 1-2 Typical VAX-11/780 Applications

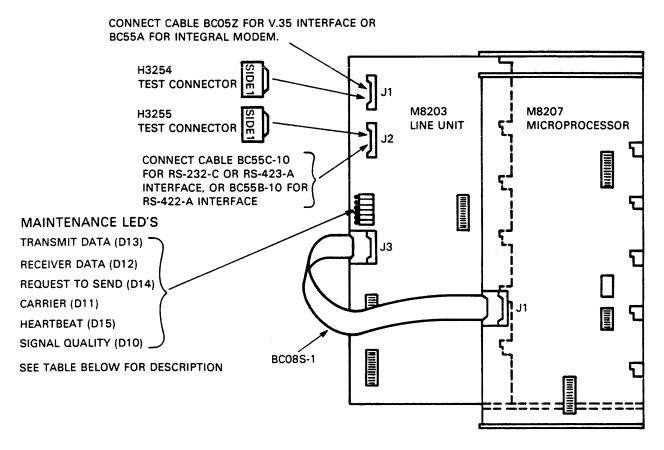

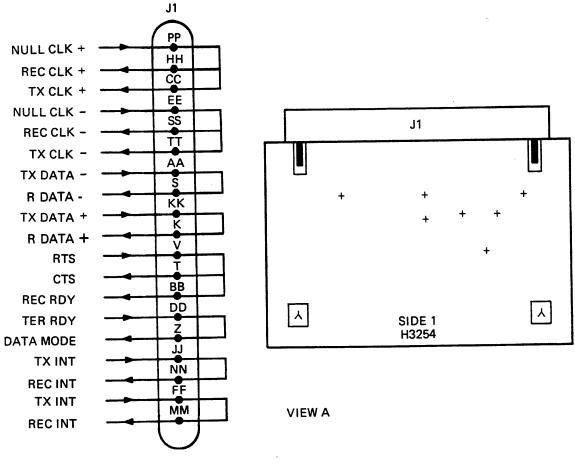

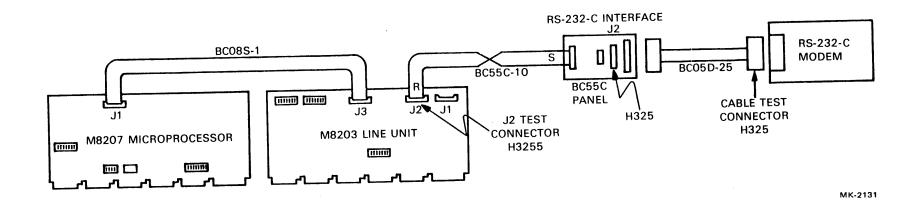

The basic subsystem is designated DMR11-AD and consists of an M8203 line unit, an M8207-RA microprocessor, a BC08S-1 interconnect cable, an H3254 interface module test connector, and an H3255 interface module test connector. The M8203 line unit has an Integral Modem which is switch selectable to operate at speeds of 56K, 250K, 500K, and 1M b/s.

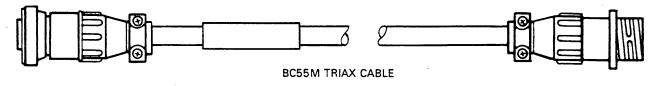

For local operations through Integral Modems, systems are interconnected by twinax or triaxial cables in either half-duplex (one cable) or full-duplex (two cables) configurations. The DMR11-AC option is used for local operations. A maximum distance of 6 km (18K feet) at 56K b/s can be obtained using recommended cables. For information on recommended cables, data rates/distance, and fabrication techniques for twinax/triaxial cables, refer to the *M8203 Line Unit Technical Manual*, EK-M8203-TM-001, Appendix B. For specific information on the installation of the DMR11 basic subsystem and its options, refer to Chapter 2.

#### 1.3 DMR11 SYSTEM OPERATION

Operation of the DMR11 is initiated and directed by a user program residing in the central processing unit's (CPU) memory. A user program consists of an application program and a device driver routine

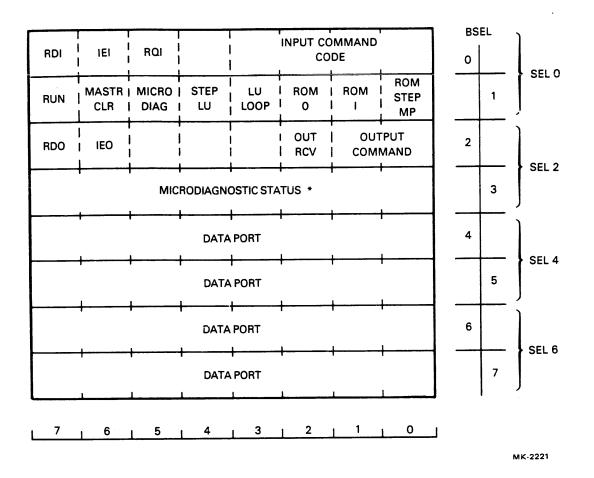

that interfaces with the DMR11. Communication between the user program and the DMR11 is accomplished by four 16-bit control and status registers (CSR) integrated to the microprocessor. These CSRs are used for initializing, selecting the mode of operation, assigning receive or transmit buffers to the DMR11, obtaining receive and transmit buffer returns from the DMR11, and error reporting.

The first two registers in the group have a fixed format and serve as a command header for the second two registers. The second two registers form a two-word data port for the exchange of unique control/status information between the DMR11 and the user program. Data port contents are specified by an identification field in the command header. Other fields in this header control interrupt enabling and status bits for command transfer handshakes between the main CPU and the DMR11.

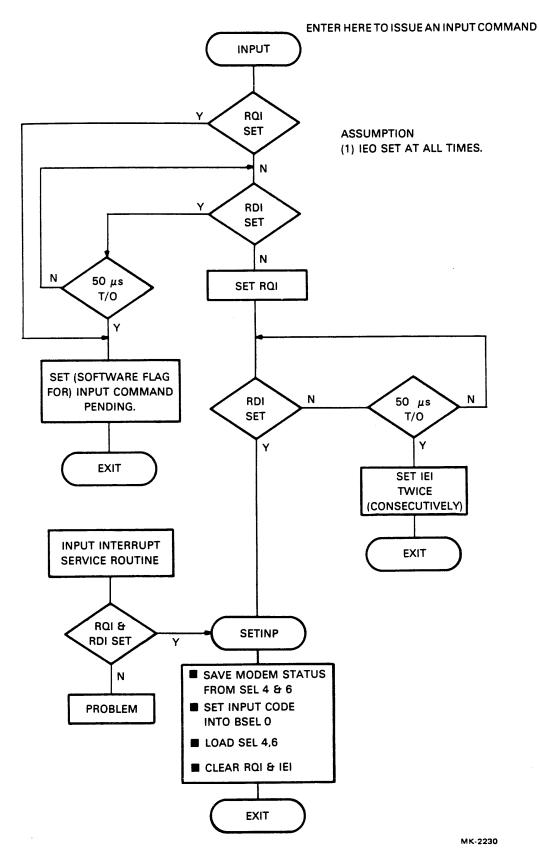

A user program issues a command to the DMR11 by setting up the input command header and requesting the use of the data port. When the DMR11 grants permission to use the data port, the user program passes the command to the DMR11 in the pertinent CSRs. The DMR11 interprets the command and performs the specified actions.

The DMR11 issues error or status information to the user program by storing the command in the pertinent CSRs and by notifying the user program that the status is available for retrieval and processing.

Message data received or transmitted by the DMR11 is written into or read from the user program assigned buffers in the main CPU memory. The DMR11 accesses these buffers through NPRs to a UNIBUS address. A UNIBUS address is an 18-bit address used by an NPR device to access a device on the UNIBUS or a location in main CPU memory.

#### 1.3.1 Command Structure

As previously stated, communication between the main CPU resident user program and the DMR11 is accomplished through a set of four 16-bit UNIBUS CSRs. This is accomplished by using these CSRs to implement an input and output command structure.

There are five input and three output commands. Their functions are discussed in Chapter 3.

#### 1.3.2 Input Commands

Input commands are issued by the user program to initialize, select the mode of operation, and assign receive or transmit buffers to the DMR11.

#### 1.3.3 Output Commands

Output commands provide a means for the DMR11 to report various normal and abnormal (error) conditions concerning the data transfer operation.

Two basic commands are provided:

- 1. Receive or Transmit Buffer Address/Character Count Out and

- 2. Control Out

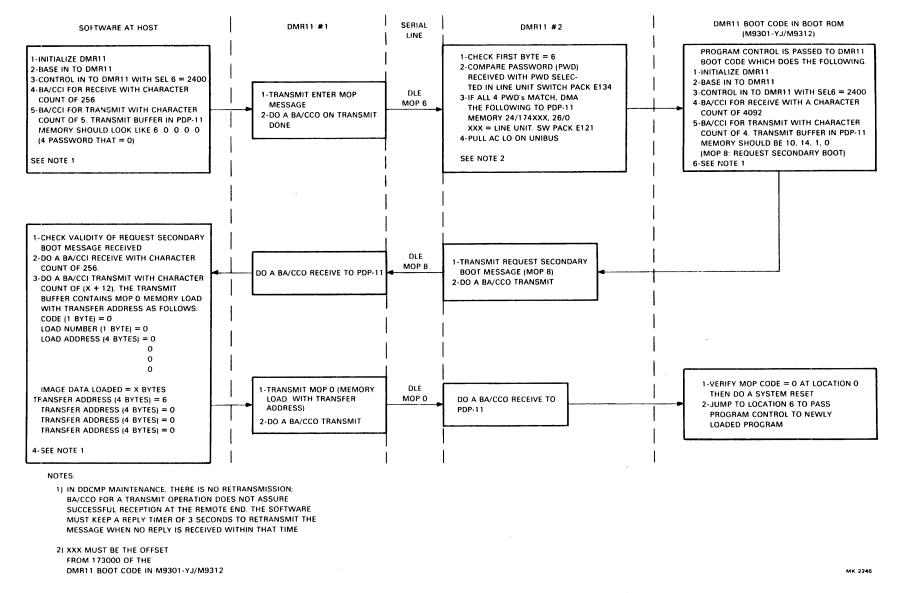

The Buffer Address/Character Count Out command is used to report a successful, error free completion of a receive or transmit buffer and it indicates the actual number of bytes transferred. This command utilizes both Select 4 (SEL 4) and SEL 6 to identify the address of the completed buffer and the actual character count of the transfer. The Control Out command is used to report specific conditions concerning the DDCMP, the user program, the hardware, or the modem. Control Out utilizes SEL 6 to inform the user program as to the nature of the report (refer to the following).

Error Status

Identifies the reason for the error condition (errors can be associated with the DDCMP, the user program, the modem, or other hardware limitations). In some cases the error condition is non-fatal and normal operations can continue. Other errors are fatal, causing the DMR11 to shut down.

#### 1.3.4 DMR11 Operation Sequencing

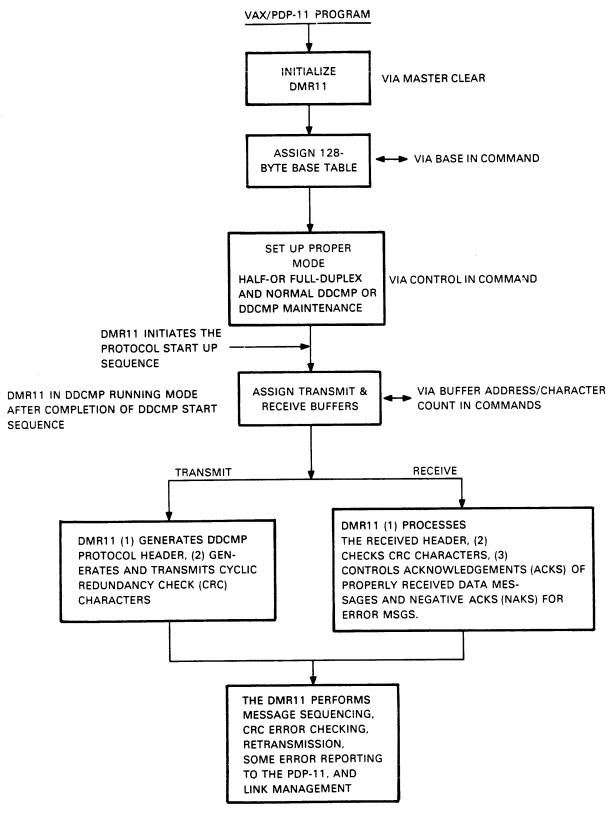

The normal sequence of operation is represented in the flow chart in Figure 1-3.

The user program initializes the DMR11 by issuing the Initialize command with the Master Clear bit set. When the DMR11 has completed the initialization, it sets the Run bit. At this point the user program assigns a 128-byte Base Table in CPU memory to the DMR11 for maintaining error counters and storage of vital information on shut-down. This is done using the Base In command. The user program via the Control In command then sets the DMR11 for either half-duplex or full-duplex and either DDCMP Normal or DDCMP Maintenance Mode. If Normal DDCMP Mode is selected, DMR11 initiates protocol start up.

The user program should now assign transmit and receive buffers to the DMR11 via the Buffer Address/Character Count In command. When a transmit buffer is assigned, the DMR11 issues an NPR to retrieve the data from CPU memory for transmission on the serial line.

If there are receive buffers assigned when the DMR11 receives data over the serial line, it issues an NPR to transfer the data to the CPU memory.

The DMR11 performs message sequencing, link management, cyclic redundancy check (CRC) error checking, error connection via retransmission, and some error reporting to the CPU.

#### 1.3.5 Maintenance Mode Operation

A special DDCMP message format, the maintenance message, is used for down-line loading, restarting, or otherwise maintaining satellite computer systems. Messages in this format are subject to error checking but are unsequenced, unacknowledged, and not retransmitted automatically by the microprocessor.

The user program must initialize the DMR11, give it a Base In with the Resume bit clear, and then give a Control In to put the DMR11 in Maintenance Mode.

#### **1.4 GENERAL SPECIFICATIONS**

The following paragraphs contain performance, electrical, and environmental specifications for all DMR11 configurations. Table 1-2 lists the performance parameters of the DMR11.

#### **1.4.1** Power Requirements

The M8207-RA and M8203 line unit power requirements are listed below:

| Module   | Voltage Rating (Approximate Values) |

|----------|-------------------------------------|

| M8207-RA | + 5 volts @ 5.0 amperes             |

| M8203    | + 5 volts @ 3.0 amperes             |

|          | +15 volts @ .11 amperes             |

|          | -15 volts @ .2 amperes              |

MK-2323

Figure 1-3 DMR11 Operation Sequencing

| Parameter          | Description                                                                |

|--------------------|----------------------------------------------------------------------------|

| Operating Mode     | Full-Duplex or Half-Duplex                                                 |

| Data Format        | Synchronous DDCMP                                                          |

| Special Data Rates | Up to 1M b/s                                                               |

| Cable Length       | Refer to M8203 Line Unit Technical Manual, EK-M8203-TM-<br>001, Appendix B |

#### Table 1-2 DMR11 Performance Parameters

#### 1.4.2 Environmental Requirements – All DMR11s

The DMR11 is designed to operate in a Class C environment as outlined in DEC Standard 102.

- Operating temperature range 5°C to 50°C (41°F to 120°F)

- Relative humidity 10 to 90 percent with a maximum wet bulb of 28°C (82°F) and a minimum dewpoint of 2°C (36°F)

#### 1.5 EIA STANDARDS OVERVIEW (RS-449 vs RS-232-C)

The most common interface standard used in recent years has been the RS-232-C. It does, however, have serious limitations for use in modern data communications systems: the most critical being speed and distance.

For this reason, the RS-449 standard has been developed to replace the RS-232-C. It maintains a degree of compatibility with RS-232-C to accommodate an upward transition to RS-449.

The most significant difference between RS-449 and RS-232-C is the electrical characteristics of signals used between the data communication equipment (DCE) and the data terminal equipment (DTE). The RS-232-C standard uses only unbalanced circuits while the RS-449 uses both balanced and unbalanced electrical circuits. The specifications for these different types of electrical circuits supported by RS-449 are contained in EIA Standards RS-422-A for balanced circuits and RS-423-A for unbalanced circuits. These new standards permit much greater transmission speeds and will allow greater distances between the DTE and DCE. The maximum transmission speeds supported by RS-423-A at 200 feet and 2M b/s for RS-422-A at 200 feet. These normal speed limits being 20K b/s for RS-423-A at 200 feet and 2M b/s for distance, or vice-versa.

Another major difference between RS-232-C and RS-449 is that two new connectors have been specified to allow for the additional leads needed to support new circuit functions and the balanced interface circuits. One connector is a 37 pin cinch used to accommodate the majority of data communications applications. The other is a nine pin cinch used in applications requiring secondary channel functions. Some of the new circuits that have been added in RS-449 support local and remote loopback testing, and standby channel selection.

The transition from RS-232-C to RS-449 will take some time. Therefore, any applications that are interconnected between RS-232-C and RS-449 must adhere to the limitations of RS-232-C, which has a normal speed of 20K b/s at a maximum distance of 50 feet.

.

## **CHAPTER 2** INSTALLATION

#### 2.1 SCOPE

This chapter provides all the necessary information for installing and testing the DMR11 microprocessor subsystem. A checklist, which can be used to verify the installation process, is also included.

## 2.2 UNPACKING AND INSPECTION

The DMR11 is packaged according to commercial packing practices. When unpacking, remove all packing material and check the equipment against the shipping list (Table 2-1 contains a list of supplied items for each configuration). Inspect all parts and carefully inspect the module for cracks, loose components, and separations in the etched paths. Report damages or shortages to the shipper and notify the DIGITAL representative.

# 2.3 INSTALLATION CONSIDERATIONS

Installation of the DMR11 microprocessor/line unit subsystem should be done in four phases:

Phase I - Preinstallation Considerations

Verify system requirements, system placement, and configuration requirements.

Phase II - Microprocessor Installation

Configure, install, and verify microprocessor module via the appropriate diagnostics.

Phase III - Line Unit Installation

Configure the line unit module for the customer application and install, cable, and verify it via appropriate diagnostics.

Phase IV - DMR11 System Testing ٠

> Verify the DMR11 microprocessor subsystem operation with the functional diagnostics and system exercise programs.

# 2.4 PREINSTALLATION CONSIDERATIONS

The following (Table 2-1) should be considered prior to ordering a DMR11 communications interface to insure that the system can accept the DMR11 and that it can be installed correctly. These steps should also be verified at installation time.

| Option   | Parts List                             | Description                                                                                                                   |

|----------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| DMR11-AD |                                        | DMR11 basic subsystem unit containing:                                                                                        |

|          | M8203<br>M8207-RA                      | Line unit module<br>Microprocessor module with DMR11 microcode<br>ROMS                                                        |

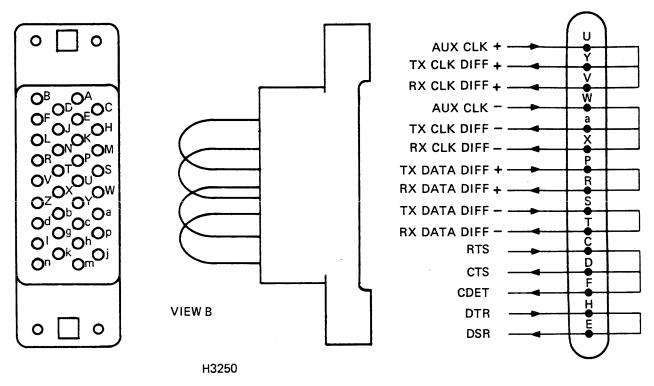

|          | BC08S-1<br>H3254<br>H3255              | Module interconnect cable<br>V.35 and integral module test connector<br>RS-232-C/RS-422-A/RS-423-A module test con-<br>nector |

|          | EK-DMR11-UG-001                        | DMR11 User's Guide                                                                                                            |

|          | MP-00911                               | Customer print set                                                                                                            |

|          | ZJ-306-RB                              | Diagnostic set                                                                                                                |

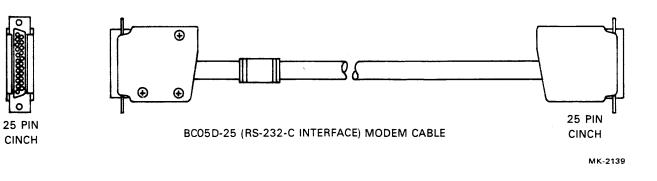

| DMR11-AA |                                        | RS-232-C/RS-423-A interface configuration con-<br>taining:                                                                    |

|          | DMR11-AD<br>BC55C-10<br>H3251<br>H325  | Basic DMR11 unit<br>EIA RS-232-C/RS-423-A cable<br>Cable turnaround test connector<br>Cable turnaround test connector         |

| DMR11-AB |                                        | CCITT V.35 interface configuration containing:                                                                                |

|          | DMR11-AD<br>BC05Z-25<br>H3250          | Basic DMR11 unit:<br>CCITT V.35 cable<br>Cable turnaround test connector                                                      |

| DMR11-AC |                                        | Integral Modem interface configuration contain-<br>ing:                                                                       |

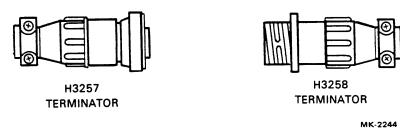

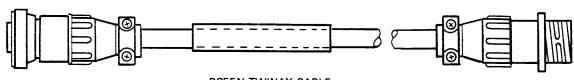

|          | DMR11-AD<br>BC55A-10<br>H3257<br>H3258 | Basic DMR11 unit<br>Integral Modem cable<br>BC55A terminators                                                                 |

| DMR11-AE |                                        | RS-422-A interface configuration containing:                                                                                  |

|          | DMR11-AD<br>BC55B-10<br>H3251          | Basic DMR11 unit<br>RS-422-A cable<br>Cable turnaround test connector                                                         |

| Table 2-1  | DMR11   | Ontion | Packing List  |

|------------|---------|--------|---------------|

| I ADIC #-1 | DIVINII | Option | I ACKING LISU |

#### 2.4.1 System and Device Placement

**2.4.1.1** System Placement – On systems that contain many high speed direct memory access (DMA) devices, there is a probability of adverse bus latency. To help prevent this occurance, the closer the

physical placement of the DMR11 to the processor, the higher the DMA device priority. A single DMR11 at 1M b/s and in full-duplex mode is capable of transferring 125,000 bytes/second/channel X 2 channels (Transmit and Receive). Because the DMR11 performs 16-bit word transfers via nonprocessor request (NPR) transactions to memory, approximately 125,000 NPRs per second at the rate of 8 microseconds/NPR are generated. Customer applications using speeds greater than 250K bits per second (b/s) require UNIBUS placement before all UNIBUS repeaters and before all devices that have a lower NPR rate on the UNIBUS.

**2.4.1.2** Device Placement – The DMR11 requires two hex-height, small peripheral controller (SPC) backplane slots (preferably two adjacent slots). Any SPC backplane [DD11-B(REV E) or later] can accept the DMR11. The DD11-D can accommodate a maximum configuration of three DMR11s.

#### CAUTION

Each DMR11 requires approximately 8 amperes from the +5 volt source. Check to ensure that the supply is capable of providing a total of 24 amperes if a maximum configuration is installed.

#### 2.4.2 System Requirements

1. UNIBUS Loading

M8207-RA microprocessor 1 UNIBUS dc load 5 UNIBUS ac loads

M8203 line unit No UNIBUS loads

2. Power Requirements

Check the power supply before and after installation to ensure against overloading. The microprocessor/line unit total current requirement for the  $\pm 5$  volt supply is approximately 8 amperes. Additionally, the unit requires  $\pm 15$  volts for the silos, level conversion logic, and Integral Modem. Power requirements for the microprocessor/line units are listed in Table 2-2.

| Table 2-2 | DMR11 | Voltage | Chart |

|-----------|-------|---------|-------|

|-----------|-------|---------|-------|

| Module   | Voltage Rating<br>(Approximate Values) | Maximum<br>Voltage | Minimum<br>Voltage | Back Plane<br>Pin |

|----------|----------------------------------------|--------------------|--------------------|-------------------|

| M8207-RA | + 5 Volts @ 5.0 A                      | + 5.25             | + 5.0              | C1A2              |

| M8203    | + 5 Volts @ 3.0 A                      | + 5.25             | + 5.0              | C1A2              |

|          | +15 Volts @ .1 A                       | +15.75             | +14.25             | CIUI              |

|          | -15 Volts @ .2 A                       | -15.75             | -14.25             | C1B2              |

3. Interrupt Priority

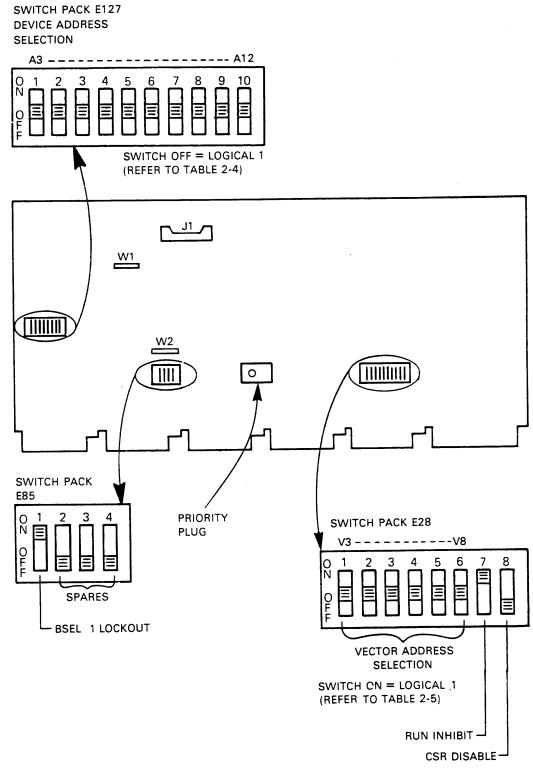

The interrupt priority is selected by priority plug E77 on the M8207-RA microprocessor module. This plug is preset to select priority five (BR5). Refer to Figure 2-1 for the priority plug location.

4. Device Address Assignment

The DMR11 resides in the floating address space of the Input/Output (I/O) page of memory. The ranking assignment of the DMR11 is equal to the DMC11 ranking number seven.

The selection of the device address is accomplished by Switch Pack E127 on the M8207-RA microprocessor module. Refer to Figure 2-1 for the switch pack placement. Since the DMR11 will reside at the same ranking as the DMC11, the operating system can determine what type of device resides at that address location by reading the second control and status register (CSR) of the device and examining the high byte.

If the bootstrapping feature of the DMR11 or DMC11 is to be used, only the devices that reside at unit zero and/or unit one address location can implement this feature, unless bootstrap is designed to accept more units.

Refer to Appendix A if more information is needed on the floating address allocation.

5. Device Vector Address Assignment

The DMR11 resides in the floating vector space of the reserved vector area of memory. The ranking assignment of the DMR11 is equal to the DMC11 ranking number 27. The selection of the device vector address is accomplished by Switch Pack E28 on the M8207-RA micro-processor module. Refer to Figure 2-1 for the location of the switch pack. Appendix A contains more information on floating vector allocation.

#### 2.5 MICROPROCESSOR INSTALLATION

#### 2.5.1 Backplane Considerations

Perform the following on the SPC slot that will contain the DMR11, M8207-RA microprocessor module (selected at preinstallation).

- 1. Verify that the backplane voltages are within the specified tolerances listed in Table 2-2.

- 2. Turn system power off and remove the NPR Grant (NPG) wire that runs between CA1 and CB1 on that backplane slot for the M8207-RA module.

#### NOTE

#### Be sure to replace this jumper if the microprocessor is removed from the system.

3. Perform resistance checks on the backplane voltage sources to ground to ensure that no short circuit conditions exist. Refer to Table 2-2 for backplane pin assignments.

#### 2.5.2 M8207-RA Considerations

Perform the following on the DMR11 M8207-RA microprocessor module.

1. Ensure that the module version number is an M8207-RA, which indicates DMR11 micro-code.

MK-2120

Figure 2-1 M8207-RA Microprocessor Switch/Jumper Locations

- 2. Verify that M8207-RA jumpers W1 and W2 are installed correctly (refer to Jumper Table 2-3).

- 3. Configure Switch Pack E127 to implement the correct device address for the DMR11 as determined from the floating address allocation. Refer to Table 2-4 for the correlation between switch number and address bit. A switch OFF (open) responds to logical one on the UNIBUS. Refer to Appendix A for additional information on floating address allocation.

- 4. Configure Switch Pack E28 to implement the correct vector address for the DMR11 as determined from the floating vector allocation. Refer to Table 2-5 for the correlation between switch number and vector bit. A switch ON (closed) responds to a logical one on the UNIBUS. Refer to Appendix A for additional information on floating vector allocation.

- 5. Verify that the switch selectable features of the M8207-RA are configured as follows (Table 2-6 provides a summary of switch selectable features):

- Run Inhibit Switch Pack E28, switch 7; always ON.

- CSR Inhibit Switch Pack E28, switch 8; always OFF.

- Byte Select/Lockout (BST) Switch Pack E85, switch 1, normally ON (allows all functions in Byte Select 1 to be used). If the switch is OFF, the Run bit is always asserted and will not allow diagnostic testing.

## NOTE

#### Switch Pack E85, switches 2, 3, and 4 are not used.

6. Verify that the priority plug is a BR5 and is installed correctly in location E77.

| Jumper<br>Number | Normal<br>Configuration                                                                                                                            | Function                                                                                              |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| WI Always In     | Microprocessor Clock Enable – When removed it disables the micro-<br>processor clock. Removed only for automatic module testing at the<br>factory. |                                                                                                       |

| W2               | Always In                                                                                                                                          | Bus ac Low Enable – When removed it disables a program asserted ac low signal passed onto the UNIBUS. |

Table 2-3

M8207-RA

DMR11

Jumper

Chart

#### 2.5.3 M8207-RA Insertion

Carefully insert the M8207-RA microprocessor module into the selected SPC slot and perform the following tasks:

- 1. Perform resistance checks on the backplane voltage sources to ground to ensure that no short circuit conditions exist on the module. Refer to Table 2-2 for backplane pin assignments.

- 2. Turn system power ON and verify that the backplane voltages are within the specified tolerances listed in Table 2-2.

- 3. Load and execute the M8207 static diagnostics, parts one and two (no test connectors are required).

- A. PDP-11 System

CZDMP\* M8207 Static Test 1 CZDMQ\* M8207 Static Test 2

B. VAX-11/780 Systems

EVDXA COMM Microprocessor Repair Level Diagnostics REV \*.\*

Chapter 4 provides additional information on these diagnostics. Upon obtaining a minimum of five error free end passes, proceed to the M8203 line unit installation section.

#### 2.6 LINE UNIT INSTALLATION

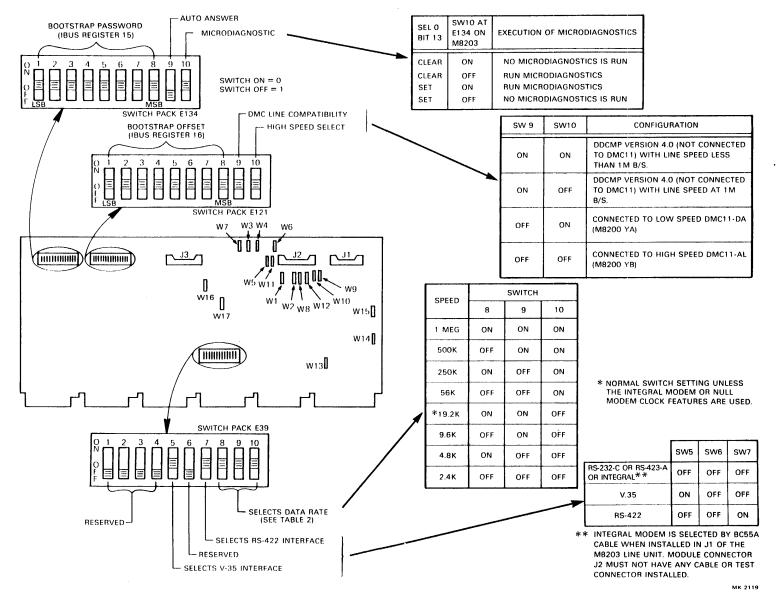

The M8203 line unit is a universal module with various types of interface capabilities. The M8203 line unit does not present any ac or dc loads to the UNIBUS and only draws power from the backplane slot in which it resides. All data and control signals flow into and out of the line unit via a berg port to the microprocessor. Because of the various M8203 applications, the configurations for each may be different and are selected via switches, jumpers, and different cables. To provide a better understanding of these variations, a number of tables describing each switch pack, jumper, and cable function (as listed below) has been created for reference. Table 2-7 lists the normal M8203 line unit configurations for the different types of DMR11 options without the bootstrap feature selected. Also, refer to the following:

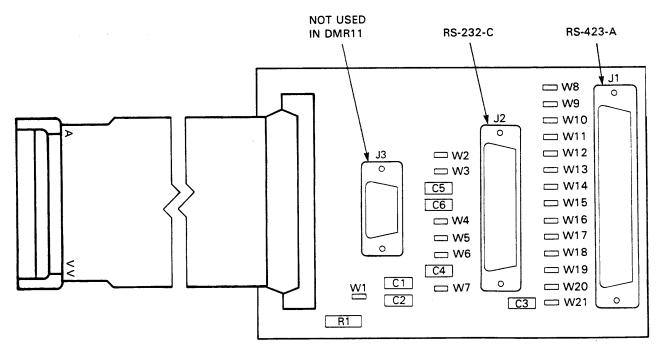

- Table 2-8 Jumper Functions These jumpers are used to select various interface standard parameters and modem interface signals, depending on application and modem type. Additional jumpers are available on the BC55C (panel) cable for additional interface signal selection.

- Table 2-9 Switch Pack E39 Functions This switch pack allows proper selection of interface driver and receiver control logic and different line speeds for various applications.

- Table 2-10 Switch Pack E121 Functions This switch pack is provided for the selection of the bootstrap offset address for the remote load detect feature (if used) and for various microcode switch features.

- Table 2-11 Switch Pack E134 Functions This switch pack is provided for the selection of the bootstrap password for the remote load detect feature (if used) and for various micro-code switch features.

- Table 2-12 Cable Description This table lists the functions and uses of each cable used with the DMR11.

- Figure 2-2 shows the jumper and switch pack placements on the M8203 line unit.

- Figure 2-3 shows the microprocessor and line unit installation.

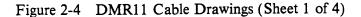

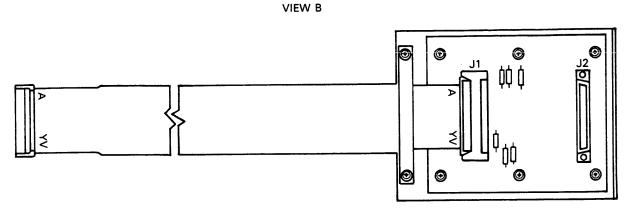

- Figure 2-4 shows the outline drawings of DMR11 cables.

| Switches | Fu                        | nctio | n             |      |             |            |                    |              |           |                   |                   |                   |                   |                   |        |                                                              |                                                                                  |

|----------|---------------------------|-------|---------------|------|-------------|------------|--------------------|--------------|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|--------|--------------------------------------------------------------|----------------------------------------------------------------------------------|

| 1-10     | Device Address Selection: |       |               |      |             |            |                    |              |           |                   |                   |                   |                   |                   |        |                                                              |                                                                                  |

|          | MSB                       |       |               |      |             |            |                    |              |           |                   |                   |                   |                   |                   |        |                                                              | LSB                                                                              |

|          |                           | 15    | 14            | 13   | 12          | 11         | 10                 | 9            | 8         | 7                 | 6                 | 5                 | 4                 | 3                 | 2      | 1                                                            | 0                                                                                |

|          |                           | 1     | 1             | 1    |             |            | S                  |              | CH P      | ACK               |                   |                   |                   |                   | 0      | 0                                                            | 0                                                                                |

|          |                           |       |               |      |             |            |                    |              |           |                   |                   |                   |                   |                   |        |                                                              |                                                                                  |

|          |                           | S     | WITC          | H    | S10         | <b>S</b> 9 | <b>S</b> 8         | <b>S</b> 7   | <b>S6</b> | S5                | <b>S4</b>         | <b>S</b> 3        | S2                | <b>S1</b>         | )<br>A | DEVIC                                                        | CE<br>ESS                                                                        |

|          |                           |       |               |      |             |            | OFF                |              |           | OFF<br>OFF<br>OFF | OFF<br>OFF<br>OFF | OFF<br>OFF<br>OFF | OFF<br>OFF<br>OFF | OFF<br>OFF<br>OFF |        | 7600<br>7600<br>7600<br>7600<br>7600<br>7600<br>7600<br>7600 | 10<br>20<br>30<br>40<br>50<br>50<br>50<br>70<br>00<br>00<br>00<br>00<br>00<br>00 |

|          |                           | NOTI  | E: S <b>W</b> | лтсн | DEV<br>SELI | тсн        | PACI<br>ADDR<br>DN | < E12<br>ESS |           |                   |                   |                   |                   | BUS.              | 1      | Switc<br>E127                                                | h Pack                                                                           |

Table 2-4 Switch Pack E127 Selections

ı

| Switches  | Functior                  | Ì  |       |    |          |              |             |             |          |                |            |          |     |          |            |          |

|-----------|---------------------------|----|-------|----|----------|--------------|-------------|-------------|----------|----------------|------------|----------|-----|----------|------------|----------|

| - <u></u> |                           | S  | witch | ON | equal    | s a lo       | NO<br>gical | TE<br>one ( | 1) or    | the l          | UNIE       | BUS.     |     |          |            |          |

| 1-6       | Vector Address Selection: |    |       |    |          |              |             |             |          |                |            |          |     |          |            |          |

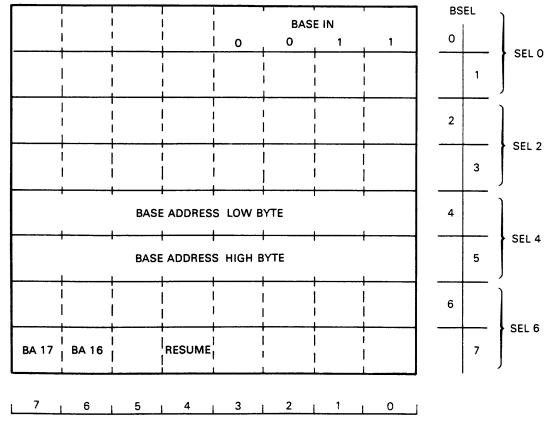

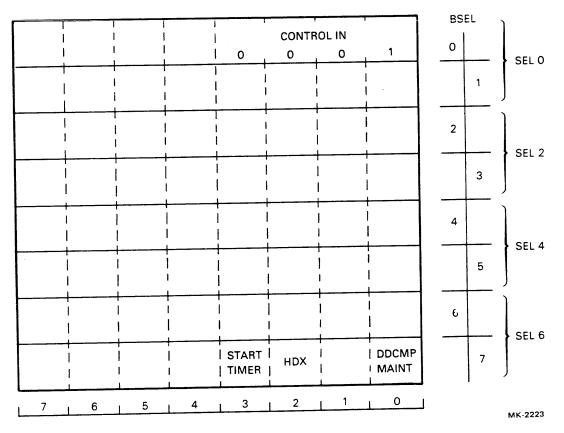

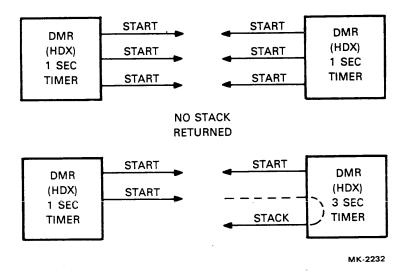

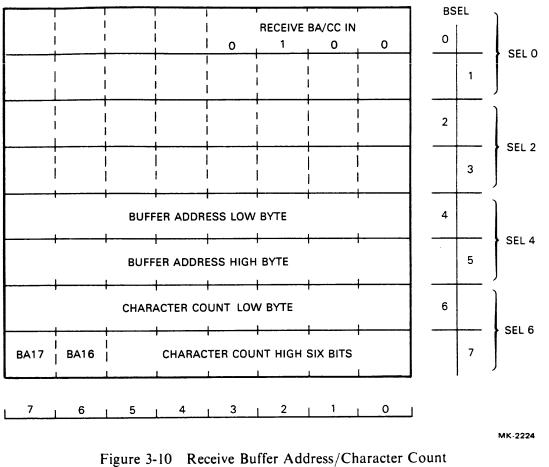

|           | MS                        | B  |       |    |          |              |             |             |          |                | ·          |          |     |          |            | LSB      |