EK-DMB32-UG-001

# DMB32 User Guide

EK-DMB32-UG-001

# DMB32 User Guide

Prepared by Educational Services of Digital Equipment Corporation

1

# Copyright © 1986 by Digital Equipment Corporation

#### All Rights Reserved

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation, Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

Using Digital's networked computer systems, this book was produced electronically by the Media, Publishing and Design Services department in Reading, England.

#### Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation.

digital

DEC DECmate DECUS DECwriter DIBOL MASSBUS PDP P/OS Professional Rainbow RSTS RSX RT UNIBUS VAX VMS VT Work Processor

# CONTENTS

# CHAPTER 1 INTRODUCTION

| 1.1     | SCOPE                              | 1-1  |

|---------|------------------------------------|------|

| 1.2     | OVERVIEW                           | 1-1  |

| 1.3     | FUNCTIONAL DESCRIPTION             | 1-2  |

| 1.3.1   | Data Transfer                      | 1-4  |

| 1.3.2   | Interrupts                         | 1-6  |

| 1.3.3   | Device Registers                   | 1-6  |

| 1.3.3.1 | VAXBI Registers                    | 1-6  |

| 1.3.3.2 | DMB32 Registers                    | 1-6  |

| 1.4     | PHYSICAL DESCRIPTION               | 1-7  |

| 1.4.1   | The DMB32 Option                   | 1-7  |

| 1.4.2   | The T1012 Module                   | 1-8  |

| 1.4.3   | The H3033 Distribution Panel       | 1-9  |

| 1.4.4   | Communications Interfaces          | 1-9  |

| 1.4.4.1 | Asynchronous Interface             | 1-10 |

| 1.4.4.2 | The Synchronous Interface          | 1-12 |

| 1.4.4.3 | The Printer Interface              | 1-13 |

| 1.5     | SPECIFICATIONS                     | 1-13 |

| 1.5.1   | Electrical Requirements            | 1-13 |

| 1.5.2   | Functional Parameters              | 1-13 |

| 1.5.2.1 | Synchronous Functional Parameters  | 1-13 |

| 1.5.2.2 | Asynchronous Functional Parameters | 1-14 |

| 1.5.2.3 | Printer Port Functional Parameters | 1-14 |

| 1.5.2.4 | Throughput                         | 1-14 |

| 1.5.3   | Environmental Specifications       | 1-15 |

| 1.5.3.1 | Operating Environment              | 1-15 |

| 1.5.3.2 | Storage Environment                | 1-15 |

|         |                                    |      |

# CHAPTER 2 INSTALLATION

| 2.1     | SCOPE                                   | 2-1 |

|---------|-----------------------------------------|-----|

| 2.2     | INSTALLATION TASK LIST                  | 2-1 |

| 2.3     | SITE PLANNING                           | 2-2 |

| 2.4     | DMB32 INSTALLATION KITS                 | 2-2 |

| 2.5     | INSTALLATION CHECKS                     | 2-3 |

| 2.6     | CONFIGURATION RULES                     | 2-3 |

| 2.7     | MECHANICAL INSTALLATION                 | 2-3 |

| 2.7.1   | Electro-Static Discharge Precautions    | 2-3 |

| 2.7.1.1 | Anti-Static Wrist Strap                 | 2-3 |

| 2.7.1.2 | Conductive Module Containers            | 2-4 |

| 2.7.2   | T1012 Module Installation               |     |

| 2.7.3   | Transition Header Assembly Installation | 2-6 |

| 2.7.4   | Ribbon Cable Installation               | 2-6 |

| 2.7.5   | Distribution Panel Installation                  | 2.6               |

|---------|--------------------------------------------------|-------------------|

| 2.8     | ACCEPTANCE TESTING                               | ····· 2-0<br>2_8  |

| 2.8.1   | Power-Up And Self-Test                           | ····· 2-0<br>2_0  |

| 2.8.2   | Diagnostics                                      | ····· 2-9<br>2_10 |

| 2.9     | CABLING                                          | 2-10              |

| 2.9.1   | H3033 Distribution Panel                         | 2-10              |

| 2.9.2   | Adapter Cables                                   | 2-10              |

| 2.9.2.1 | V.35 Adapter Cable                               | 2-12              |

| 2.9.2.2 | V.24 Adapter Cable                               | 2-13              |

| 2.9.2.3 | RS-422 Adapter Cable                             | 2-14              |

| 2.9.2.4 | RS-423-A Adapter Cable                           | 2-16              |

| 2.9.3   | Loopback Connectors                              | 2-16              |

| 2.9.3.1 | H3196 50-Way Balanced Loopback Connector         | 2-17              |

| 2.9.3.2 | H3195 50-Way Unbalanced Loopback Connector       | 2-17              |

| 2.9.3.3 | H3197 25-Way Loopback Connector (Async Channels) | 2-18              |

| 2.9.3.4 | H3250 34-Way Loopback Connector (V.35)           | 2-10              |

| 2.9.3.5 | H3248 37-Way Loopback Connector (V.24)           | 2_20              |

| 2.9.3.6 | H3198 37-Way Loopback Connector (RS-422/423)     | 2-20              |

|         |                                                  |                   |

# CHAPTER 3 OPERATION AND PROGRAMMING

| 3.1    |   | SCOPE                                                | 3-1  |

|--------|---|------------------------------------------------------|------|

| 3.2    |   | OPERATION                                            | 3-1  |

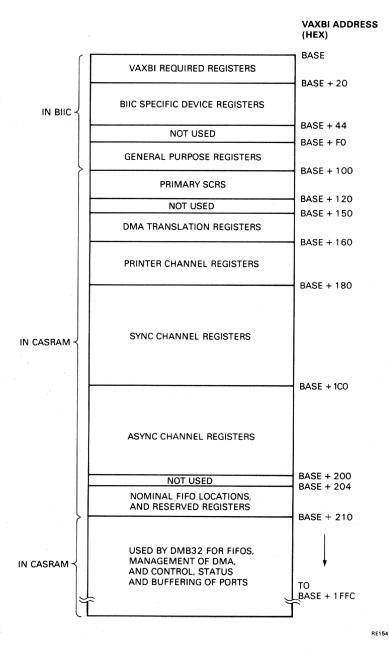

| 3.2.1  |   | DMB32 Register Map                                   | 3-1  |

| 3.2.2  |   | Register Access                                      | 3-1  |

| 3.3    |   | REGISTER BIT DEFINITIONS                             | 3-5  |

| 3.3.1  | - | Device Type Register (DTYPE)                         | 3-6  |

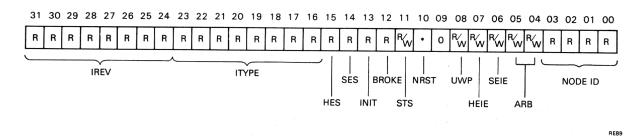

| 3.3.2  |   | VAXBI Control and Status Register (VAXBICSR)         | 3-6  |

| 3.3.3  |   | Bus Error Register (BER)                             | 3-8  |

| 3.3.4  |   | Error Interrupt Control Register (EINTRCSR)          | 3-10 |

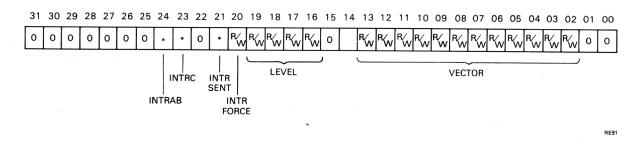

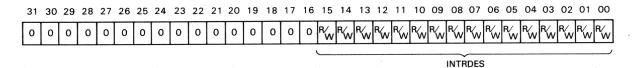

| 3.3.5  |   | Interrupt Destination Register (INTRDES)             | 3-11 |

| 3.3.6  |   | Starting Address Register (SADR)                     | 8-11 |

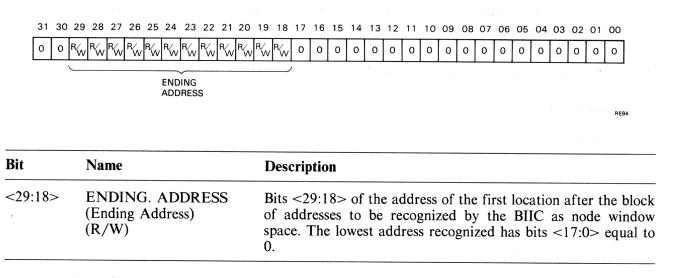

| 3.3.7  |   | Ending Address Register (EADR)                       | 3-12 |

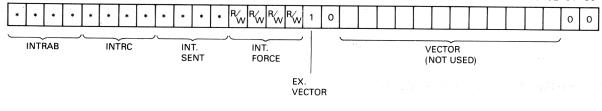

| 3.3.8  |   | User Interface Interrupt Control Register (UINTRCSR) | 3-12 |

| 3.3.9  |   | General Purpose Register 0 (GPR0)                    | 8-13 |

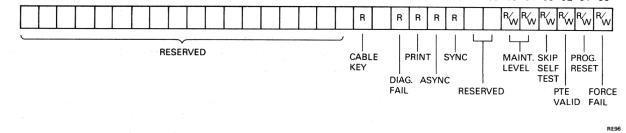

| 3.3.10 |   | Maintenance Register (MAINT)                         | 3-14 |

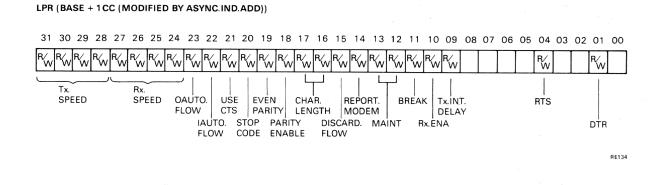

| 3.3.11 |   | Async Control And Status Register (ACSR)             | 8-16 |

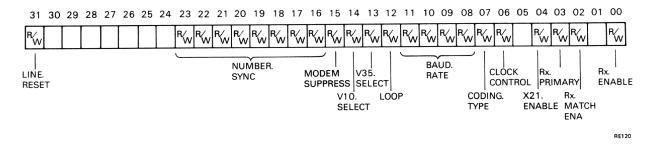

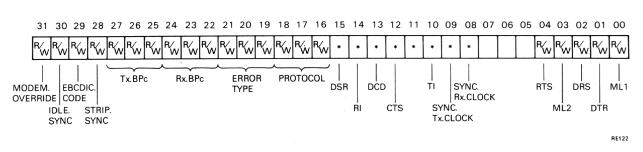

| 3.3.12 |   | Sync Control And Status Register (SCSR)              | 8-17 |

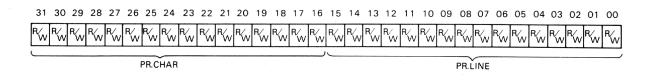

| 3.3.13 |   | Printer Control And Status Register (PCSR)           | 3-17 |

| 3.3.14 |   | Device Configuration Register (CONFIG)               | 1-18 |

| 3.3.15 |   | Second Async Control And Status Register (ACSR2)     | 1-19 |

| 3.3.16 |   | Second Sync Control And Status Register (SCSR2)      | -20  |

| 3.3.17 |   | Second Printer Control And Status Register (PCSR2)   | -20  |

| 3.3.18 |   | System Page Table Register (SPTE)                    | -21  |

| 3.3.19 |   | System Page Table Size Register (SPTS)               | -21  |

| 3.3.20 |   | Global Page Table Register (GPTE)                    | -22  |

| 3.3.21 |   | Global Page Table Size Register (GPTS)               | -22  |

| 3.3.22 |   | Printer Prefix/Suffix Control Register (PFIX)        | -23  |

| 3.3.23 |   | Printer Buffer Address Register (PBUFFAD)            | -24  |

| 3.3.24 |   | Printer Buffer Count Register (PBUFFCT)              | -24  |

| 3.3.25 |   | Printer Control Register (PCTRL)                     | -25  |

| 3.3.26 |   | Printer Carriage Counter Register (PCAR)             | -28  |

| 3.3.27  | Printer Page Size Descriptor Register (PSIZE)            | -29          |

|---------|----------------------------------------------------------|--------------|

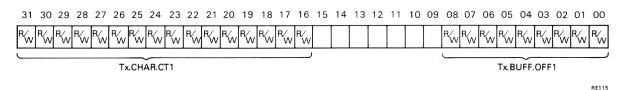

| 3.3.28  | Sync Transmit Buffer 1 Address Register (TBUFFAD1) 3-    | -29          |

| 3.3.29  | Sync Transmit Buffer 1 Count/Offset Register (TBUFFCT1)  | -30          |

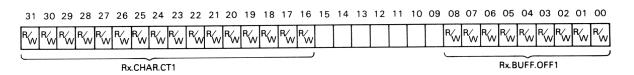

| 3.3.30  | Sync Receive Buffer 1 Address Register (RBUFFAD1) 3      | -30          |

| 3.3.31  | Sync Receive Buffer 1 Count/Offset Register (RBUFFCT1) 3 | -31          |

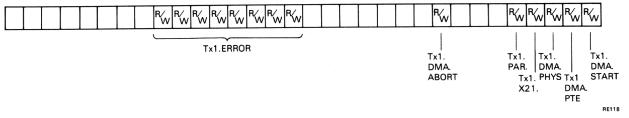

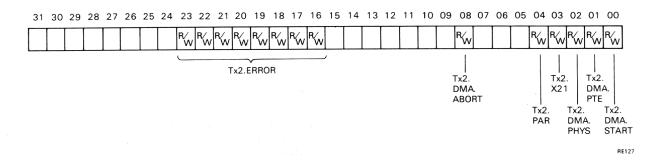

| 3.3.32  | Sync Transmit Buffer 1 Control Register (TLNCTRL1)       | -31          |

| 3.3.33  | Sync Receive Buffer 1 Control Register (RLNCTRL1)        | -33          |

| 3.3.34  | Sync Line Parameters Register 1 (LPR1) 3                 | -35          |

| 3.3.35  | Sync Line Parameters Register 2 (LPR2)                   | -37          |

| 3.3.36  | Sync Transmit Buffer 2 Address Register (TBUFFAD2)       | -39          |

| 3.3.37  | Sync Transmit Buffer 2 Count/Offset Register (TBUFFCT2)  | -40          |

| 3.3.38  | Sync Receive Buffer 2 Address Register (RBUFFAD2)        | -40          |

| 3.3.39  | Sync Receive Buffer 2 Count/Offset Register (RBUFFCT2)   | -41          |

| 3.3.40  | Sync Transmit Buffer 2 Control Register (TLNCTRL2)       | -41          |

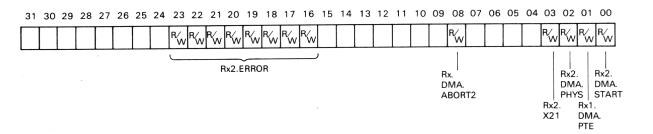

| 3.3.40  | Sync Receive Buffer 2 Control Register (RLNCTRL2)        | -43          |

| 3.3.41  | Sync Line Parameters Register 3 (LPR3)                   | -44          |

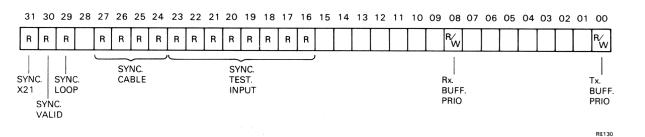

| 3.3.43  | Sync Buffer Control Register (BUFCTRL)                   | -45          |

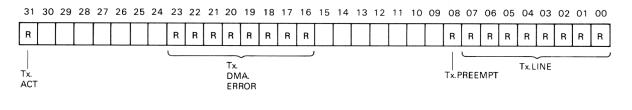

| 3.3.43  | Async Transmission Preempt Buffer (PREEMPT)              | -47          |

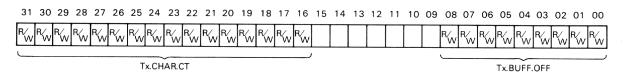

| 3.3.44  | Async Transmit Buffer Address Register (TBUFFAD)         | -47          |

| 3.3.46  | Async Transmit Buffer Count/Offset Register (TBUFFCT)    | -48          |

|         | Async Line Parameters Register (LPR)                     | -48          |

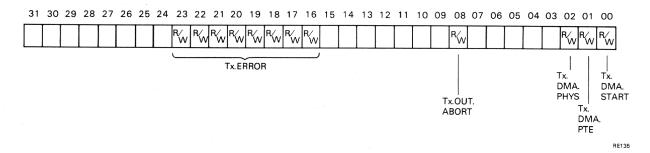

| 3.3.47  | Async Line Control Register (LI R)                       |              |

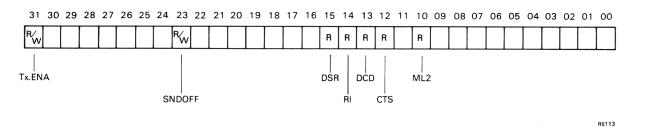

| 3.3.48  | Async Line Status Register (LSTAT)                       |              |

| 3.3.49  | Async Flow Control Characters (FLOWC)                    |              |

| 3.3.50  | Async Transmit Completion FIFO (TBUF)                    | -58          |

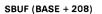

| 3.3.51  | Sync Line Completion FIFO (SBUF)                         | -59          |

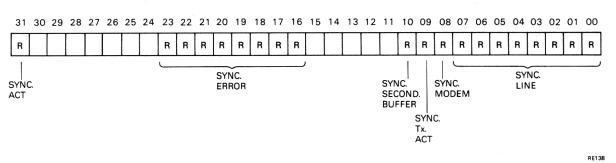

| 3.3.52  | Async Receive Buffer (RBUF)                              |              |

| 3.3.53  | PROGRAMMING FEATURES                                     |              |

| 3.4     | Initialization                                           |              |

| 3.4.1   | Configuration                                            |              |

| 3.4.2   | Using the FIFOs                                          | 8-64         |

| 3.4.3   | Receiving via the RX FIFO                                | 8-64         |

| 3.4.4   | Preempt Transfers                                        |              |

| 3.4.5   | DMA Operations                                           | 2.61         |

| 3.4.6   | DMA Operations                                           | 2 65         |

| 3.4.6.1 | Address Translation                                      |              |

| 3.4.6.2 | Transmitting Data                                        |              |

| 3.4.6.3 | Receiving Data                                           | 2 66         |

| 3.4.7   | Interrupt Control                                        | 2 67         |

| 3.4.8   | Error Codes                                              | 3 68         |

| 3.4.8.1 |                                                          |              |

| 3.4.8.2 | DMA Error                                                | 2 60         |

| 3.4.8.3 | Message Error                                            | 2 40         |

| 3.4.8.4 | Last Character Incomplete                                | 2 60         |

| 3.4.8.5 | Buffer Error                                             | 2-09         |

| 3.4.8.6 | Modem Error                                              |              |

| 3.4.8.7 | Aborted by Host                                          | 2 70         |

| 3.4.8.8 | Printer Offline                                          | 2-70<br>2-70 |

| 3.4.8.9 | Internal Error                                           | 3-70<br>3 70 |

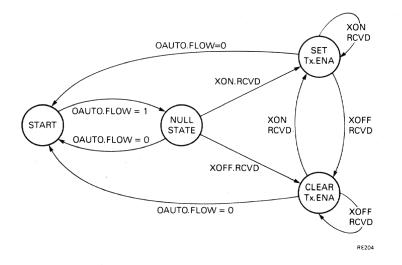

| 3.4.9   | Automatic Flow-Control                                   | 5-/U         |

| 3.4.9.1 | IAUTO.FLOW                                               | 3-/1<br>2 72 |

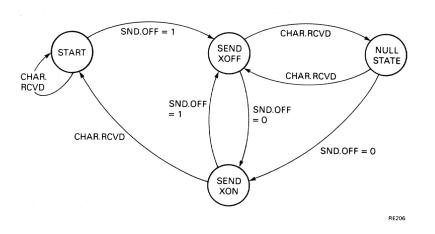

| 3.4.9.2 | SNDOFF                                                   | 3-12         |

| 3.4.9.3 | OAUTO.FLOW                                               | 5-12         |

|         |                                                          |              |

v

| 5.1.2.1 | DISCARD.FLOW                | 3-72 |

|---------|-----------------------------|------|

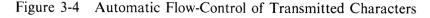

| 3.4.9.5 | Flow-Control State Diagrams | 3-72 |

| 3.4.9.6 | Flow-Control Characters     | 3-74 |

| 3.4.10  | Async Modem Control         |      |

| 3.4.11  | Sync Modem Control          | 3-74 |

| 3.4.12  | Selecting Protocols         |      |

# CHAPTER 4 TROUBLESHOOTING

| 4.1     |   | SCOPE                                  | 4-1  |

|---------|---|----------------------------------------|------|

| 4.2     |   | DIAGNOSTICS                            | 4-1  |

| 4.3     |   | ON-BOARD SELF-TEST DIAGNOSTIC          | 4-2  |

| 4.3.1   |   | Starting the Self-Test                 | 4-3  |

| 4.3.2   |   | Self-Test Indications and Error Codes  | 4-3  |

| 4.3.2.1 |   | Self-Test Error Codes in the RX FIFO   | 4-4  |

| 4.3.2.2 | 2 | Test Summary Register Bit Definitions  | 4-5  |

| 4.4     |   | EVDAK STANDALONE DIAGNOSTIC            | 4-6  |

| 4.4.1   |   | Starting EVDAK                         | 4-8  |

| 4.4.2   |   | Options                                | 4-9  |

| 4.4.3   |   | EVENT Flags                            | 4-10 |

| 4.4.4   |   | Sections                               | 4-11 |

| 4.4.5   |   | Error Messages                         | 4-11 |

| 4.5     |   | EVDAJ ONLINE DIAGNOSTIC (Async)        | 3-11 |

| 4.5.1   |   | Starting EVDAJ                         | 4-13 |

| 4.5.2   |   | Options                                | 4-14 |

| 4.5.3   |   | EVENT Flags                            | 4-14 |

| 4.5.4   |   | Sections                               | 4-14 |

| 4.5.5   |   | Error Messages                         | 4-15 |

| 4.6     |   | EVDAL ONLINE DIAGNOSTIC (Sync)         | 4-15 |

| 4.6.1   |   | Starting EVDAL                         | 4-16 |

| 4.6.2   |   | EVENT Flags                            | 4-16 |

| 4.6.3   |   | Sections                               | 4-17 |

| 4.6.4   |   | Error Messages                         | 4-17 |

| 4.7     |   | EVAAA ONLINE DIAGNOSTIC (Printer)      | 4-17 |

| 4.7.1   |   | Starting EVAAA 4                       | 4-18 |

| 4.7.2   |   | Error Messages                         | 1-19 |

| 4.8     |   | USER ENVIRONMENT TEST PROGRAM (UETP) 4 | 4-19 |

| 4.9     |   | DATA COMMUNICATIONS LINK TEST (DCLT) 4 | 1-19 |

| 4.10    |   | FIELD REPLACEABLE UNITS (FRUs) 4       | 1-19 |

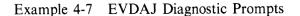

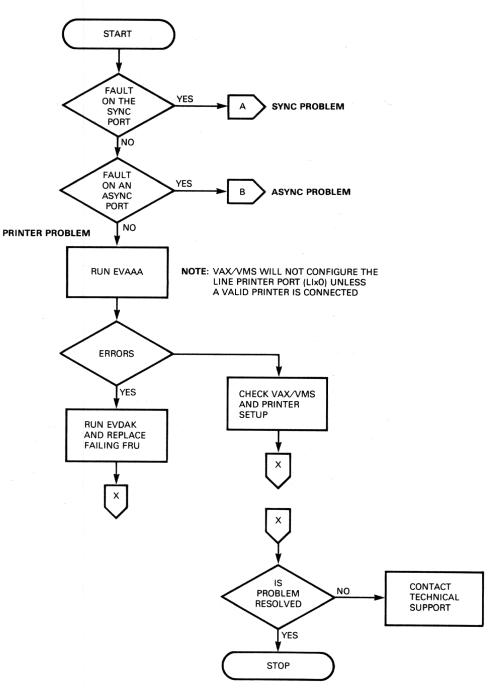

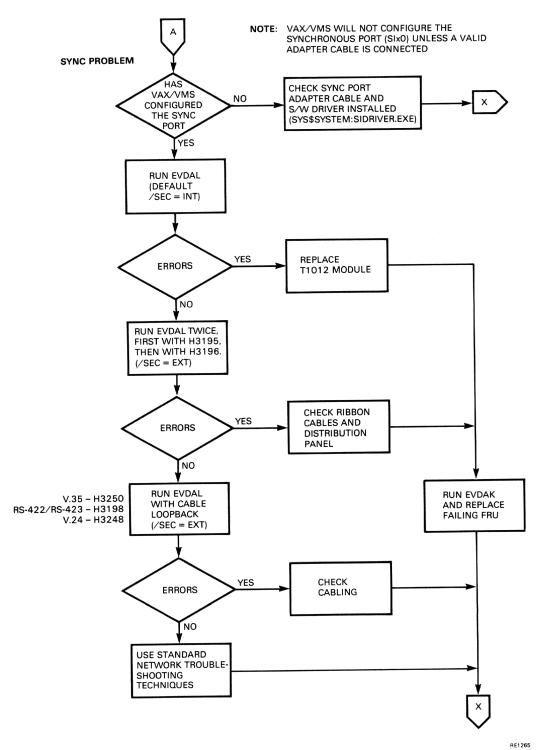

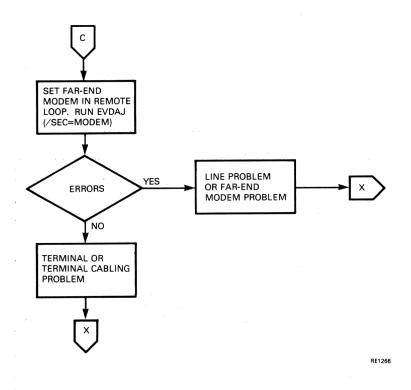

| 4.11    |   | TROUBLESHOOTING FLOWCHART 4            | 1-21 |

# **APPENDIX A GLOSSARY**

# FIGURES

|     | Title                           |      |

|-----|---------------------------------|------|

| 1-1 | DMB32 Typical Configuration     | 1-3  |

| 1-2 | DMB32 Functional Block Diagram  | 1-5  |

| 1-3 | T1012 Module                    | 1-8  |

| 1-4 | H3033 Distribution Panel        |      |

| 1-5 | J0 to J7 Async Connector Detail |      |

| 1-6 | Sync Connector Detail           | 1-12 |

| 1-7  | Printer Connector Detail                         | 1-13 |

|------|--------------------------------------------------|------|

| 2-1  | DMB32 Installation                               | 2-5  |

| 2-2  | The VAXBI Backplane (Rear View)                  | 2-7  |

| 2-3  | The H3033 Distribution Panel (Rear View)         | 2-8  |

| 2-4  | H3033 Distribution Panel (Front View)            | 2-11 |

| 2-5  | 50-Way Sync Channel Connector                    | 2-12 |

| 2-5  | BC19F-02 (17-01112-01) Adapter Cable Detail      | 2-13 |

| 2-0  | BC19D-02 (17-01110-01) Adapter Cable Detail      | 2-14 |

| 2-8  | BC19B-02 (17-01108-01) Adapter Cable Detail      | 2-15 |

| 2-9  | BC19E-02 (17-01111-01) Adapter Cable Detail      | 2-16 |

| 2-10 | H3197 Loopback Connector                         | 2-18 |

| 2-10 | H3250 Loopback Connector                         | 2-19 |

| 2-11 | H3248 Loopback Connector                         | 2-20 |

| 2-12 | H3198 Loopback Connector                         | 2-21 |

| 3-1  | DMB32 Register Map                               | 3-2  |

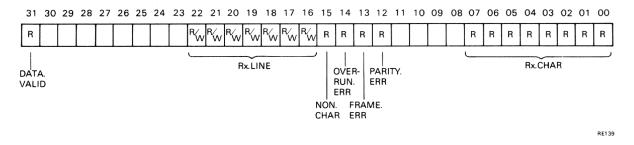

| 3-2  | Handling an Unaligned DMA Buffer                 | 3-65 |

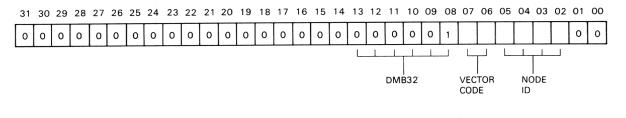

| 3-3  | DMB32 Interrupt Vectors                          | 3-67 |

| 3-4  | Automatic Flow-Control of Transmitted Characters | 3-72 |

| 3-4  | Automatic Flow-Control of Received Characters    | 3-73 |

| 00   | Program Initiated Flow-Control                   | 3-73 |

| 3-6  | F IUgrani miniatou i num-control                 | 0 10 |

# TABLES

| Table No. | Title                                           |    |

|-----------|-------------------------------------------------|----|

| 1-1       | EIA/CCITT Signal Relationships 1-11             |    |

| 1-2       | Synchronous Functional Parameters 1-13          | į  |

| 1-3       | Asynchronous Functional Parameters 1-14         | •  |

| 1-4       | Printer Port Functional Parameters 1-14         | ł  |

| 1-5       | Maximum Sensible Speeds (Sync Port) 1-15        | į. |

| 2-1       | DMB32 Installation Kit Details 2-2              |    |

| 2-2       | Ribbon Cable Connections 2-6                    | )  |

| 2-3       | H3196 Balanced Loopback Interconnections 2-17   | ł  |

| 2-4       | H3195 Unbalanced Loopback Interconnections 2-17 | 1  |

| 3-1       | DMB32 Registers 3-3                             | 3  |

| 4-1       | Scope and Duration of Self-Test 4-2             | 2  |

| 4-2       | Self-Test Error Codes in the RX FIFO 4-4        | ł  |

| 4-3       | EVDAK Tests 4-7                                 | 7  |

| 4-4       | Ribbon Cable Signal Distribution 4-20           | )  |

# PREFACE

This document describes the installation, use, programming, and service requirements of the DMB32 asynchronous/synchronous multiplexer. It contains information for first-line service, field service support, and for customer engineers and programmers.

The manual is organized into four chapters plus an appendix.

| Chapter 1  |   | Introduction              |

|------------|---|---------------------------|

| Chapter 2  |   | Installation              |

| Chapter 3  | - | Operation and Programming |

| Chapter 4  | - | Troubleshooting           |

| Appendix A | - | Glossary                  |

The following is a list of related titles.

| Document                          | Number      |

|-----------------------------------|-------------|

| DMB32 Technical Description       | EK-DMB32-TD |

| DMB32 Field Maintenance Print Set | MP-01797-01 |

# CHAPTER 1 INTRODUCTION

## 1.1 SCOPE

This chapter describes the functions, versions, physical features, and specifications of the DMB32 communications adapter.

#### **1.2 OVERVIEW**

The DMB32 is an intelligent synchronous/asynchronous multiplexer which provides eight full-duplex asynchronous serial data channels, one synchronous data channel, and one line printer interface on VAXBI systems.

The main features of the DMB32 are:

- Single VAXBI module (T1012) and distribution panel (H3033)

- Eight full-duplex asynchronous (async) data channels

- One synchronous (sync) data channel

- One line-printer port. The DMB32 printer port supports the LP32 generic printer specification. This includes the LN01, LN01-B, LN01-S, LP25, LP26, LP27, LXY12, and LXY22 printers.

- Direct Memory Access (DMA) or single-character programmed transfers to and from host memory

- Onboard virtual-to-physical address translation allows the DMB32 to handle data buffers in their virtual address format

- Large 512-entry First-In First-Out (FIFO) buffer on the async channels, for received characters, dataset status changes, and diagnostic information

- Async ports are electrically and mechanically compliant with RS-232-C, and compatible with V.28/V.24 (T1012 is also compatible with RS-423-A, V.10, and X.26, but the H3033 is not, due to pin limitations on the 25-pin D-type connectors).

- The sync port is electrically and mechanically compliant with RS-232-C, RS-422-A/RS-449, V.11, X.27, and V.35, and compatible with RS-423-A/RS-449, V.28/V.24, V.10, and X.26.

- IBM Bisync, SDLC/HDLC, and DDCMP protocols are supported on the sync port. NRZI support is also provided.

- General Byte (GEN BYTE) protocol provides basic framing and data transfer facilities to implement other byte-oriented protocols on the sync channel

- Full-duplex point-to-point or auto-answer dial-up operation

- Programmable split-speed operation

- Total module throughput 21000 characters per second

- Automatic flow-control of transmitted and received data on the async channels

- Self-test diagnostics

- Programmable loopback modes and test facilities

- There are no switches on the module or the distribution panel. Each external cable for the sync channel is electrically coded to select a specific CCITT/EIA standard. Other line characteristics are set under program control.

Enough modem control is provided on all synchronous and asynchronous channels to allow auto-answer dial-up operation over the public switched telephone network (PSTN). The DMB32 can also be used for point-to-point operation over private lines. Modem control is implemented by software in the host.

An integral microprocessor releases the host from many of the data-handling tasks.

The DMB32 has an on-board self-test diagnostic that is executed independently of the host. Online and standalone diagnostics are also available.

Two yellow LEDs on the T1012 module give the GO/NOGO status of the option. The self-test also provides more detailed error and/or status information through the RX FIFO and some of the device registers.

## **1.3 FUNCTIONAL DESCRIPTION**

The DMB32 is a communications adapter of the VAXBI family. It has eight asynchronous channels, one synchronous channel, and a printer channel. The function of the DMB32 is to transfer data between a VAXBI node and the asynchronous, synchronous, and printer ports.

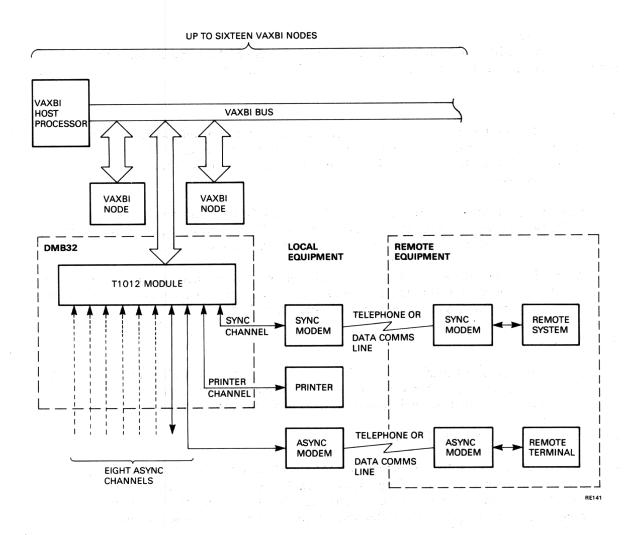

Figure 1-1 shows a DMB32 in a typical configuration.

. 이 사람은 이 가지 않는 것은 이 가지도 못했다. 한 이들과 이것이는 이러한 이것은 이 것은 것이 있는 것을 하는 것은 것을 하는 것 같은 것이 같은 것 같은 것은 것은 것은 것이 같은 것은 것은 것을 것을 것을 수 없다. 것을 것을 것을 수 있는 것이 있는 것을 하는 것이 같은 것이 같은 것이 같은 것이 같은 것이 같은 것이 있다.

Figure 1-1 DMB32 Typical Configuration

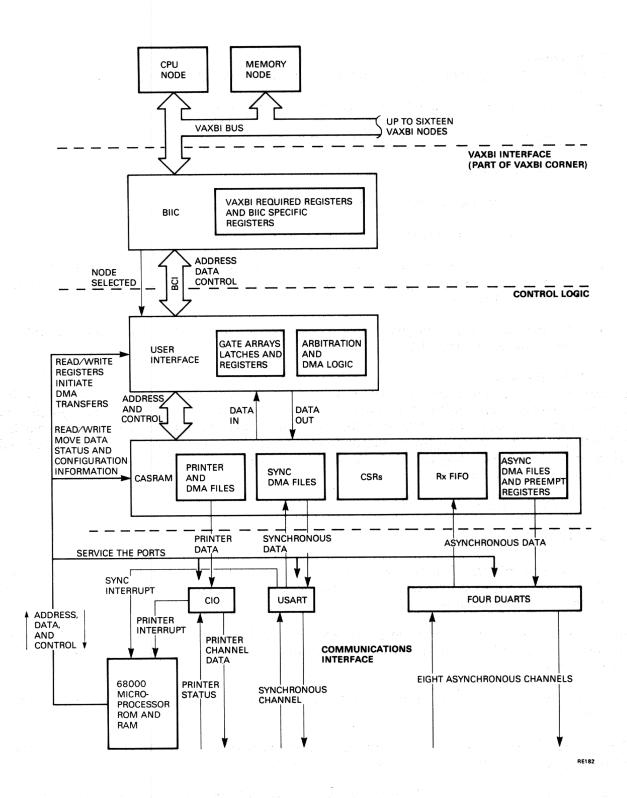

Figure 1-2 is a functional block diagram that shows the data routes through the option. Data is transferred between a VAXBI node on the host and the communications lines via registers and DMA files in the Common Address Store RAM (CASRAM). Also in the CASRAM are Control and Status Registers (CSRs) which configure and program the option. The information which is written to and read from the CSRs is used to support and control the communications functions.

Data can be transferred between the VAXBI and CASRAM by programmed Read or Write commands, or by the DMB32's DMA logic. Data is transferred between the communications interface and the CASRAM under the control of a 68000 microprocessor.

The maximum data transfer rate on the VAXBI is 13.3 Mbytes per second. Such a high rate makes the design of the VAXBI interface critical, so a standard VAXBI interface (VAXBI corner) has been designed for all VAXBI options. The VAXBI corner is based on a specially designed VAXBI integrated circuit (BIIC), which handles all the VAXBI commands and protocols.

The intelligence of the DMB32 is supplied by the 68000 microprocessor driven by ROM-based firmware. The microprocessor controls and configures the communications interface, and manages both DMA and communications functions. The firmware also includes self-test routines which run automatically at power-up or reset.

## **1.3.1** Data Transfer

The function of the DMB32 is to transfer data between the VAXBI host and the data lines connected to the communications interface. There are several methods of transfer.

• DMA

Sync RX and TX data is transferred between host memory buffers and CASRAM files by DMA. The microprocessor keeps track of the buffers, and initiates further DMA transfers as needed. Transfers between CASRAM and the sync port are initiated by an interrupt to the microprocessor.

Printer data is also transferred across the VAXBI by DMA. Transfers of data from CASRAM to the printer port are done by the microprocessor. Printer status is polled by the microprocessor, which also makes the status information available in the CSRs.

Async TX data can be transferred by DMA or by programmed transfer. DMA transfers to CASRAM are controlled in the same way as sync data transfers. The microprocessor monitors the async ports to check if they are ready to accept data.

RX FIFO

The microprocessor transfers async RX data to a 512-character RX FIFO in CASRAM. The host reads the data, together with error status information, from a single location (RBUF). The RX FIFO is also used to send diagnostic reports to the host.

• Programmed (Preempt) Transfer

Async TX data may be transferred to CASRAM by DMA, or it can be written to a singlecharacter 'preempt' register (one exists in each async channel). From there the transfer is completed by the microprocessor. A character written to the preempt register of a channel which is transmitting a DMA buffer will be transferred to the async port before any remaining DMA data.

Figure 1-2 DMB32 Functional Block Diagram

## 1.3.2 Interrupts

The DMB32 can be programmed to interrupt a VAXBI host under the following conditions.

- When a channel is ready for another preempt character

- When transfer of a DMA buffer from system memory to an I/O channel has:

- been aborted

- been terminated due to an error

- completed successfully

- When a received character has been placed in a previously empty RX FIFO (the DMB32 can be programmed to delay this interrupt so that several characters can be placed in the FIFO before "the interrupt is raised)

- When modem status information has been placed in the RX FIFO. This action overrides any programmed interrupt delay.

#### **1.3.3 Device Registers**

The DMB32 is a microprocessor-controlled device and consequently the host does not have to perform many data-handling tasks directly. The DMB32 appears to the host to be a set of device registers which can be loaded with commands or data to produce a certain action. When this action has been completed the DMB32 loads appropriate registers with status information. The completion of a task is signaled to the host either by an interrupt or by status information in a register that is polled by the host. Device registers can be considered in two groups.

- VAXBI registers

- DMB32 registers

**1.3.3.1** VAXBI Registers – Some of these registers must exist on any device (node) that is connected on the VAXBI. These "required" registers hold status and control information which defines how the DMB32 will respond to commands on the VAXBI.

Other VAXBI registers are not required by the VAXBI specification, but they support specific functions implemented by the BIIC. Features selected by the BIIC registers include the commands to be implemented by this node.

The VAXBI registers, which are all in the BIIC, are considered in detail in Chapter 3, Operation and Programming.

**1.3.3.2** DMB32 Registers – These are the registers through which the DMB32 specific features are controlled. They can be further subdivided into four groups.

- General registers Used to control parameters and functions common to all parts of the communications interface

- Async registers Used to control and monitor the async ports

- Sync registers Used to control and monitor the sync ports

- Printer registers Used to control and monitor the printer port

A register map, together with full details of all register functions, is given in Chapter 3, Operation and Programming.

## 1.4 PHYSICAL DESCRIPTION

#### 1.4.1 The DMB32 Option

The DMB32 option is made up of the following major items:

- A single VAXBI module (T1012)

- A distribution panel (H3033)

- Six ribbon cables (17-00740-xx, where xx defines the length)

- A 50-pin unbalanced loopback connector (H3195)

- A 50-pin balanced loopback connector (H3196)

- An async line loopback connector (H3197)

In addition to the above, the following adapter cables are available to match the synchronous channel connector (50-pin subminiature D-type) to the standard used by the connected equipment. Appropriate loopback connectors, not supplied with the option, are also indicated.

| Cable    | DIGITAL<br>Part Number | Standard      | Loopback<br>Connector |

|----------|------------------------|---------------|-----------------------|

| BC19F-02 | 17-01112-01            | V.35          | H3250                 |

| BC19D-02 | 17-01110-01            | V.24          | H3248                 |

| BC19B-02 | 17-01108-01            | <b>RS-422</b> | H3198                 |

| BC19E-02 | 17-01111-01            | RS-423-A      | H3198                 |

Details of the adapter cables and all loopback connectors are given in Chapter 2, Section 2.9.

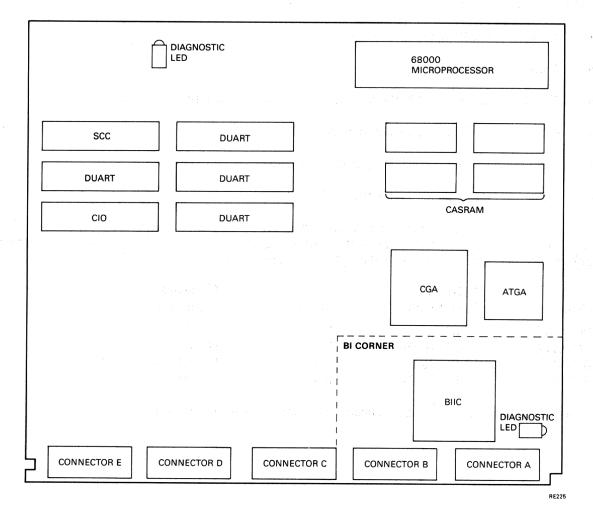

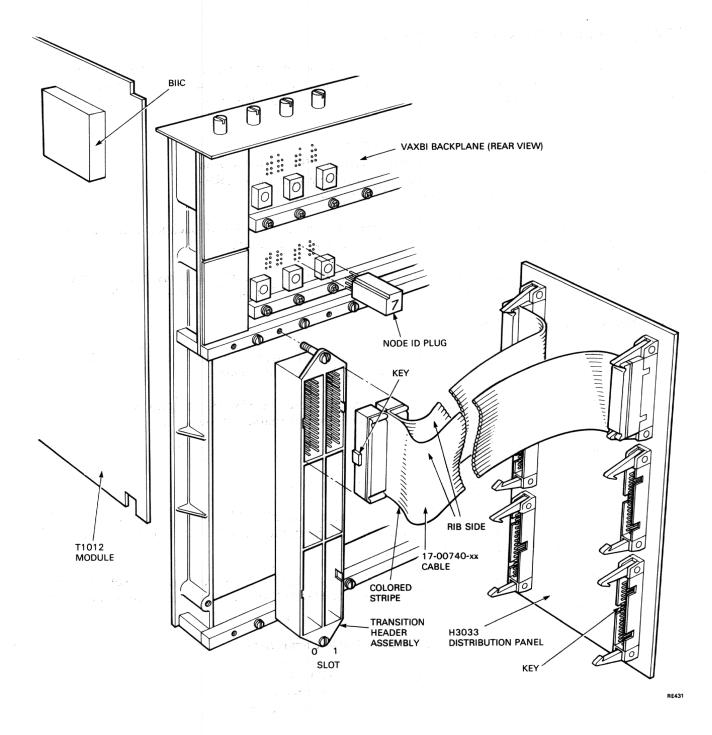

## 1.4.2 The T1012 Module

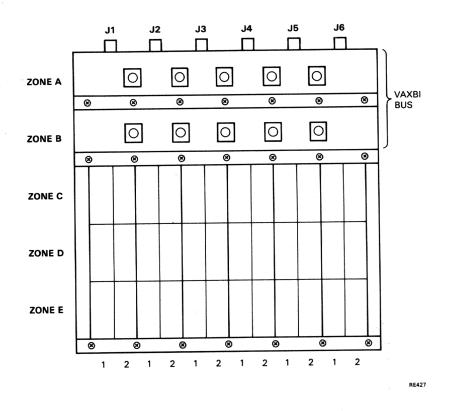

The DMB32 is based on a standard VAXBI-size module (T1012). The layout of this module is shown in Figure 1-3. The dimensions are 23.3 cm (9.18 in) by 20.3 cm (8.00 in).

The module is connected to the VAXBI via connector segments A and B. Connector segments C, D, and E are connected to the communications lines via the ribbon cables and the H3033 distribution panel.

The T1012 module connects directly to any slot (except number K1J1; see Chapter 2, Installation) in the VAXBI backplane. The bus address is determined by the 'Node ID' plug which is fitted to the back of the backplane (there are no switches on the module itself).

Figure 1-3 T1012 Module

## 1.4.3 The H3033 Distribution Panel

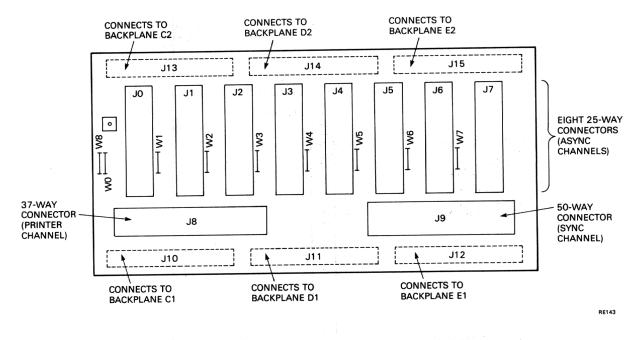

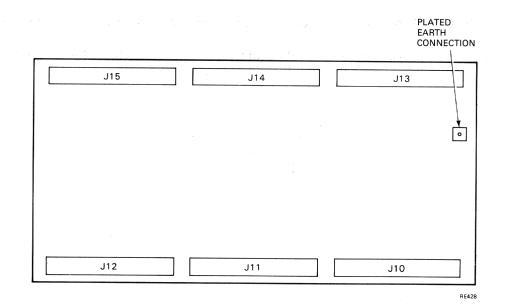

Figure 1-4 shows the H3033 distribution panel. This identifies the sync, async and printer connectors, and the connectors to which the ribbon cable headers are connected.

Figure 1-4 H3033 Distribution Panel

#### 1.4.4 Communications Interfaces

Electrically and mechanically, the T1012/H3033 async ports are:

- Compliant with RS-232-C •

- Compatible with V.28/V.24 •

The T1012 module is also compliant with RS-423-A, V.10, and X.26, but the H3033 is not, because of pin limitations on the 25-pin D-type connector.

Electrically and mechanically, the T1012/H3033 sync port is:

- Compliant with RS-232-C, RS-422-A/RS-449, V.11, X.27, and V.35

- Compatible with RS-423-A/RS-449, V.28/V.24, V.10, and X.26 •

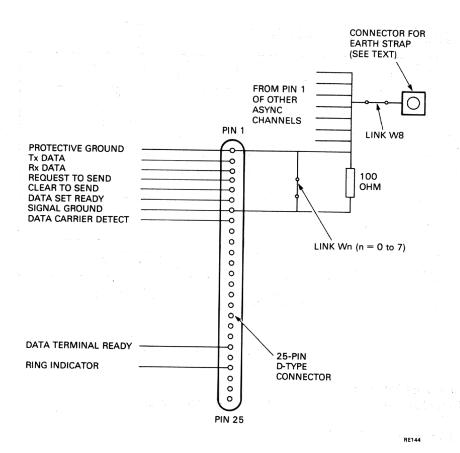

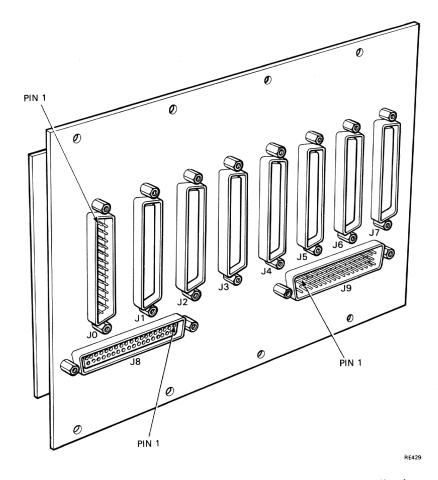

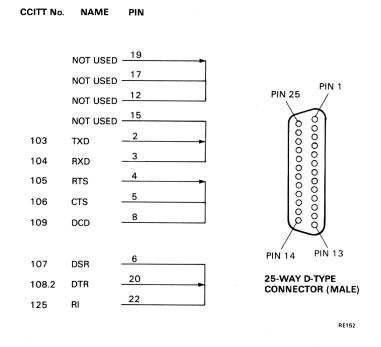

**1.4.4.1** Asynchronous Interface – Connection to external equipment, for each of the eight async interfaces, is made via a 25-pin subminiature D-type connector. Figure 1-5 shows the pin configuration of the connector.

Figure 1-5 J0 to J7 Async Connector Detail

As supplied by DIGITAL, each async connector has Signal Ground (pin 7) connected to Protective Ground (pin 1) by a resistor. Provision is made on the circuit board for a wire link to connect pin 7 directly to pin 1. There are places for eight such links designated W0 to W7.

The Protective Grounds of all eight channels are joined together, and are connected (via wire link W8) to a plated hole suitable for connection to a grounding strap. This allows the Protective Grounds to be connected to the chassis of the equipment in which the DMB32 is installed.

Table 1-1 shows the EIA/CCITT signal relationships and the pin connections for equivalent signals.

|         |                             |     | EIA I                                                                                                              | S 111 C                                              |     | CCIT            | Г V.24                                               |      |

|---------|-----------------------------|-----|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----|-----------------|------------------------------------------------------|------|

|         | RS-449<br>Name              | Pin |                                                                                                                    | RS-232-C<br>  Name                                   | Pin |                 | Name                                                 | Pir  |

| -       | Shield                      | 1   | AA                                                                                                                 | Protective Ground                                    | 1   | -               |                                                      | -    |

| -<br>SG | Signal Ground               | 19  | AB                                                                                                                 | Signal Ground                                        | 7   | 102             | Signal Ground                                        | 7    |

| SC      | Send Common                 | 37  | _                                                                                                                  |                                                      | _   | _               | -                                                    | -    |

| RC      | Receive Common              | 20  | _                                                                                                                  |                                                      | -   | _               |                                                      | _    |

| S       | Terminal In Service         | 36  | 1997 - Barry B<br> |                                                      | _   |                 |                                                      | _    |

| IC      | Incoming Call               | 15  | CE                                                                                                                 | Ring Indicator                                       | 22  | 125             | Calling Indicator                                    | 22   |

| TR      | Terminal Ready (+)          | 12  | CD                                                                                                                 | Data Terminal Ready                                  | 20  | 108/2           | Data Terminal Ready                                  | 20   |

| TR      | Terminal Ready (-)          | 30  | -                                                                                                                  | 2000 2000000000000000000000000000000000              | _   | _               |                                                      | -    |

| DM      | Data Mode (+)               | 1   | CC                                                                                                                 | Data Set Ready                                       | 6   | 107             | Data Set Ready                                       | 6    |

| DM      | Data Mode (-)               | 29  | -                                                                                                                  | 2                                                    | _   | _               |                                                      |      |

| SD      | Send Data (+)               | 4   | BA                                                                                                                 | Transmitted Data                                     | 2   | 103             | Transmitted Data                                     | 2    |

| SD      | Send Data (-)               | 22  | _                                                                                                                  |                                                      | _   | -               |                                                      | -    |

| RD      | Received Data (+)           | 6   | BB                                                                                                                 | Received Data                                        | 3   | 104             | Received Data                                        | 3    |

| RD      | Received Data (-)           | 6   | _                                                                                                                  |                                                      | _   |                 |                                                      | _    |

| TT      | Terminal Timing (+)         | 17  | DA                                                                                                                 | Transmitter Signal<br>Element Timing<br>(DTR Source) | 24  | 113             | Transmitter Signal<br>Element Timing<br>(DTR Source) |      |

| TT      | Terminal Timing (-)         | 35  | -                                                                                                                  |                                                      |     | 21 <del>-</del> |                                                      | -    |

| ST      | Send Timing (+)             | 5   | DB                                                                                                                 | Transmitter Signal<br>Element Timing<br>(DCE Source) | 15  | 114             | Transmitter Signal<br>Element Timing<br>(DCE Source) |      |

| ST      | Terminal Timing (-)         | 23  | -                                                                                                                  |                                                      | -   | _               |                                                      |      |

| RT      | Receive Timing (+)          | 8   | DD                                                                                                                 | Receiver Signal<br>Element Timing                    | 17  | 115             | Receiver Signa<br>Element Timing                     | 1 17 |

| RT      | Receive Timing (-)          | 26  | -                                                                                                                  |                                                      | -   |                 |                                                      |      |

| RS      | Request To Send (+)         | 7   | CA                                                                                                                 | Request To Send                                      | 4   | 105             | Request To Send                                      | 4    |

| RS      | Request To Send (-)         | 25  | -                                                                                                                  |                                                      | -   | _               |                                                      | -    |

| CS      | Clear To Send (+)           | 9   | CB                                                                                                                 | Clear To Send                                        | 5   | 106             | Clear To Send                                        | 5    |

| CS      | Clear To Send (-)           | 27  | -                                                                                                                  |                                                      |     | -               |                                                      | -    |

| RR      | Receiver Ready (+)          | 13  | CF                                                                                                                 | Received Line Signal<br>Detector                     | 8   | 109             | Data Channe<br>Received Line Signa<br>Detector       |      |

| RR      | Receiver Ready (-)          | 81  | . <b>-</b>                                                                                                         |                                                      | -   | -               |                                                      | -    |

| SQ      | Signal Quality              | 33  | CG                                                                                                                 | Signal Quality Detector                              | 21  | 110             | Data Signal Quality<br>Detector                      | y 21 |

| NS      | New Signal                  | 34  | -                                                                                                                  |                                                      | -   | ·               |                                                      | -    |

| SR      | Signaling Rate Selector     | 16  | СН                                                                                                                 | Data Signal Rate<br>Selector (DTE Source)            | 23  | 111             | Data Signaling Rat<br>Selector (DCI<br>Source)       |      |

| SI      | Signaling Rate<br>Indicator | 2   | CI                                                                                                                 | Data Signal Rate<br>Selector (DCE Source)            | 23  | _               |                                                      | -    |

| LL      | Local Loopback              | 10  |                                                                                                                    |                                                      | ·   | 141             | Local Loopback                                       | 1    |

| RL      | Remote Loopback             | 14  |                                                                                                                    |                                                      | -   | 140             | Remote Loopback                                      | 2    |

| ТМ      | Test Mode                   | 18  | -                                                                                                                  |                                                      | -   | 142             | Test Indicator                                       | 2    |

# Table 1-1 EIA/CCITT Signal Relationships

1

.

.

\_\_\_\_

|    | RS-449<br>al Name | Pin | EIA RS-232-C<br>Signal Name | Pin | CCITT V.24<br>Signal Name | Pin                     |

|----|-------------------|-----|-----------------------------|-----|---------------------------|-------------------------|

| SS | Select Standby    | 32  | _                           | -   |                           |                         |

| SB | Standby Indicator | 36  | -                           |     | <u> </u>                  | · · · · · · · · · · · · |

Table 1-1 EIA/CCITT Signal Relationships (continued)

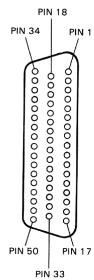

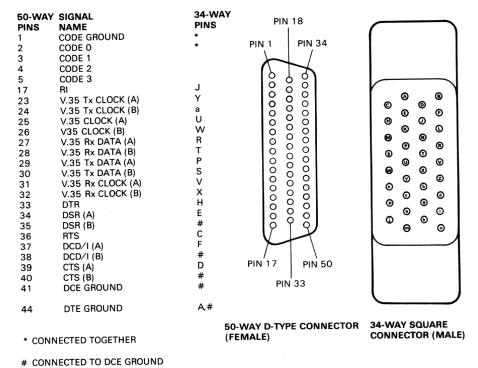

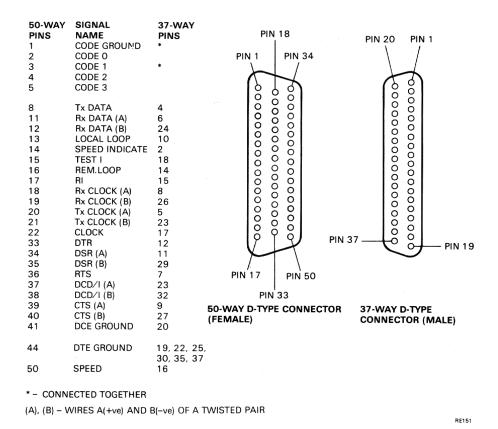

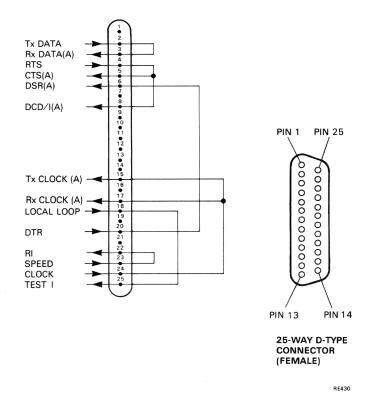

**1.4.4.2** The Synchronous Interface – Connection to external equipment is made via a 50-pin subminiature D-type connector. Figure 1-6 shows the pin configuration of the connector. Different adapter cables are used to select only those signals needed to implement a specific interface standard. These adapter cables are fully described in Chapter 2, Section 2.8, Cabling.

| 50-WAY<br>PIN | SIGNAL<br>NAME    |     |      |

|---------------|-------------------|-----|------|

| 1             | CODE GROUND       |     |      |

| 2             | CODE 0            |     |      |

| 3             | CODE 1            |     |      |

| 4             | CODE 2            |     |      |

| 5             | CODE 3            |     |      |

| 6             | Tx DATA (A)       |     |      |

| 7             | Tx DATA (B)       |     |      |

| 8             | Tx DATA           |     |      |

| 9             | RTS/C (A)         |     |      |

| 10            | RTS/C (B)         |     |      |

| 11            | Rx DATA (A)       |     |      |

| 12            | Rx DATA (B)       |     |      |

| 13            | LOCAL LOOP        |     |      |

| 14            | SPEED INDICATE    |     |      |

| 15            | TEST I            |     |      |

| 16            | REM.LOOP          |     |      |

| 17            | RI                |     |      |

| 18            | Rx CLOCK (A)      |     |      |

| 19            | Rx CLOCK (B)      |     |      |

| 20            | Tx CLOCK (A)      |     |      |

| 21            | Tx CLOCK (B)      |     |      |

| 22            | CLOCK             |     |      |

| 23            | V.35 Tx CLOCK (A) |     |      |

| 24            | V.35 Tx CLOCK (B) |     |      |

| 25            | V.35 CLOCK (A)    |     |      |

| 26            | V.35 CLOCK (B)    |     |      |

| 27            | V.35 Rx DATA (A)  |     |      |

| 28            | V.35 Rx DATA (B)  |     |      |

| 29            | V.35 Tx DATA (A)  |     |      |

| 30            | V.35 Tx DATA (B)  |     |      |

| 31            | V.35 Rx CLOCK (A) |     |      |

| 32            | V.35 Rx CLOCK (B) |     |      |

| 33            | DTR               |     |      |

| 34            | DSR (A)           |     |      |

| 35            | DSR (B)           |     |      |

| 36            | RTS               |     |      |

| 37            | DCD/I (A)         |     |      |

| 38            | DCD/1 (B)         | 50  | 0-W  |

| 39            | CTS (A)           | ( N | VIAL |

| 40            | CTS (B)           | •   |      |

| 41            | DCE GROUND        |     |      |

| 42            | TEST 1            |     |      |

| 43            | TEST 2            |     |      |

| 44            | DTE GROUND        |     |      |

| 45            | DTR (A)           |     |      |

| 46            | DTR (B)           |     |      |

| 47            | CLOCK (A)         |     |      |

| 48            | CLOCK (B)         |     |      |

| 49            | TEST 3            |     |      |

| 50            | SPEED             |     |      |

|               |                   |     |      |

50-WAY D-TYPE CONNECTOR (MALE PLUG)

RE146

(A).(B) WIRES A(+ve) AND B(-ve) OF A TWISTED PAIR

Figure 1-6 Sync Connector Detail

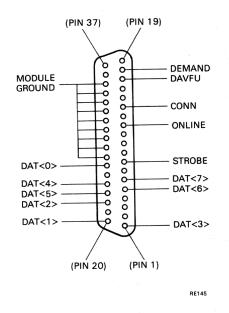

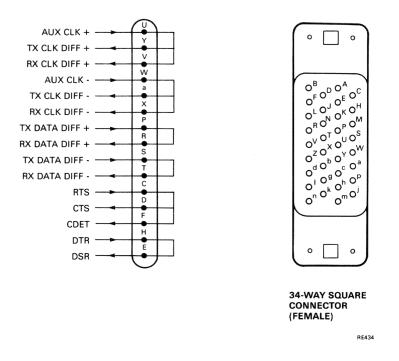

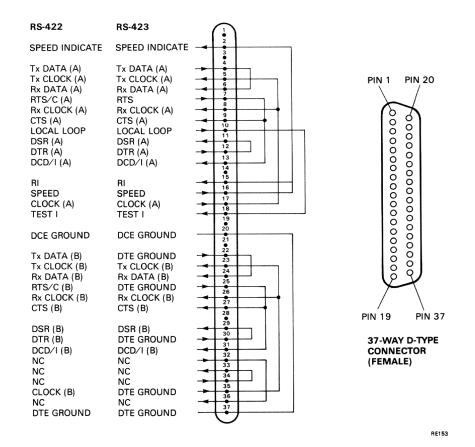

**1.4.4.3** The Printer Interface – The printer port is a parallel interface at TTL levels. Connection to the printer is made via a 37-pin subminiature D-type connector. Figure 1-7 shows the pin configuration of the connector.

The T1012/H3033 line printer port supports the LP32 generic printer specification. This includes the LN01, LN01-B, LN01-S, LP25, LP26, LP27, LXY12, and LXY22 printers.

Figure 1-7 Printer Connector Detail

# **1.5 SPECIFICATIONS**

# 1.5.1 Electrical Requirements

+5 V dc + or - 5% at 6.75 A +12 V dc + or - 3% at 300 mA -12 V dc + or - 3% at 425 mA

#### **1.5.2 Functional Parameters**

**1.5.2.1** Synchronous Functional Parameters – Table 1-2 lists the functional parameters for the synchronous line of the DMB32.

| Parameter           | Description                                                         |

|---------------------|---------------------------------------------------------------------|

| DMA transfer        | Double buffered                                                     |

| Protocols supported | DDCMP, SDLC, HDLC, IBM BISYNC, GEN BYTE                             |

| Data rates (bits/s) | 600, 1200, 1800, 2000, 2400, 4800, 9600, 19200, 48000, 56000, 64000 |

| Table 1-2 Synchronous Functional Paramete | Table | e 1-2 | Synchronous | Functional | Parameter |

|-------------------------------------------|-------|-------|-------------|------------|-----------|

|-------------------------------------------|-------|-------|-------------|------------|-----------|

**1.5.2.2** Asynchronous Functional Parameters – Table 1-3 lists the functional parameters for the asynchronous line of the DMB32.

| Parameter           | Description                                                                                                                                                                                                                                                                 |                                                      |  |  |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--|--|--|--|

|                     | Description                                                                                                                                                                                                                                                                 |                                                      |  |  |  |  |

| Operating mode      | Full-duplex or half-duplex*                                                                                                                                                                                                                                                 |                                                      |  |  |  |  |

| Data format         | One start bit; 1, 1.5, or 2 stop bits                                                                                                                                                                                                                                       |                                                      |  |  |  |  |

| Character size      | 5, 6, 7, or 8 bits (Does not include the                                                                                                                                                                                                                                    | 5, 6, 7, or 8 bits (Does not include the parity bit) |  |  |  |  |

| Parity              | Odd, even or no parity                                                                                                                                                                                                                                                      |                                                      |  |  |  |  |

| Data rates (bits/s) | 50, 75, 110, 134.5, 150, 300, 600, 1800, 2000, 2400, 4800, 7200, 9600, 19200, 38400                                                                                                                                                                                         |                                                      |  |  |  |  |

| Split-speed         | When using split-speed operation the transmit and receive speeds of bor<br>channels sharing a DUART must be in the same group (A or B). Channel<br>are paired (use the same DUART) as follows: channels 0 and 1, 2 and 3,<br>and 5, 6 and 7. Speeds are grouped as follows: |                                                      |  |  |  |  |

|                     | Speeds (bits/s)                                                                                                                                                                                                                                                             | Group                                                |  |  |  |  |

|                     | 50, 7200, 38400                                                                                                                                                                                                                                                             | Α                                                    |  |  |  |  |

|                     | 75, 150, 1800 2000, 19200                                                                                                                                                                                                                                                   | В                                                    |  |  |  |  |

|                     | 110, 134.5, 300, 600, 1200, 2400, 4800, 9600                                                                                                                                                                                                                                | A and B                                              |  |  |  |  |

| Table 1-3 | Asyncl | hronous | Functional | F | Parameters |

|-----------|--------|---------|------------|---|------------|

|-----------|--------|---------|------------|---|------------|

\* Half-duplex is only supported on systems using coded link-control as the DMB32 does not support the secondary transmit and receive signals.

**1.5.2.3** Printer Port Functional Parameters – Table 1-4 lists the functional parameters for the printer port of the DMB32.

| Parameter               | Description                                                                          |                                                                                             |

|-------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

|                         |                                                                                      |                                                                                             |

| Formatting capabilities | Prefix characters, suffix of<br>lower-case to upper-case<br>tracking, line truncate. | characters, CR insertion, FF to LF conversion, conversion, line wrapping, carriage position |

| Table 1-4 | Printer | Port | Functional | Parameters |

|-----------|---------|------|------------|------------|

|-----------|---------|------|------------|------------|

**1.5.2.4** Throughput – Each asynchronous channel is capable of full-duplex operation at data rates of up to 38400 bits/s. However, the DMB32 cannot support eight channels operating at 38400 bits/s at the same time. The total maximum throughput of the DMB32 is around 21000 characters per second (eight data bits with start and one stop bit), including all characters transmitted and received on the synchronous line and the printer port.

If congestion occurs, the DMB32 will give priority to the synchronous line, followed by the reception of async characters.

The individual maximum througputs for each port are:

- Sync 16000 char/s

- Async 10000 char/s

- Printer 4000 chars/s (equivalent to 1800 lines/min)

The maximum sensible speed that can be used on the sync port depends on the protocol and electrical interface standard selected. Table 1-5 lists the maximum sensible speeds for all the supported protocols.

|          |        | Electrical I  | nterface Standa | rd    |           |

|----------|--------|---------------|-----------------|-------|-----------|

| Protocol | RS-232 | <b>RS-423</b> | RS-422          | V.35  |           |

| DDCMP    | 19200  | 19200         | 19200           | 19200 | Data rate |

| HDLC     | 19200  | 64000         | 64000           | 48000 | (Bits/s)  |

| BISYNC   | 9600   | 9600          | 9600            | 9600  |           |

| GEN BYTE | 9600   | 9600          | 9600            | 9600  |           |

Table 1-5

Maximum Sensible Speeds (Sync Port)

# 1.5.3 Environmental Specifications

#### 1.5.3.1 Operating Environment

- Temperature: 5°C to 50°C (41°F to 122°F)

- Relative humidity: 10% to 95% non-condensing, with a maximum wet bulb of 32°C (90°F) and a minimum dew point of 2°C (36°F)

- Altitude: Up to 2.4 km (8000 feet)

# 1.5.3.2 Storage Environment

- Temperature:  $-40^{\circ}$ C to  $66^{\circ}$ C ( $-40^{\circ}$ F to  $151^{\circ}$ F)

- Relative Humidity: Up to 95% non-condensing

- Altitude: Up to 9.0 km (30000 feet)

and the second second

and the second second

しんしん あいえん したて ないしん かんかいかん しんし 新設す

e de la companya de l La companya de la comp

# CHAPTER 2 INSTALLATION

#### 2.1 SCOPE

The procedures for installing and testing the DMB32 option are described in this chapter.

#### WARNING

The procedures described in this chapter involve the removal of the system covers, and should be performed only by trained personnel.

#### CAUTION

You must wear an anti-static wrist strap connected to an active ground whenever you work on a system with the covers removed, or handle the T1012 module.

The T1012 module is supplied in protective antistatic packaging. Do not remove the module from its packaging until you are about to install it.

#### NOTE

The complete equipment and documentation should be present before installation begins. Any missing items must be identified and the discrepancy corrected.

## 2.2 INSTALLATION TASK LIST

The installation of the DMB32 consists of a number of steps:

- Unpacking and inspection (see Section 2.4)

- Installation checks (Section 2.5)

- VAXBI Configuration checks (Section 2.6)

- Installing the T1012 module (Section 2.7.2)

- Installing the transition header assembly on the VAXBI backplane (Section 2.7.3)

- Installing the ribbon cables into the transition header (Section 2.7.4)

- Installing the H3033 distribution panel and ribbon cables (Section 2.7.5)

- Installing the external adapter cables (Sections 2.7.5 and 2.9)

- Installation testing (Section 2.8)

# 2.3 SITE PLANNING

No special site planning is required for the DMB32 option. Your System documentation will define any site-planning considerations. The environmental conditions required by the DMB32 option are specified in Chapter 1, Section 1.5.3.

# 2.4 DMB32 INSTALLATION KITS

The DMB32 option is supplied in a kit that contains the parts needed to install the option, but you may also need the torque wrench (29-17381-00) from the VAXBI installation kit. Check the contents of your DMB32 installation kit against the list given in this section. Examine all parts for physical damage. Report damaged or missing items to the shipper immediately, and inform the local DIGITAL office.

### CAUTION

The T1012 module is supplied in protective antistatic packaging. Do not remove the module from its packaging unless you are wearing an anti-static wrist strap.

There are three different versions of the installation kit, tailored to three different system configurations. These are:

- DMB32-LJ for the VAX-8800 and VAX-8500 systems

- DMB32-LM for the VAX-8200 and VAX-8300 systems

- DMB32-LN for the VAX-8800 system with an expander cabinet

The only difference between the three versions is the length of the six ribbon cables that go between the VAXBI backplane and the H3033 distribution panel. The contents of the three kits are given in Table 2-1.

| Part Number | Description                    | DMB32-LJ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -LM                             | -LN      |

|-------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------|

| T1012       | DMB32 module                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                               | 1        |

| H3033       | Distribution panel             | i al <b>1</b> e al 1 al                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                               | 1 .<br>1 |

| 12-22246-01 | Transition header assembly     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                               | 1        |

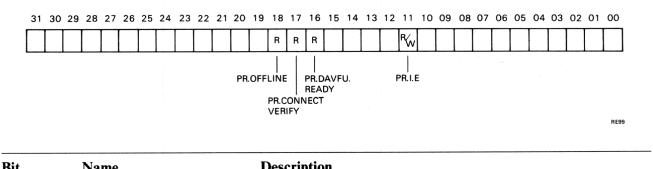

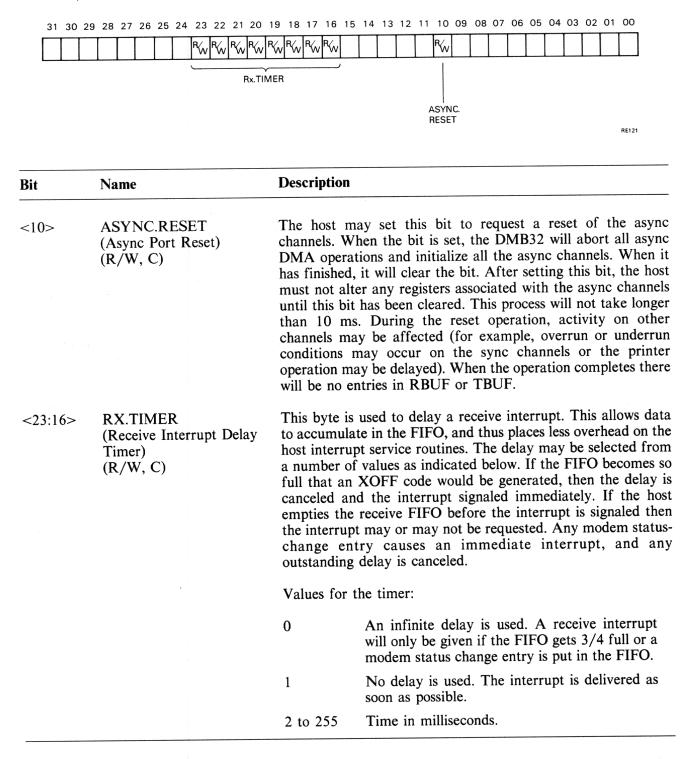

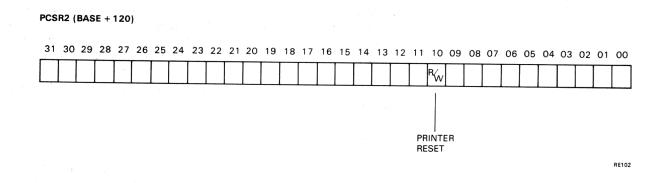

| 17-00740-02 | 5 ft ribbon cable assembly     | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                               | 0        |