EK-DMB32-TD-001

## DMB32 Technical Description

EK-DMB32-TD-001

# DMB32 Technical Description

Prepared by Educational Services of Digital Equipment Corporation

#### Copyright © 1986 by Digital Equipment Corporation

#### All Rights Reserved

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

Using Digital's networked computer systems, this book was produced electronically by the Media, Publishing and Design Services department in Reading, England.

#### Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation.

DEC DECmate DECUS DECwriter DIBOL MASSBUS PDP P/OS Professional Rainbow RSTS RSX RT UNIBUS VAX VMS VT Work Processor

#### **CONTENTS**

#### **CHAPTER** 1 **GENERAL DESCRIPTION**

| 1.1       | SCOPE                                          | 1-1 |

|-----------|------------------------------------------------|-----|

| 1.2       | GENERAL OVERVIEW                               | 1-1 |

| 1.2.1     | Communications Interface                       | 1-3 |

| 1.2.2     | Control Logic                                  | 1-3 |

| 1.2.2.1   | Common Address Store RAM (CASRAM)              | 1-3 |

| 1.2.2.2   | User Interface                                 | 1-3 |

| 1.2.3     | VAXBI Interface                                | 1-3 |

| 1.2.4     | Registers                                      | 1-3 |

| 1.2.4.1   | VAXBI Required Registers                       | 1-3 |

| 1.2.4.2   | BIIC Specific Registers                        | 1-3 |

| 1.2.4.3   | User Registers                                 | 1-4 |

| 1.2.5     | Types of Data Transfer                         | 1-4 |

| 1.2.5.1   | DMA Transfer                                   | 1-4 |

| 1.2.5.2   | Programmed (RX FIFO) Asynchronous Reception    | 1-4 |

| 1.2.5.3   | Programmed (Preempt) Asynchronous Transmission | 1-4 |

| 1.2.6     | Interrupts to the Host                         | 1-5 |

| 1.3       | HARDWARE OVERVIEW                              | 1-5 |

| 1.3.1     | VAXBI Interface (BIIC)                         | 1-5 |

| 1.3.2     | User Interface                                 | 1-5 |

| 1.3.2.1   | Data Paths                                     | 1-5 |

| 1.3.2.2   | Busmux                                         | 1-5 |

| 1.3.2.3   | CASRAM                                         | 1-5 |

| 1.3.2.4   | Address Translation Gate Array (ATGA)          | 1-5 |

| 1.3.2.5   | Control Gate Array (CGA)                       | 1-7 |

| 1.3.3     | Communications Interface                       | 1-7 |

| 1.3.3.1   | Microprocessor                                 | 1-7 |

| 1.3.3.2   | Asynchronous Ports                             | 1-7 |

| 1.3.3.3   | Synchronous Port                               | 1-7 |

| 1.3.3.4   | Printer Port (Parallel Port)                   | 1-7 |

| 1.3.3.5   | Line Drivers and Receivers                     |     |

| 1.4       | DATA ROUTING                                   |     |

| CHAPTER 2 | FUNCTIONAL DESCRIPTION                         |     |

| CHAFTER 2 | FUNCTIONAL DESCRIPTION                         |     |

| 2.1       | SCOPE                                          | 2-1 |

| 2.2       | OVERVIEW                                       | 2-1 |

| 2.2.1     | DMA Operation                                  | 2-1 |

| 2.2.2     | VAX-11 Address Translation                     | 2-2 |

| 2.2.2.1   | Address of Buffer                              | 2-2 |

| 2.2.2.2   | Physical Address of Page Table                 | 2-2 |

| 2.2.2.3   | System Virtual Address of Buffer               | 2-2 |

| 2.2.2.4   | System Virtual Address of Process Page Table   | 2-3 |

| 2.2.3     | Interrupts                                     | 2-3 |

| 2.2.4     | Synchronous Operation                          | 2-4 |

| 2.2.4.1   | Synchronous Transmit Full DMA File Queue       | 2-5 |

| 2.2.4.2   | Synchronous Transmit Done DMA File Queue       | 2-5 |

| 2.2.4.3   | Synchronous Receive Empty DMA File Queue       | 2-5 |

| 2.2.4.4   | Synchronous Receive Full DMA File Queue        | 2-5 |

|           |                                                |     |

| 2.2.4.5 | Synchronous Buffer Translate Queue | 2-5  |

|---------|------------------------------------|------|

| 2.2.4.6 | Further Information                | 2-5  |

| 2.3     |                                    | 2-6  |

|         |                                    | 2-6  |

| 2.4     | MODEM CONTROL (SYNC PORT)          |      |

| 2.4.1   | Modem Control Signals              | 2-6  |

| 2.5     | PROTOCOL SUPPORT (SYNC PORT)       | 2-8  |

| 2.6     | HDLC/SDLC SUPPORT (SYNC PORT)      | 2-8  |

| 2.6.1   | Message Definition                 | 2-8  |

| 2.6.2   | Block Check                        | 2-8  |

| 2.6.3   | Character Size                     | 2-9  |

| 2.6.4   | Address Bytes                      | 2-9  |

| 2.6.5   |                                    | 2-9  |

| 2.7     |                                    | 2-9  |

| 2.7.1   | Message Definition                 |      |

| 2.7.1.1 | SYNSEQ                             |      |

| 2.7.2   | Start of Message (SOM)             |      |

|         |                                    |      |

| 2.7.2.1 | COUNT                              |      |

| 2.7.2.2 | QSYNC                              |      |

| 2.7.2.3 | SELECT 2                           |      |

| 2.7.2.4 | CONTROL                            |      |

| 2.7.2.5 | ADDR                               | 2-11 |

| 2.7.2.6 | CRCI                               | 2-11 |

| 2.7.2.7 | DATA 2                             | 2-11 |

| 2.7.2.8 | CRC2                               | 2-11 |

| 2.7.2.9 | PAD                                |      |

| 2.7.3   | Character Size                     |      |

| 2.7.4   | Aborting Transmission              |      |

| 2.8     | IBM BISYNC SUPPORT (SYNC PORT)     |      |

| 2.8.1   | Message Definition                 |      |

| 2.8.1.1 | Transparent Mode                   |      |

| 2.8.1.2 | Block Check                        |      |

| 2.8.1.2 | Insert SYNC Characters             |      |

|         |                                    |      |

| 2.8.1.4 | PAD Characters                     |      |

| 2.8.1.5 | Character Sets                     |      |

| 2.8.1.6 | ASCII Character Set                |      |

| 2.8.1.7 | EBCDIC Character Set 2             |      |

| 2.8.1.7 | Aborting a Transmission 2          | 2-15 |

| 2.9     | GENERAL BYTE SUPPORT (SYNC PORT) 2 | 2-15 |

| 2.9.1   | General Description 2              |      |

| 2.9.1.1 | Received Data 2                    |      |

| 2.9.1.2 | Character Size 2                   | 2-15 |

| 2.9.1.3 | Block Check 2                      | 2-16 |

| 2.9.1.4 | Aborting a Message 2               | 2-16 |

| 2.10    | ASYNCHRONOUS INTERFACE 2           |      |

| 2.10.1  | Speeds 2                           | 2-17 |

| 2.10.2  | Speed Selection                    |      |

| 2.10.3  | Performance                        |      |

| 2.11    | DATA TRANSFERS (ASYNCHRONOUS PORT) | 2-18 |

| 2.11.1  | Receive Data                       |      |

| 2.11.2  | Transmit Data                      |      |

| 2.11.2  | Interrupts                         |      |

| 2.11.3  | Modem Control                      |      |

| 2.11.4  | Protective Ground                  |      |

| 4.II.J  |                                    | -4U  |

| 2.11.6    | Auto XON/XOFF Operation                      | 2-20 |  |  |  |

|-----------|----------------------------------------------|------|--|--|--|

| 2.11.7    | Received XON/XOFF Characters                 | 2-21 |  |  |  |

| 2.11.8    | Transmitted XON/XOFF Characters              |      |  |  |  |

| 2.12      | PRINTER INTERFACE                            |      |  |  |  |

| 2.12.1    | Operation                                    |      |  |  |  |

| 2.12.2    | Formatting                                   | 2-22 |  |  |  |

| CHAPTER 3 | TECHNICAL DESCRIPTION                        |      |  |  |  |

| 3.1       | SCOPE                                        | 3-1  |  |  |  |

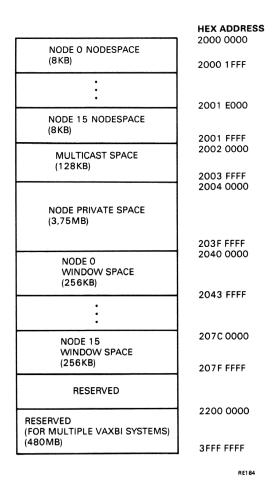

| 3.2       | MEMORY MAPS                                  | 3-1  |  |  |  |

| 3.3       | DMB32 COMMANDS                               | 3-5  |  |  |  |

| 3.3.1     | DMB32 Slave Response/Interpretation          | 3-5  |  |  |  |

| 3.3.2     | DMB32 Master Commands                        | 3-6  |  |  |  |

| 3.4       | VAXBI CORNER                                 |      |  |  |  |

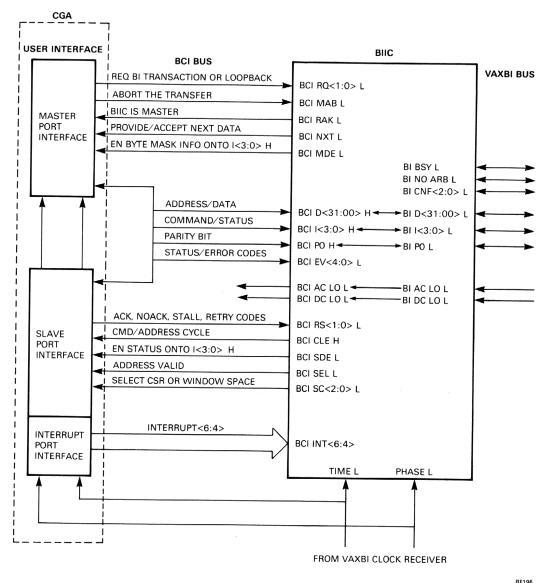

| 3.4.1     | Backplane Interconnect Interface Chip (BIIC) |      |  |  |  |

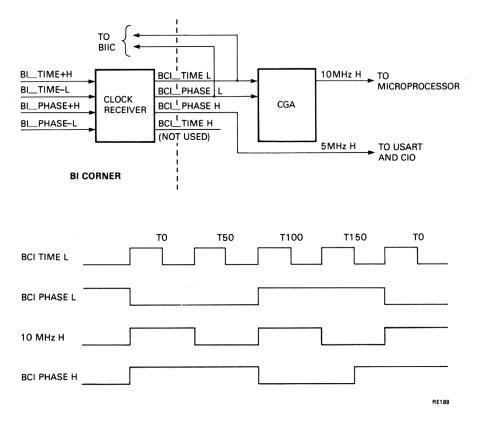

| 3.4.2     | Clock Circuits                               | 3-7  |  |  |  |

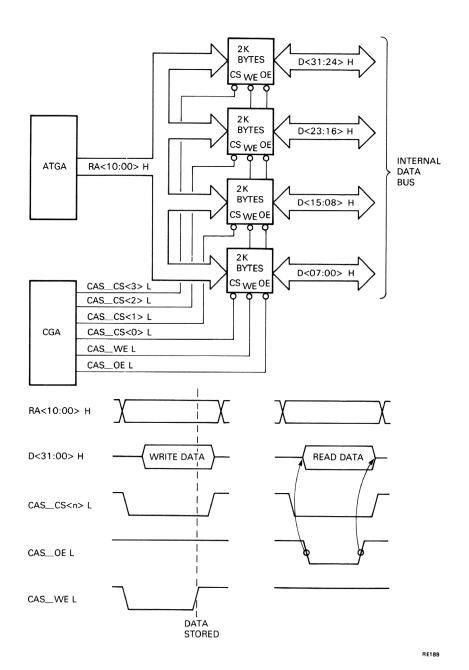

| 3.5       | COMMON ADDRESS STORE RAM (CASRAM)            | 3-8  |  |  |  |

| 3.6       | ADDRESS TRANSLATION GATE ARRAY (ATGA)        | 3-8  |  |  |  |

| 3.6.1     | Address Translation                          | 3-8  |  |  |  |

| 3.6.1.1   | Indexing                                     | 3-8  |  |  |  |

| 3.6.1.2   | FIFO Controllers                             |      |  |  |  |

| 3.6.1.3   | Inversion of Microprocessor Addresses        |      |  |  |  |

| 3.6.2     | ATGA Registers                               |      |  |  |  |

| 3.7       | CONTROL GATE ARRAY (CGA)                     |      |  |  |  |

| 3.8       | DATA PATHS                                   | 3-11 |  |  |  |

| 3.9       | 68000 BUS MULTIPLEXER                        | 3-12 |  |  |  |

| 3.10      | 68000 MICROPROCESSOR                         |      |  |  |  |

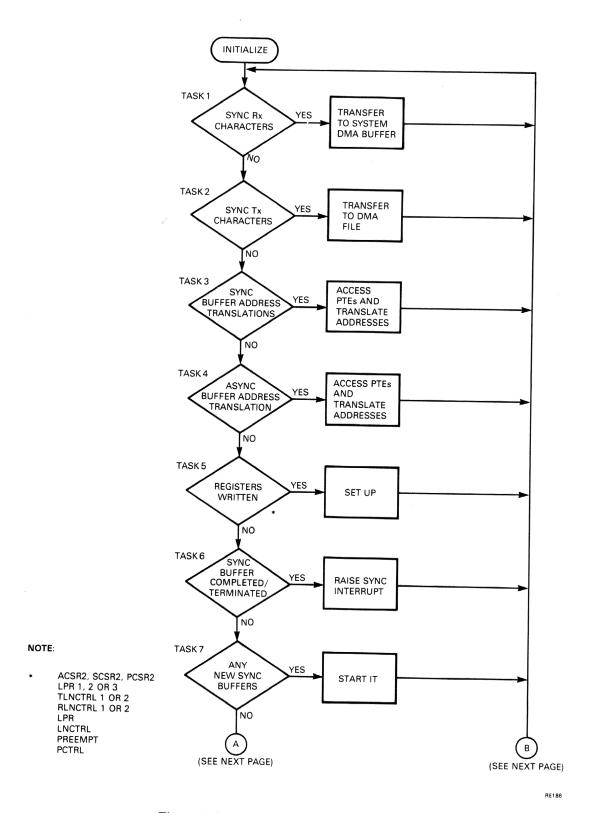

| 3.11      | FIRMWARE FLOW                                |      |  |  |  |

| 3.12      | ASYNCHRONOUS PORTS                           |      |  |  |  |

| 3.13      | SYNCHRONOUS PORT                             | 3-17 |  |  |  |

| 3.14      | PRINTER PORT AND DISCRETE I/O                | 3-19 |  |  |  |

| 3.15      | OUTPUT/TTL LEVEL CONVERSION                  |      |  |  |  |

| 3.16      | COMMUNICATIONS INTERFACE                     |      |  |  |  |

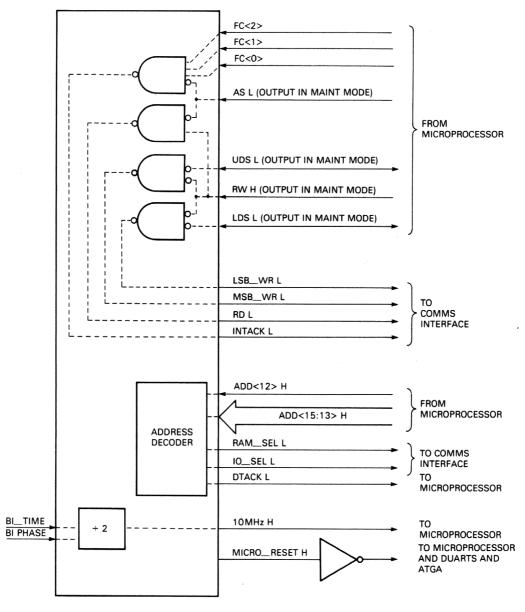

| 3.16.1    | Address and Signal Decoding                  |      |  |  |  |

| 3.17      | BCI INTERFACE                                |      |  |  |  |

| 3.17.1    | DMB32 Slave Transactions                     |      |  |  |  |

| 3.17.1.1  | Slave Read Transaction                       |      |  |  |  |

| 3.17.1.2  | Slave Write Transaction                      |      |  |  |  |

| 3.17.1.3  | IDENT Transaction                            |      |  |  |  |

| 3.17.1.4  | Maintenance Levels                           |      |  |  |  |

| 3.17.2    | DMB32 Master Transaction                     |      |  |  |  |

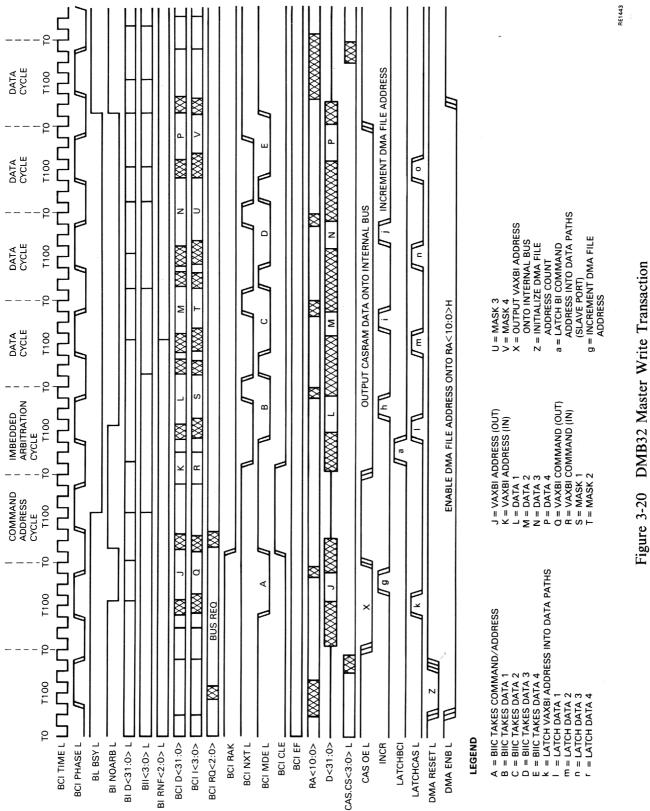

| 3.17.2.1  | Master Write Transaction                     | 3-36 |  |  |  |

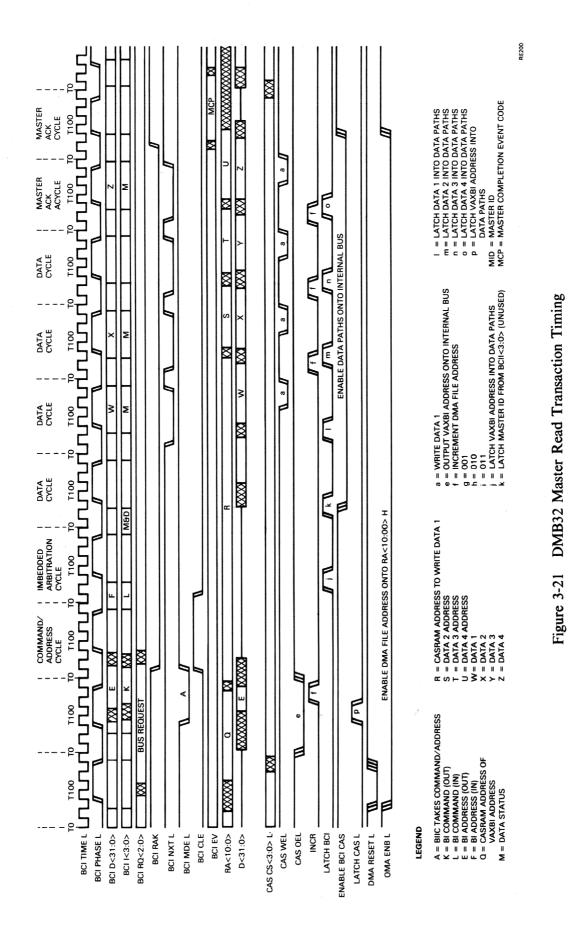

| 3.17.2.2  | Master Read Transaction                      |      |  |  |  |

| 3.17.3    | Loopback Transactions.                       |      |  |  |  |

| 3.17.4    | VAXBI INTR Transactions.                     | 3-38 |  |  |  |

| 3.18      | OVERALL CONTROL LOGIC OPERATION AND TIMING   |      |  |  |  |

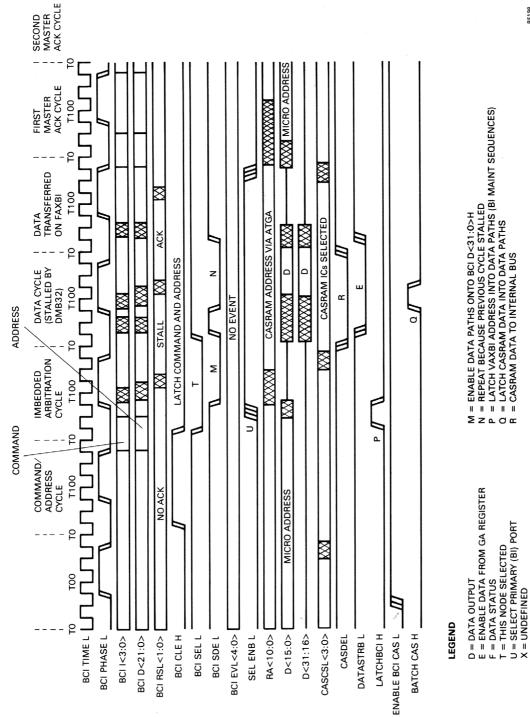

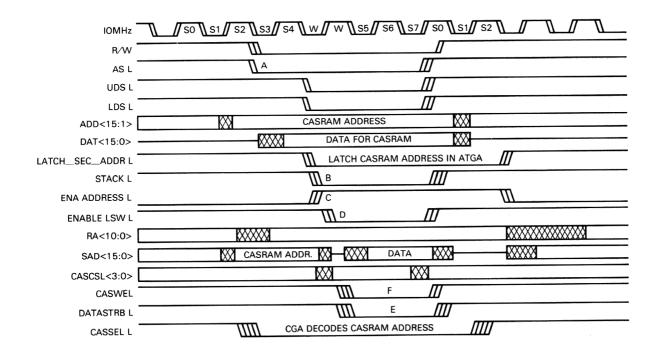

| 3.18.1    | Microprocessor Write to CASRAM               | 3-40 |  |  |  |

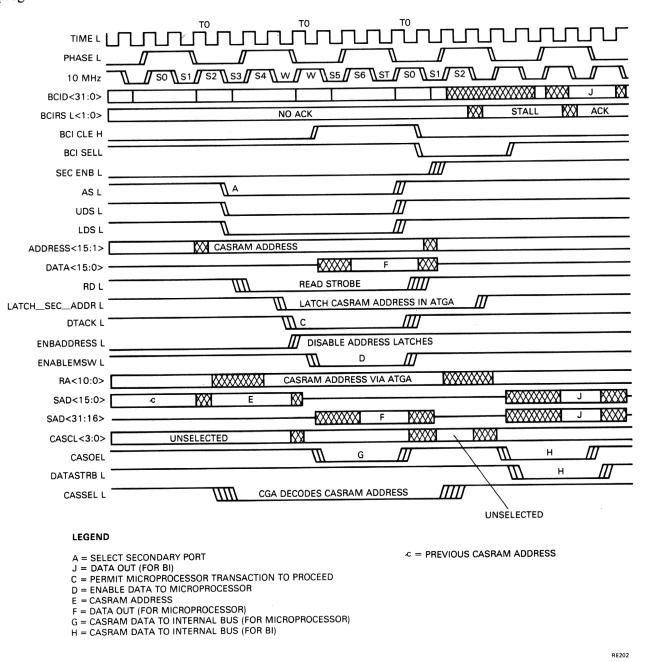

| 3.18.2    | Microprocessor Read from CASRAM              | 3-41 |  |  |  |

v

#### APPENDIX A IC DESCRIPTIONS

| A.1     | SCOPE                                   | A-1   |

|---------|-----------------------------------------|-------|

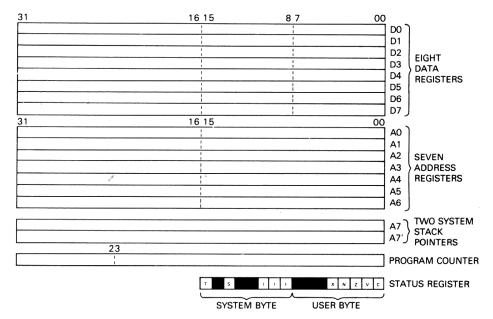

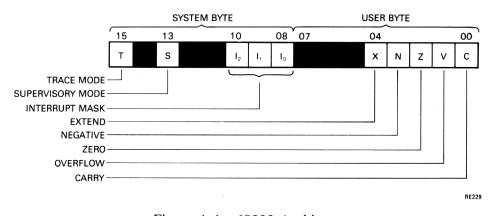

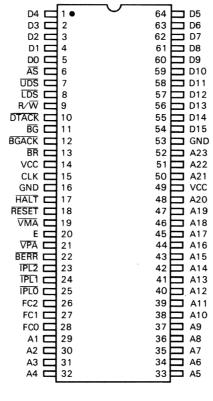

| A.2     | 68000 MICROPROCESSOR                    | . A-1 |

| A.2.1   | Overview                                |       |

| A.2.2   | Signals and Pinout                      | . A-2 |

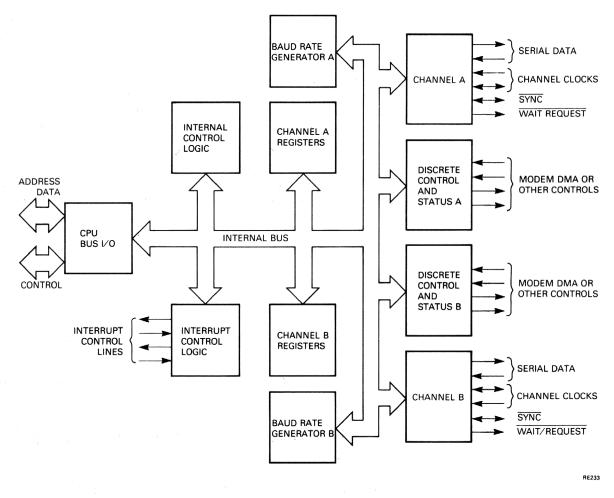

| A.3     | 8530 UNIVERSAL SYNCHRONOUS/ASYNCHRONOUS |       |

|         | RECEIVER/TRANSMITTER                    | A-5   |

| A.3.1   | Overview                                | A-5   |

| A.3.2   | Signals and Pinout                      | A-8   |

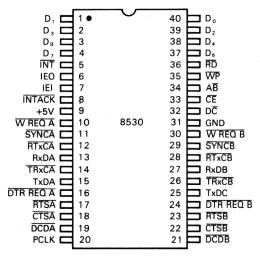

| A.4     | 8536 COUNTER/TIMER                      | A-10  |

| A.4.1   | Overview                                | A-10  |

| A.4.1.1 | The CPU Interface                       |       |

| A.4.1.2 | I/O Ports                               |       |

| A.4.1.3 | Counter/Timers                          | A-11  |

| A.4.1.4 | Interrupts                              | A-11  |

| A.4.1.5 | Register Selection                      | A-12  |

| A.4.2   | Signal and Pinout                       | A-14  |

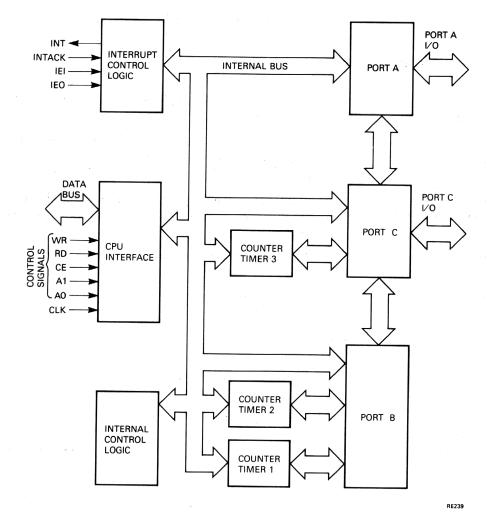

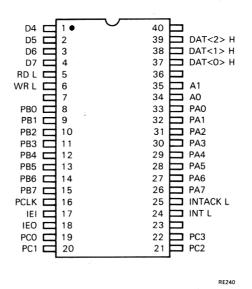

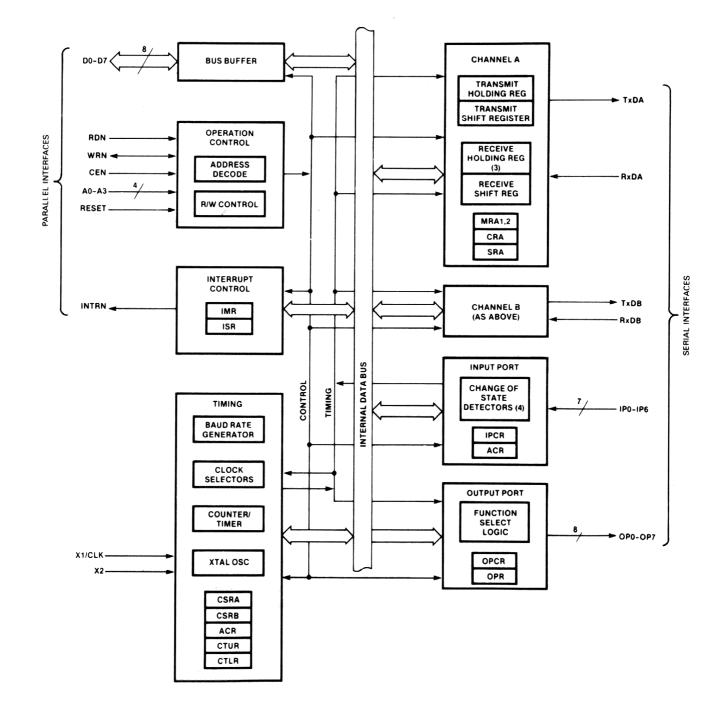

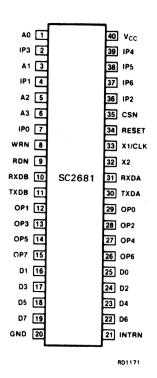

| A.5     | 2681 DUART                              | A-15  |

| A.5.1   | Overview                                |       |

| A.5.2   | Signals and Pinout                      |       |

#### APPENDIX B GATE ARRAYS

| B.1     | OVERVIEW                              | B-1        |

|---------|---------------------------------------|------------|

| B.2     | ADDRESS TRANSLATION GATE ARRAY (ATGA) | B-1        |

| B.2.1   | Scope                                 | B-1        |

| B.2.2   | Derivation Of CASRAM Addresses        | B-1        |

| B.2.3   | ATGA Register Overview                | B-4        |

| B.2.4   | SIGNAL DESCRIPTIONS                   | B-5        |

| B.3     | CONTROL GATE ARRAY (CGA)              | <b>B-8</b> |

| B.3.1   | Scope                                 | <b>B-8</b> |

| B.3.1.1 | Overview                              | B-9        |

| B.3.2   | CGA Register Overview                 | B-9        |

| B.3.3   | Signal Descriptions                   | B-11       |

|         |                                       |            |

#### APPENDIX C GLOSSARY

#### FIGURES

| Figure No. | Title                                         | Page |

|------------|-----------------------------------------------|------|

| 1-1        | DMB32 Functional Block Diagram                | 1-2  |

| 1-2        | Hardware Overview Diagram                     | 1-6  |

| 3-1        | DMB32 Overview Diagram                        |      |

| 3-2        | VAXBI I/O Address Space                       |      |

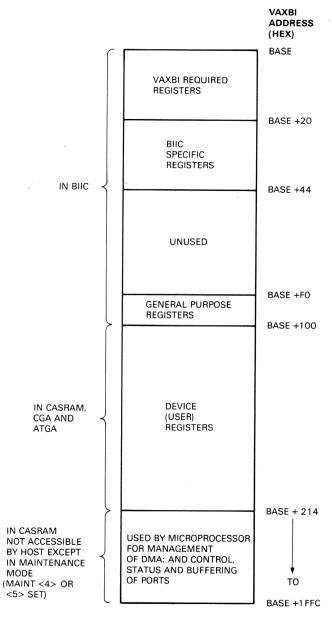

| 3-3        | DMB32 Memory Map.                             |      |

| 3-4        | DMB32 Clock Circuits                          |      |

| 3-5        | CASRAM Block Diagram                          |      |

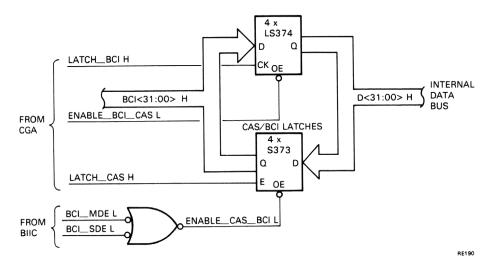

| 3-6        | Data Paths Logic                              |      |

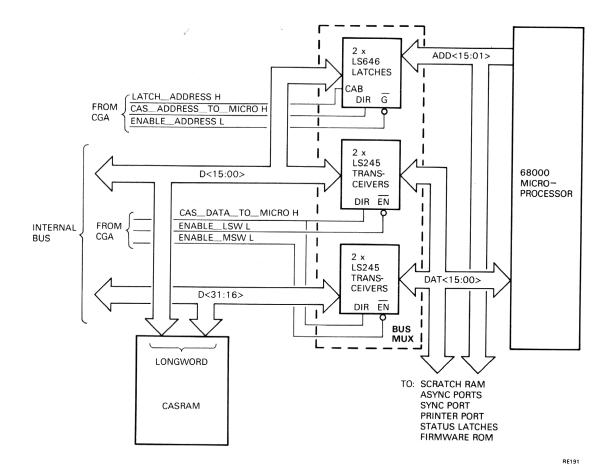

| 3-7        | Multiplexing the 68000 Microprocessor Bus     |      |

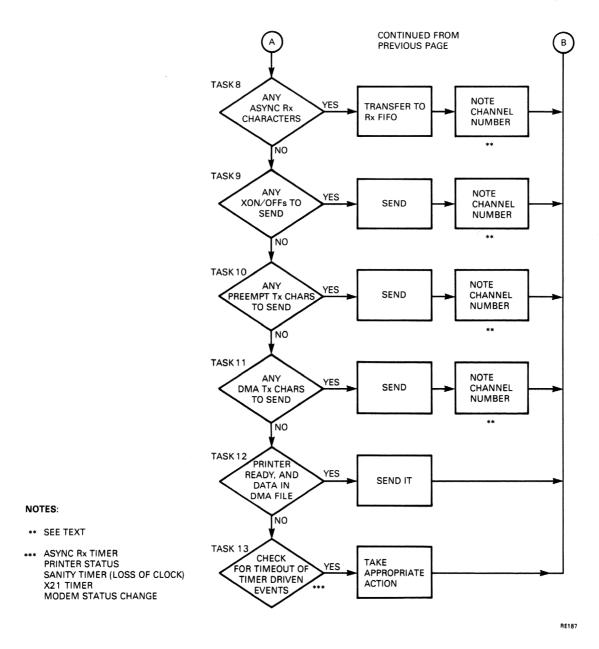

| 3-8        | DMB32 Firmware Flow Diagram                   |      |

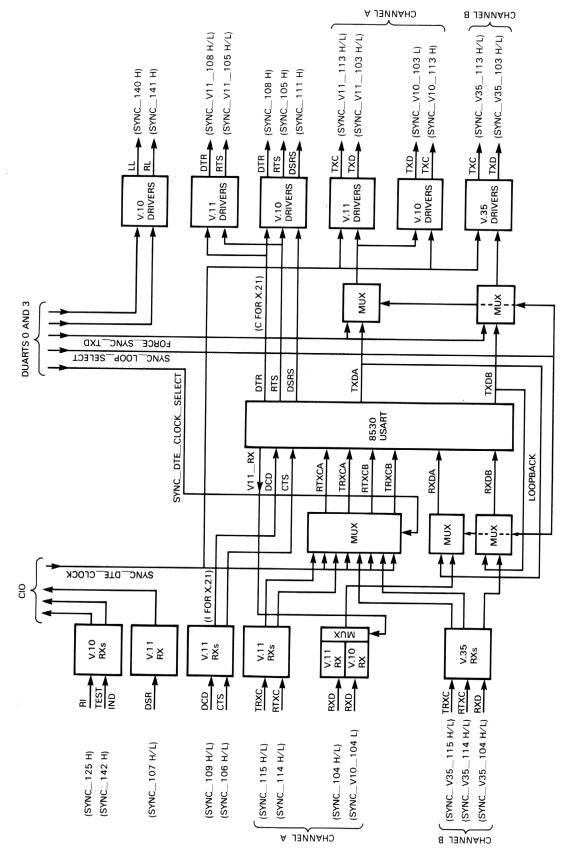

| 3-9        | Control of Sync Channel Drivers and Receivers |      |

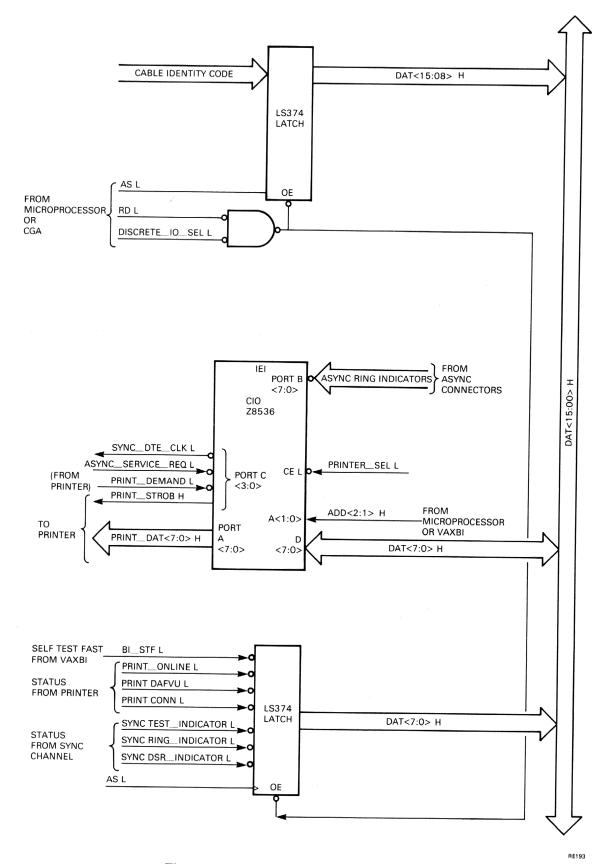

| 3-10       | Printer Port and Discrete Logic               |      |

| Figure No.  | Title                                                 | Page |

|-------------|-------------------------------------------------------|------|

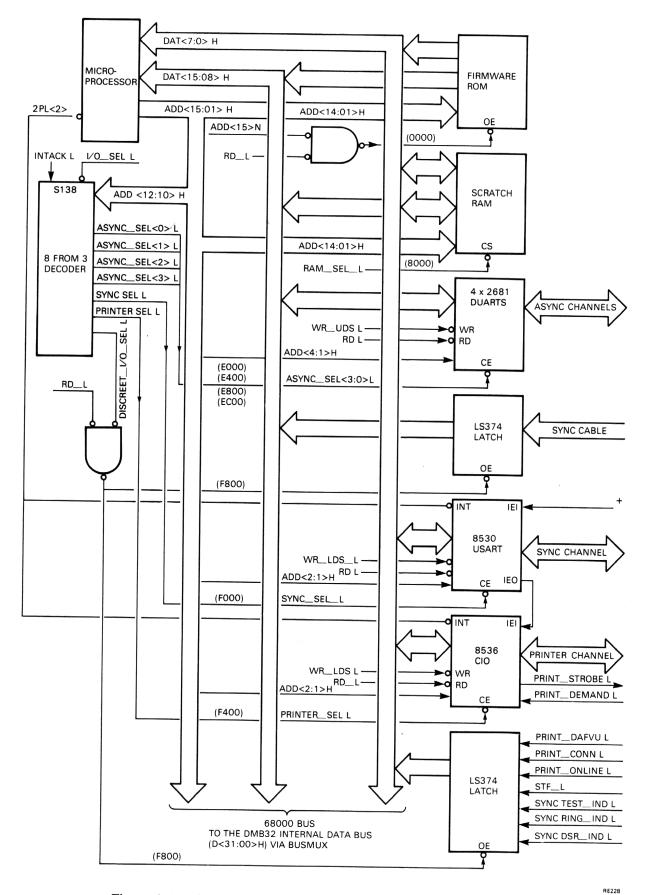

| 3-11        | Data Bus Arrangement — Communications Interface       | 3-22 |

| 3-12        | 68000 Microprocessor Bus Address and Signal Decoding  | 3-23 |

| 3-13        | DMB32 BCI Interface                                   |      |

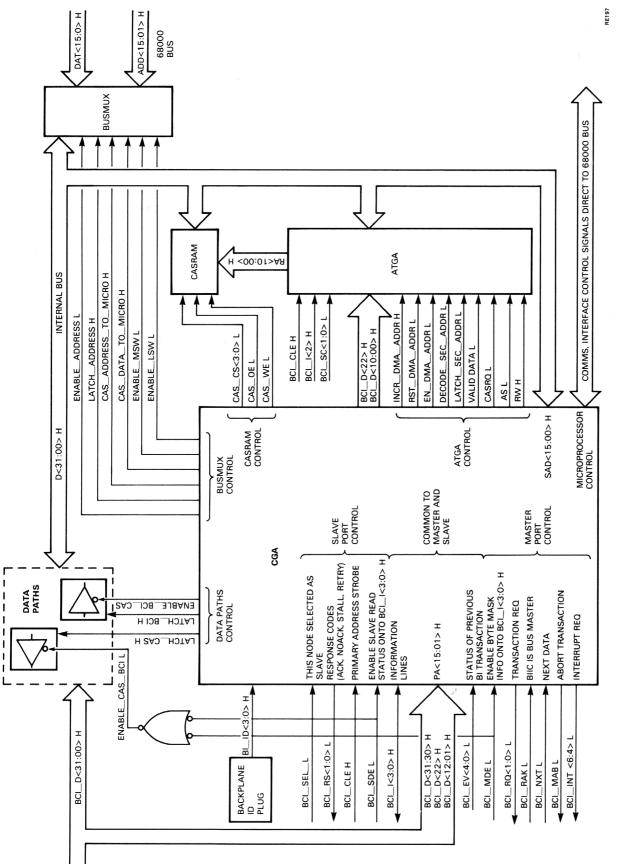

| 3-14        | Control and BCI Interface Logic                       |      |

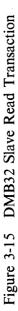

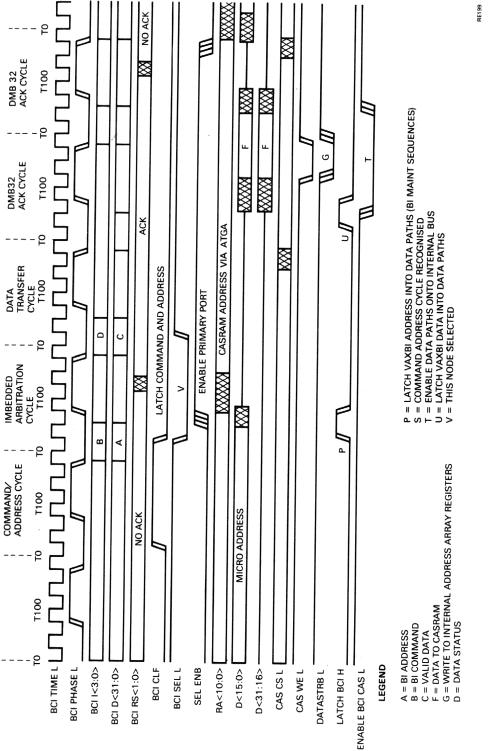

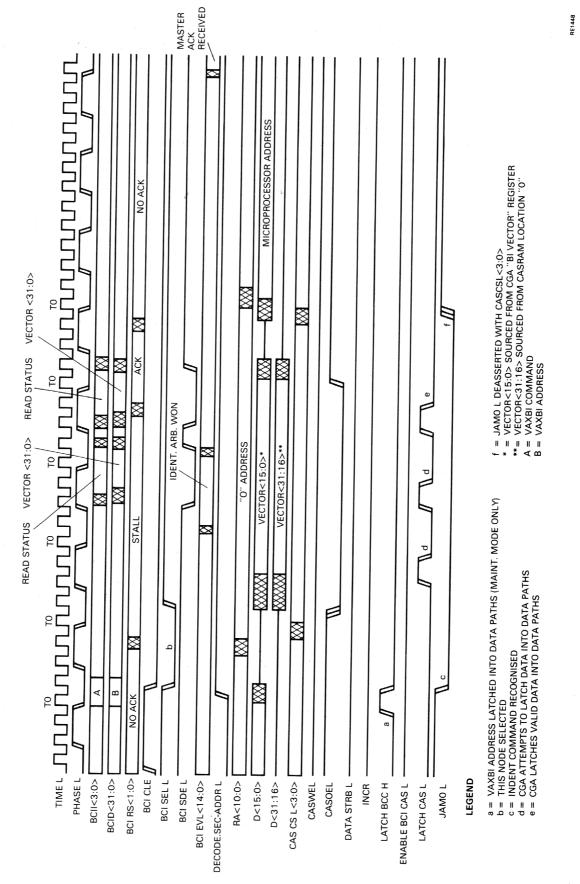

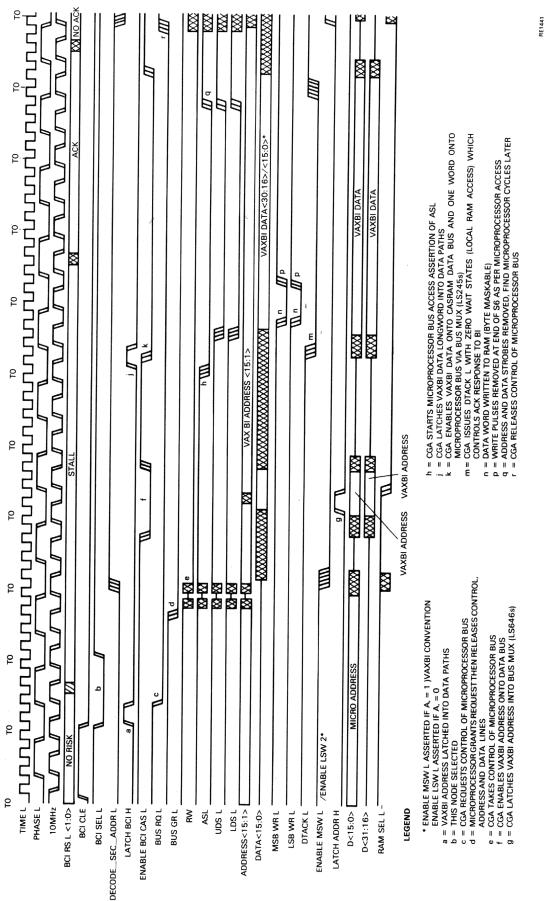

| 3-15        | DMB32 Slave Read Transaction                          | 3-29 |

| 3-16        | DMB32 Slave Write Transaction                         |      |

| 3-17        | VAXBI IDENT Transaction                               | 3-32 |

| 3-18        | VAXBI Window Space Write to Microprocessor I/O Space  | 3-34 |

| 3-19        | VAXBI Window Space Read from Microprocessor RAM       | 3-35 |

| 3-20        | DMB32 Master Write Transaction                        | 3-37 |

| 3-21        | DMB32 Master Read Transaction Timing                  |      |

| 3-22        | Busmux Write Transaction Timing                       | 3-41 |

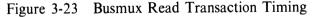

| 3-23        | Busmux Read Transaction Timing                        | 3-42 |

| A-1         | 68000 Architecture                                    |      |

| A-2         | 68000 Input/Output Signals                            | A-3  |

| A-3         | 68000 Pinout                                          | A-3  |

| A-4         | 8530 Architecture                                     | A-6  |

| A-5         | 8530 Register Summary                                 | A-7  |

| A-6         | 8530 Pinout                                           | A-8  |

| <b>A-</b> 7 | CIO Architecture                                      |      |

| A-8         | CIO Pinout Details                                    | A-14 |

| A-9         | 2681 Dual Universal Asynchronous Receiver Transmitter | A-16 |

| A-10        | 2681 Pinout Diagram                                   | A-17 |

| B-1         | ATGA Pinout Diagram                                   | B-2  |

| B-2         | Representation of Address Translation Functions       | B-3  |

| B-3         | CGA Pinout Diagram                                    | B-8  |

#### TABLES

| Table No. | Title                                    | Page |

|-----------|------------------------------------------|------|

| 2-1       | Maximum Sensible Speeds (Sync Port)      | 2-6  |

| 2-2       | Synchronous Interchange Circuits         | 2-7  |

| 2-3       | Supported Speeds (Async Port)            |      |

| 2-4       | Redefinition of Conflicting Speeds       |      |

| 2-5       | Asynchronous Interchange Circuits        |      |

| 3-1       | Address Latch Truth Table                |      |

| 3-2       | CGA Decoding of Microprocessor Addresses |      |

| 3-3       | DMB32 Response to VAXBI Commands         |      |

| A-1       | 68000 Signal Descriptions                |      |

| A-2       | 8530 Signal Descriptions                 |      |

| A-3       | Counter/Timer External Access            |      |

| A-4       | CIO Register Selection                   |      |

| A-5       | 8536 Registers                           |      |

| A-6       | 8536 Signal Description                  |      |

| A-7       | 2681 Signal Description                  |      |

| B-1       | ATGA Register Map                        |      |

| B-2       | ATGA Signal Descriptions                 |      |

| B-3       | CGA Register Map                         |      |

| B-4       | CGA Signal Descriptions                  |      |

#### vii

#### Page

#### PREFACE

This document gives a functional and technical description of the DMB32 asynchronous/synchronous multiplexer. It contains information for field service support, and for anyone who needs to know, in detail, how the DMB32 works.

The manual is organized into three chapters plus appendixes.

Chapter 1- General DescriptionChapter 2- Functional DescriptionChapter 3- Technical DescriptionAppendix A- IC DescriptionsAppendix B- Gate ArraysAppendix C- Glossary of Terms

The following is a list of related titles.

**Document** DMB32 User Guide DMB32 Field Maintenance Print Set **Number** EK-DMB32-UG MP-01797-01

•

### CHAPTER 1 GENERAL DESCRIPTION

#### 1.1 SCOPE

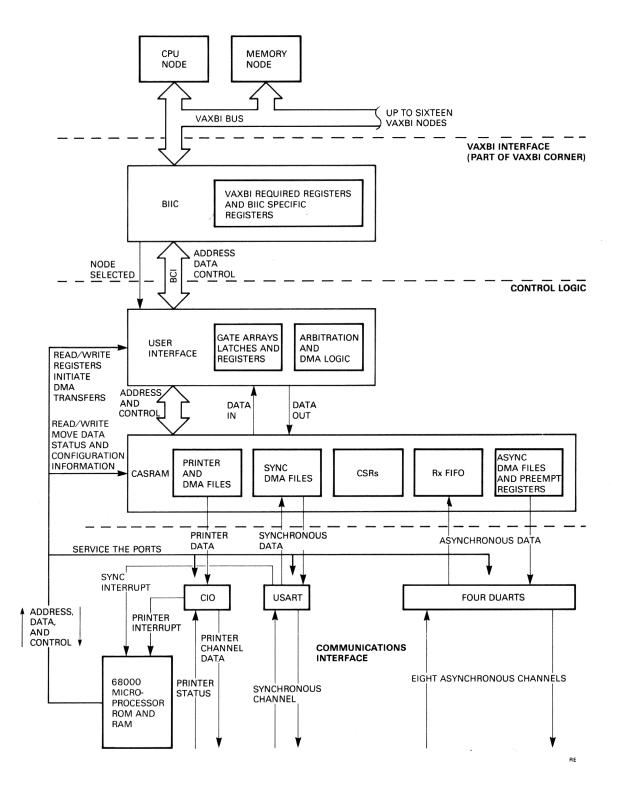

Chapter 1 provides a general description of the main functions of the DMB32 module. This is followed by a hardware overview section which provides more information on the functions of the on-board devices. Two supporting block diagrams are included as an aid to understanding the descriptions.

#### **1.2 GENERAL OVERVIEW**

The DMB32 is an intelligent communications adapter for the VAXBI. The primary function of the DMB32 is to transfer data between its communications ports and other VAXBI nodes, by the methods described later in this chapter. The DMB32 communications ports consist of:

- One synchronous port handling data at up to 64 Kbits per second.

- Eight asynchronous ports each handling data asynchronously at up to 38.4 Kbits per second.

- One parallel printer port handling up to 1200 lines per minute.

The VAXBI host needs only to make a DMA buffer available, and to program the CSRs, as described in the *DMB32 Users Guide*. All other tasks are carried out by the firmware-driven on-board microprocessor which performs and manages all configuration and data transfer functions and instructs the relevant logic to do whatever tasks are required. The microprocessor will initiate and manage DMA transfers and will ensure that the selected communications interface protocols are observed.

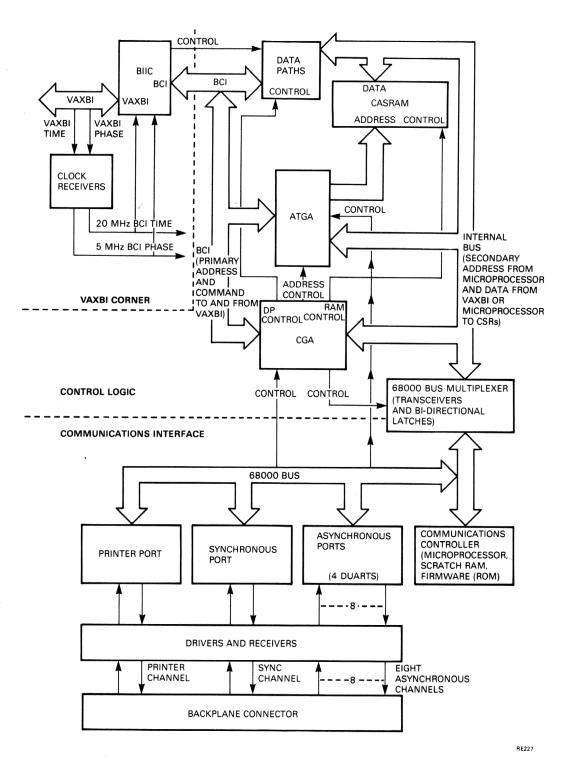

Figure 1-1 shows a simplified block diagram of the DMB32 in which the three main functional areas are identified as follows:

- 1. Communications Interface

- 2. Control Logic

- 3. VAXBI Interface

Data flow is also indicated on Figure 1-1.

Figure 1-1 DMB32 Functional Block Diagram

#### **1.2.1** Communications Interface

This consists of the asynchronous, synchronous, and printer ports under the control of a 68000 microprocessor. The microprocessor has firmware ROM and dedicated scratch RAM. It controls the VAXBI Interface by a combination of interrupts and polling.

#### 1.2.2 Control Logic

For explanatory purposes, this can be subdivided into two areas of operation:

- 1. Common Address Store RAM (CASRAM)

- 2. User Interface

**1.2.2.1** Common Address Store RAM (CASRAM) – CASRAM is accessed by the VAXBI host, or by the on-board microprocessor. It contains data buffer areas and most of the CSRs used by the DMB32.

**1.2.2.2** User Interface – The interface between the BIIC and the user functions will be called the User Interface in this manual, to conform with the VAXBI generic documentation. Gate arrays in this block contain most of the DMB32 logic, and one of the arrays arbitrates between host and microprocessor access to CASRAM.

The User Interface can respond as slave to commands passed on by the BIIC, or as bus master it can request VAXBI transfers. VAXBI transfer requests are made to the BIIC, which arbitrates for the bus and then controls the transfer.

#### **1.2.3 VAXBI Interface**

Handling of VAXBI protocol, parity, and the recognition of commands and addresses are all performed by a VAXBI interface chip (BIIC) on the VAXBI Interface. Valid commands addressed to this node are passed to the User Interface which can then respond via the BIIC, as bus slave. The BIIC contains registers whose functions are described in Section 1.2.4.

#### 1.2.4 Registers

The device registers (CSRs) are mapped into CASRAM; however, some are in the BIIC and some are duplicated in the gate arrays. Device registers can be considered as three groups.

- 1. VAXBI Required registers

- 2. BIIC Specific registers

- 3. User registers

**1.2.4.1** VAXBI Required Registers – These are provided on every device (node) that is connected on the VAXBI. These registers hold status and control information which defines how the DMB32 will respond to commands on the VAXBI.

**1.2.4.2 BIIC Specific Registers** – These registers are not required by the VAXBI specification. They support specific functions implemented by this BIIC. Features selected by the BIIC Specific Registers include the commands to be implemented by this node.

**1.2.4.3** User Registers – These are the registers through which the device application is controlled. They can be further subdivided into four groups as follows:

| ٠ | General Registers      | - | Used to control parameters and functions common to the communications interface. |

|---|------------------------|---|----------------------------------------------------------------------------------|

| ٠ | Asynchronous Registers | - | Used to control and monitor the asynchronous ports.                              |

| ٠ | Synchronous Registers  |   | Used to control and monitor the synchronous port.                                |

| • | Printer Register       | - | Used to control and monitor the printer port.                                    |

#### **1.2.5** Types of Data Transfer

The function of the DMB32 is to move data between the VAXBI and the communications interface; this can be achieved in three ways:

- 1. DMA Transfer

- 2. Programmed (RX FIFO) Asynchronous Reception

- 3. Programmed (Preempt) Asynchronous Transmission

**1.2.5.1** DMA Transfer – Synchronous RX and TX data are transferred between host memory buffers and CASRAM by DMA. The microprocessor monitors the buffers, and initiates further DMA transfers as they are needed. Transfers between CASRAM and the synchronous port are initiated by interrupt from the synchronous port to the microprocessor.

Printer data is also transferred across the VAXBI by DMA. Transfers of data from CASRAM to the printer port are performed by the microprocessor. Printer status is polled by the microprocessor, which also makes status information available in the CSRs.

Asynchronous TX data can be transferred by DMA or by programmed transfer. DMA transfers to CASRAM are controlled in the same way as synchronous data transfers. The microprocessor monitors the asynchronous ports to check if they are ready to accept data.

**1.2.5.2** Programmed (RX FIFO) Asynchronous Reception – The microprocessor transfers asynchronous RX data to a 512-character RX FIFO in CASRAM. The host reads the data, from the RX FIFO, together with error status information. The RX FIFO is also used to send diagnostic reports to the host and to send modem change information.

**1.2.5.3 Programmed (Preempt) Asynchronous Transmission** – Asynchronous TX data may be transferred to CASRAM by DMA, or it can be written to a single-character preempt register (one exists in each asynchronous channel). From there the transfer is completed by the microprocessor. A character written to the preempt register of a channel which is transmitting a DMA buffer, will be transferred to the asynchronous port before the remaining DMA data.

•

#### **1.2.6** Interrupts to the Host

The DMB32 can be programmed to interrupt a VAXBI host under the following conditions:

- When a channel is ready for another preempt character.

- When transfer of a DMA buffer from system memory to an I/O channel has:

- been aborted

- been terminated due to a memory read error

- been successfully completed

- When a received character has been placed in a previously empty RX FIFO. (The DMB32 can be programmed to delay this interrupt so that several characters can be placed in the FIFO before the interrupt is raised).

- When modem status information has been placed in the RX FIFO. This action overrides any programmed interrupt delay.

#### **1.3 HARDWARE OVERVIEW**

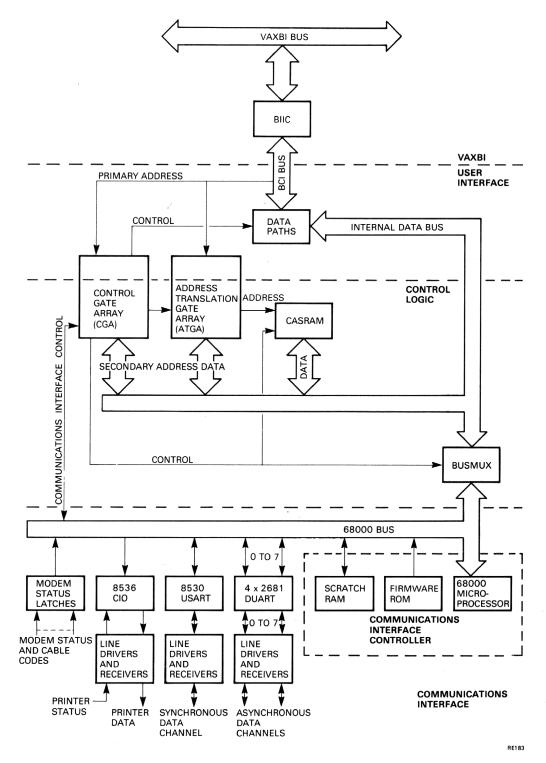

The major DMB32 hardware blocks and the buses that interconnect them are shown in Figure 1-2. In this figure, the three areas of logic are identified for comparison with Figure 1-1. A brief overview of the hardware is provided in the subsequent sections.

#### **1.3.1 VAXBI Interface (BIIC)**

The BIIC is the major functional element of the VAXBI interface. The BIIC provides a standard VAXBI family interface between the VAXBI bus and the user.

#### **1.3.2** User Interface

The functions of the devices within the user interface are defined as follows:

**1.3.2.1 Data Paths** – The Data Paths is a data bus multiplexer. Latches in this block isolate the BCI (VAXBI Chip Interface) and internal data buses. Latching the data allows the DMB32 to meet VAXBI timing requirements.

**1.3.2.2** Busmux – The Busmux is a bus multiplexer and isolator. This group of latches and drivers multiplexes the microprocessor data and address buses (68000 bus) onto the internal data bus.

**1.3.2.3** CASRAM – CASRAM is a 2 K-longword RAM that contains device registers used by both the VAXBI host and the DMB32 microprocessor to configure and control the DMB32 module. All data to and from the communications interface is transferred via registers and data buffer areas in CASRAM.

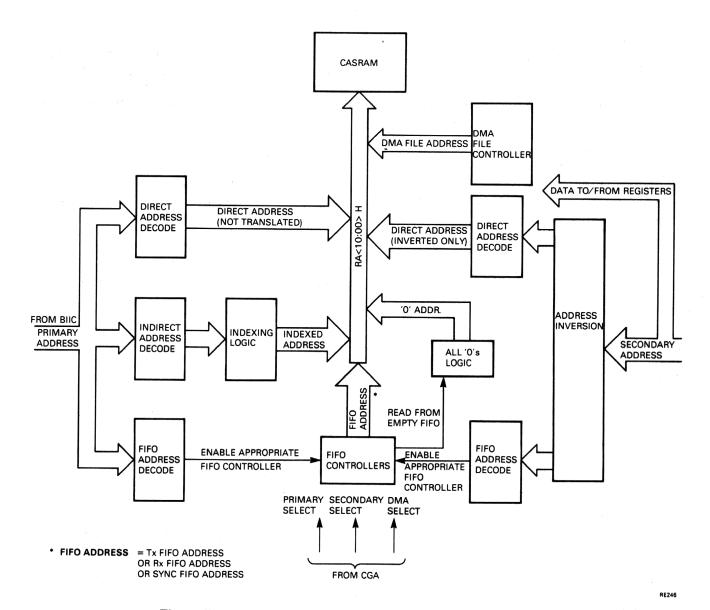

**1.3.2.4** Address Translation Gate Array (ATGA) – The ATGA multiplexes primary (VAXBI) and secondary (microprocessor) addresses for the CASRAM. It also performs address translation functions such as indexing and FIFO addressing, and 68000 versus VAX-11 addressing convention.

Figure 1-2 Hardware Overview Diagram

**1.3.2.5** Control Gate Array (CGA) – The bulk of the DMB32 logic is in the CGA. By controlling the ATGA, the CGA arbitrates between the primary and secondary address ports, allowing only one port to address the CASRAM at any time. The CGA controls the CASRAM, Data Paths and Busmux, as necessary to transfer the data.

Some of the control and decoding logic for the microprocessor and the communications interface is integrated in the CGA.

#### **1.3.3** Communications Interface

The functions of the devices within the communications interface are described in the following sections.

**1.3.3.1** Microprocessor – A68000 microprocessor with dedicated ROM and RAM forms the Communications Interface Controller. The controller controls and configures the communications interface in response to information in device registers in the CASRAM. (Like the DMB32 itself, the ICs that form the I/O ports are controlled and configured by access to internal registers).

**1.3.3.2** Asynchronous Ports – Eight asynchronous ports are provided by four 2681 Dual Universal Asynchronous Receiver Transmitter (DUART) ICs. These ICs perform the serial/parallel conversion of data, generate parity, and provide modem status and control signals.

**1.3.3.3** Synchronous Port – The synchronous port uses an 8530 Universal Synchronous Asynchronous Receiver Transmitter (USART) IC. This IC performs serial/parallel conversion of data, generates and checks CRC, and provides the modem status and control signals required for the synchronous port.

**1.3.3.4 Printer Port (Parallel Port)** – The port is formed by an 8536 Counter/timer and parallel I/O chip (CIO). This IC has three ports, one of which is used for the printer. Other ports support the printer function, monitor some of the asynchronous port modem signals, and supply a clock to the synchronous port. Counter/timers in the CIO are used to provide delays, and to alert the microprocessor to tasks that must be performed at regular intervals.

**1.3.3.5** Line Drivers and Receivers – Line drivers and receivers provide circuitry to drive data on a line, and to reconstitute received data. In the case of serial data communications lines, line drivers and receivers convert between TTL levels on the option and EIA levels on the lines. The printer channel is at TTL level only.

#### **1.4 DATA ROUTING**

During DMA transfers, or when the host writes or reads a register, data between the VAXBI and CASRAM is routed as follows:

| WRITE BIIC – Data Paths – CASRAM | WRITE | BIIC - | Data | Paths – | CASRAM |

|----------------------------------|-------|--------|------|---------|--------|

|----------------------------------|-------|--------|------|---------|--------|

READ CASRAM – Data Paths – BIIC

Data to or from the I/O ports is routed as follows:

| WRITE | BIIC – Data Paths – CASRAM – microprocessor – I/O Port |

|-------|--------------------------------------------------------|

| READ  | I/O Port - microprocessor - CASRAM - Data Paths - BIIC |

For each type of transfer, the CGA controls the ATGA, CASRAM, Data Paths, and Busmux, as necessary.

### CHAPTER 2 FUNCTIONAL DESCRIPTION

#### 2.1 SCOPE

Chapter 2 provides operational information on the facilities provided by the DMB32. The Overview section contains details of DMA Operation, VAX-11 Address Translation, Interrupts, and Synchronous Operation; this is followed by a section on compliance with the Electrical Interface Standards. Sections are also included on Modem Control, DMB32 Protocol Support, HDLC/SDLC Support, DDCMP Support, IBM Bisync Support, and General Byte Support. Finally, the chapter provides information on the Asynchronous Multiplexer, and the Printer Interface.

#### 2.2 OVERVIEW

The DMB32 module, containing an on-board 68000 microprocessor and firmware, implements a communications controller as described in the previous chapter. The main functions of the DMB32 are to provide the following communications facilities:

- 1. Synchronous Controller handling the following protocols:

- HDLC/SDLC

- IBM BISYNC

- DDCMP

- GEN BYTE

- 2. Asynchronous Multiplexer for eight lines

- 3. Line Printer Interface

The microprocessor is the main controller of the DMB32 but some state oriented control is implemented by the CGA controlling the CASRAM in particular. All VAXBI bus protocol and control is handled by the BIIC.

#### 2.2.1 DMA Operation

DMA data transmissions are implemented for synchronous transmission and reception, asynchronous transmission, and line printer output. DMA operations support both virtual and physical mapping of the host memory.

In order to use the maximum bandwidth of the VAXBI bus, the DMB32 attempts to use octaword transfers wherever possible, and achieves this by the use of internal DMA files kept in CASRAM. A DMA file is used to accept data from the VAXBI on transmit, and to supply data to the VAXBI on receive. The DMA file holds up to an octaword of data and the relevant physical address within the host memory buffer.

During the progress of a DMA, the DMB32 does not update the count and address registers, so it is not possible for the host to track the progress of a DMA via these registers. An exception to this is when the GEN BYTE protocol is being used in receive messages; for these messages, only the count register is maintained. The count is a DMA count and because of the nature of the DMA files, at any given time it may be up to 16 bytes out of date.

#### 2.2.2 VAX-11 Address Translation

The DMB32 is able to carry out VAX-11 address translation for use when accessing DMA buffers. It can use one of four modes of address translation as described in the subsequent sections.

**2.2.2.1** Physical Address of Buffer – The DMB32 performs no address translation, but is given the physical address of the buffer and the length. The buffer must be contiguous in physical memory. This mode makes no assumptions about the virtual address structure used by the host processor.

**2.2.2.2** Physical Address of Page Table – The DMB32 is given the physical address of a page table. Each entry in the page table is 4 bytes long. The DMB32 is given the offset of the first byte of the buffer which is in the page described by the page table entry. (This number must be less than 512). Each page table entry contains bits 9 to 29 of the physical address of the page that is to be accessed. The remaining high order bits in the page table entry are ignored. This mode allows buffers to be split into several pages.

**2.2.2.3** System Virtual Address of Buffer – This mode of address translation uses the VAX Address Translation Structure, as described in the VAX Architecture reference manual.

The DMB32 is given the system virtual address of the buffer. It then accesses page table entries in the system (and possibly global) page tables to perform the address translation. A page table entry has the following format:

- Bits<20:0> PFN. These bits contain the high order 21 bits of the physical address to be used to access the page (except when the PTE indicates that a global page table entry is to be used).

- Bits<21:0>

- Global Page Table Index. When the PTE indicates a global page is to be accessed, these bits indicate the index to be used to access the global page table entry.

#### NOTE

### Only one of the above formats will apply at any given time, as determined by bits 31, 26, and 22.

• Bit<22>

- This bit, together with bits 26 and 31, indicates the format of the PTE. The following combinations are recognized:

| 31 | 26 | 22 |   |                                                                                            |

|----|----|----|---|--------------------------------------------------------------------------------------------|

| 1  | х  | x  | - | valid page                                                                                 |

| 0  | 0  | 0  | _ | valid page                                                                                 |

| 0  | 0  | 1  | - | use PFN to index global page<br>table (not valid in an entry in<br>the global page table). |

| 0  | 1  | х  | _ | not valid                                                                                  |

• Bits<25:23>

- Not used

- Bit<26>

- Bits<30:27>

- See bit 22

- Protection code. This field is checked to ensure that kernel mode has access to the page. The field must not contain 0 or 1 when the page is to be read by the DMB32, and must not contain 0, 1, 3, 7, 11 or 15 if the page is to be written by the DMB32. Only one protection code field is used for any page to be accessed. This comes from the first PTE that describes the page. The codes in global page table entries and in system page table entries, that are accessed in order to find another page table entry, are ignored.

• Bit<31>

- See bit 22

When the PTE indicates that a global page table entry is to be found, the DMB32 calculates the system virtual address of the global page table entry by multiplying the index (bits<21:0>) by four and adding the result to the address of the base of the global page table. The DMB32 reads the PTE which results in another system page table translation. This second system PTE must not refer to another global page table, nor must the entry be found in the global page table. At most, one global page table entry is fetched for translating any page address.

**2.2.2.4** System Virtual Address of Process Page Table – The DMB32 is given the system virtual address of a process page table entry which describes the page containing the first byte of the buffer. The longwords that follow describe the succeeding pages of the buffer. The format of the page table entries is the same as in the previous mode. This method allows the DMB32 to directly access process buffers. The use of the system virtual address allows for the handling of non-contiguous PTEs describing a process buffer.

Address translations using the system page table are necessary to access the entries in a process page table. If the entry in this table refers to a global page then further PTEs will need to be accessed from the system page table and the global page tables as described for the previous mode.

#### 2.2.3 Interrupts

There are four interrupt vectors used by the DMB32, these are defined as follows:

- BIIC error interrupts

- Asynchronous Interrupts (Transmit and Receive)

- Printer Interrupts

- Synchronous Interrupts

These interrupts are all at the lowest interrupt priority on the VAXBI bus. The DMB32 interrupts with a vector made up in the following way:

0

• Bits<1:0>

Bits<5:2>

- The Node ID (Node Identifier)

The use of these interrupts is controlled by four interrupt enable bits (two for asynchronous, one for synchronous, and one for printer). The error interrupt is controlled by a separate mechanism in the BIIC.

If the appropriate enable bit is set when an interrupting condition occurs, then the DMB32 will interrupt immediately. If the enable bit is not set then the interrupt will be delayed until the interrupt enable bit is set. This interrupt may occur even if the interrupt condition has been removed; for example, if the host empties a FIFO and then sets the interrupt enable bit, an interrupt may be generated with the FIFO empty.

If the enable bit is cleared after an interrupt request is made by the DMB32, then the interrupt may still take place; for example, if the interrupt enable bit is cleared while the host is running at an IPL which would prevent the interrupt taking place. The interrupt may still have taken place when the IPL was lowered, even if the interrupt condition had been removed and the interrupt enable bit cleared.

If the interrupt enable bit is cleared after an interrupt is requested, but without processing the interrupt condition, then there may not be a second interrupt if the enable bit is set later. This applies even if the condition which caused the original interrupt remains; for example, if a FIFO is not emptied but the enable bit is cleared, then when the enable bit is later set again, there may not be a further interrupt until the FIFO is emptied and new entries made. This means that the host driver is not able to set the interrupt bit, and therefore get an interrupt to continue processing the interrupt data, unless it is sure that the interrupt condition was removed when the enable bit was cleared.

#### 2.2.4 Synchronous Operation

In order to facilitate synchronous communications the host system must first allocate a host memory buffer. The address and size of this buffer must be then passed to the DMB32 via the appropriate registers and the appropriate DMA START bit must be set.

Due to the time-critical nature of synchronous communications and use of generally higher transfer speeds, the synchronous port may be allocated two buffers for transmit and two for receive. This allows the host system to service one buffer while the DMB32 is transferring data to or from the other. For the same reasons, the DMB32 allocates two internal DMA files to each synchronous buffer within the host, thus allowing similar double buffering to take place between the microprocessor and the CGA. To permit the microprocessor to order these and other tasks, the synchronous DMA files are assigned to different work queues representing the DMA file state. The following queues are used:

**2.2.4.1** Synchronous Transmit Full DMA File Queue – This queue is used to order the transfer of data from TX DMA files, having been filled with data transferred from the host memory transmit buffers, to the synchronous communications port.

**2.2.4.2** Synchronous Transmit Done DMA File Queue – This queue is used to order the refilling of TX DMA Files from the host memory transmit buffers, once their contents have been transferred to the synchronous communications port.

**2.2.4.3** Synchronous Receive Empty DMA File Queue – This queue is used to order the presenting of RX DMA files with valid translated physical addresses, to the synchronous receive process. These files are then filled with receive data from the synchronous line.

**2.2.4.4** Synchronous Receive Full DMA File Queue – This queue is used to order the unloading of the RX DMA buffers to the host memory buffers once they have been filled by the synchronous receive process.

**2.2.4.5** Synchronous Buffer Translate Queue – This queue is used to submit requests for host buffer address translation. It is shared by the synchronous transmit and the synchronous receive processes.

**2.2.4.6** Further Information – The internal DMA files are pointed to indirectly, via Synchronous File Status Blocks (SFSBs) which track the contents of the DMA file and the phase of the communications protocol in use. The SFSBs also point to another status block called the Synchronous Buffer Status Block (SBSB) which describes and tracks the host memory buffer.

In the case of Synchronous RX DATA the synchronous receive process requests a DMA file from the Synchronous Receive Empty DMA file queue. This file is empty of data but contains the valid physical address of the next octaword to be filled in the host memory buffer. The microprocessor fills the file with 16 bytes of data received from the synchronous line. In the case of start or end of buffer, where less than an octaword transmission is required, the size of transfer is tracked via the SFSB. This information is used for the byte mask during the VAXBI data cycle. When filled, the DMA file is queued to the Synchronous Receive Full DMA file queue. The CGA gate array controls the actual DMA of the data in the DMA file, across the VAXBI bus to host memory. The microprocessor first has to set up the following registers:

| 1. | DMA File Address Register – | This register is found in the ATGA and contains the address of the DMA File in CASRAM. The address is incremented as each longword is transferred.        |

|----|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2. | VAXBI Command Register -    | This register is found in the CGA. Writing to the register causes the corresponding command to be initiated on the VAXBI bus.                             |

| 3. | VAXBI Mask Register -       | This register is found in the CGA, and is used by the microprocessor to indicate which bytes to transfer, when less than a longword transfer is required. |

The CGA indicates the status of the transfer to the microprocessor via its VAXBI Status register. Having completed the DMA the CGA indicates this to the microprocessor. The empty DMA file, after being loaded with a valid host memory physical address, is passed back to the Synchronous Receive Empty DMA file queue ready to accept more synchronous receive data.

The synchronous transmit procedure is similar to that of the receive procedure. This time the address of an empty DMA file, with a valid host memory transmit buffer physical address written into it, is loaded into the DMA file Address Register. Where necessary, the VAXBI mask bits are loaded into the VAXBI Mask Register and the appropriate command is loaded into the VAXBI Command Register. The CGA controls the DMA of data from host memory into the DMA file. When this transfer is complete the microprocessor places the full DMA file in the Synchronous Transmit Full DMA file queue. The synchronous transmit process can now service this queue, transferring data from the DMA file to the synchronous line. TX DMA files, when empty, are now passed to the Synchronous Transmit Done DMA file queue for re-use. The use of two DMA files per host buffer will allow the CGA to be filling or emptying one file while the microprocessor services the other.

#### 2.3 SYNCHRONOUS INTERFACE

Electrically and mechanically, the T1012/H3033 synchronous port is:

- Compliant with RS-232-C, RS-422-A/RS-449, V.11, X.27 and V.35

- Compatible with RS-423-A/RS-449, V.28/V.24, V.10 and X.26

The maximum sensible speed that can be used on the sync port depends on the protocol and electrical interface standard selected. Table 2-1 lists the maximum sensible speeds for all the supported protocols. The maximum total throughput for the sync port is 16000 char/s.

|          | <b>Electrical Interface Standard</b> |               |               |       |          |  |

|----------|--------------------------------------|---------------|---------------|-------|----------|--|

| Protocol | RS-232                               | <b>RS-423</b> | <b>RS-422</b> | V.35  |          |  |

| DDCMP    | 19200                                | 19200         | 19200         | 19200 | <br>Data |  |

| HDLC     | 19200                                | 64000         | 64000         | 48000 | (Bits,   |  |

| BISYNC   | 9600                                 | 9600          | 9600          | 9600  |          |  |

| GEN BYTE | 9600                                 | 9600          | 9600          | 9600  |          |  |

Table 2-1

Maximum Sensible Speeds (Sync Port)

#### **2.4 MODEM CONTROL (SYNC PORT)**

Modem status changes are reported by an interrupt. Since there is no indication of which bits have changed, the host is expected to keep a record of the last modem status it saw. This will enable the host to identify which bits have changed. There are two special modem control bits which show whether or not the receive and transmit clocks are working. If no transition is detected on any clock line from the modem for 1 second, the appropriate modem control bit is cleared. When one of these bits is cleared, any transfer in the corresponding direction will terminate with an error indication. Other modem state changes can also affect transfers; for example, loss of DCD or DSR will abort a received message, and loss of DSR or CTS will abort a transmission. If the host drops DTR or RTS during a transmission, the DMB32 will not drop the corresponding signal to the modem, until the message and trailing pads have been transmitted.

#### 2.4.1 Modem Control Signals

Table 2-2 lists the interchange circuits which are supported for the synchronous port on the DMB32.

The state of the modem status lines is sampled at 10 ms intervals and compared to the last reported state. If there has been a change of state the line status register is updated. Ring Indicator signal (Circuit 125) is monitored over a period of 30 ms, and a change recorded only if the state of the signal has been constant over this period.

| EIA RS-449<br>Signal Name |                             |    |    | EIA RS-232-C<br>Signal Name                          |     | CCITT V.24<br>Signal Name |                                                      | Pin |

|---------------------------|-----------------------------|----|----|------------------------------------------------------|-----|---------------------------|------------------------------------------------------|-----|

| _                         | Shield                      | 1  | AA | Protective Ground                                    | 1   | _                         |                                                      | _   |

| SG                        | Signal Ground               | 19 | AB | Signal Ground                                        | 7   | 102                       | Signal Ground                                        | 7   |

| SC                        | Send Common                 | 37 | -  | -                                                    | _   | _                         | -                                                    | -   |

| RC                        | Receive Common              | 20 | _  |                                                      | -   | _                         |                                                      | -   |

| IS                        | Terminal In Service         | 36 | _  |                                                      | _   | · _                       |                                                      | -   |

| IC                        | Incoming Call               | 15 | CE | Ring Indicator                                       | 22  | 125                       | Calling Indicator                                    | 22  |

| TR                        | Terminal Ready (+)          | 12 | CD | Data Terminal Ready                                  | 20  | 108/2                     | Data Terminal Ready                                  | 20  |

| TR                        | Terminal Ready (-)          | 30 | -  |                                                      | -   | _                         |                                                      | -   |

| DM                        | Data Mode (+)               | 1  | CC | Data Set Ready                                       | 6   | 107                       | Data Set Ready                                       | 6   |

| DM                        | Data Mode (-)               | 29 | _  |                                                      | -   | _                         |                                                      | -   |

| SD                        | Send Data (+)               | 4  | BA | Transmitted Data                                     | 2   | 103                       | Transmitted Data                                     | 2   |

| SD                        | Send Data (-)               | 22 | -  |                                                      | _   | _                         |                                                      | -   |

| RD                        | Received Data (+)           | 6  | BB | Received Data                                        | 3   | 104                       | Received Data                                        | 3   |

| RD                        | Received Data(-)            | 6  | -  |                                                      | _   | -                         |                                                      |     |

| TT                        | Terminal Timing (+)         | 17 | DA | Transmitter Signal<br>Element Timing (DTR<br>Source) | 24  | 113                       | Transmitter Signal<br>Element Timing (DTR<br>Source) | 24  |

| ГТ                        | Terminal Timing (-)         | 35 | -  |                                                      | -   | -                         |                                                      |     |

| ST                        | Send Timing (+)             | 5  | DB | Transmitter Signal<br>Element Timing (DCE<br>Source) | 15  | 114                       | Transmitter Signal<br>Element Timing (DCE<br>Source) | 15  |

| ST                        | Terminal Timing (-)         | 23 | -  |                                                      | -   | -                         |                                                      | -   |

| RT                        | Receive Timing (+)          | 8  | DD | Receiver Signal<br>Element Timing                    | 17  | 115                       | Receiver Signal<br>Element Timing                    | 17  |

| RT                        | Receive Timing (-)          | 26 | -  |                                                      | -   | -                         |                                                      | -   |

| RS                        | Request To Send (+)         | 7  | CA | Request To Send                                      | 4   | 105                       | Request To Send                                      | 4   |

| RS                        | Request To Send (-)         | 25 | -  |                                                      | -   | -                         |                                                      | -   |

| CS                        | Clear To Send (+)           | 9  | CB | Clear To Send                                        | 5   | 106                       | Clear To Send                                        | 5   |

| CS                        | Clear To Send (-)           | 27 | -  |                                                      | -   | -                         |                                                      | -   |

| RR                        | Receiver Ready (+)          | 13 | CF | Received Line Signal<br>Detector                     | 8   | 109                       | Data Channel Received<br>Line Signal Detector        | 8   |

| RR                        | Receiver Ready (-)          | 81 | -  |                                                      | -   | -                         |                                                      | -   |

| SQ                        | Signal Quality              | 33 | CG | Signal Quality Detector                              | 21  | 110                       | Data Signal Quality<br>Detector                      | 21  |

| NS                        | New Signal                  | 34 | -  | \$                                                   | _ # | -                         |                                                      | -   |

| SR                        | Signaling Rate Selector     | 16 | СН | Data Signal Rate<br>Selector (DTE Source)            | 23  | 111                       | Data Signaling Rate<br>Selector (DCE Source)         | 23  |

| SI                        | Signaling Rate<br>Indicator | 2  | CI | Data Signal Rate<br>Selector (DCE Source)            | 23  | -                         |                                                      | -   |

| LL                        | Local Loopback              | 10 | -  |                                                      | -   | 141                       | Local Loopback                                       | 18  |

| RL                        | Remote Loopback             | 14 |    |                                                      | -   | 140                       | Remote Loopback                                      | 21  |

| ГМ                        | Test Mode                   | 18 | -  |                                                      | -   | 142                       | Test Indicator                                       | 25  |

| SS                        | Select Standby              | 32 | -  |                                                      |     |                           |                                                      | -   |

| SB                        | Standby Indicator           | 36 | -  |                                                      | -   | -                         |                                                      | -   |

Table 2-2

Synchronous Interchange Circuits

#### 2.5 PROTOCOL SUPPORT (SYNC PORT)

The synchronous controller will support message framing and CRC generation and checking of the following protocols:

- HDLC/SDLC

- DDCMP

- IBM BISYNC

Error recovery, message sequencing, and retransmission are not performed by the DMB32. Software assistance is required to implement the full protocols.

Other byte oriented protocols can be supported by the GEN BYTE protocol. This allows the DMB32 to receive and transmit messages in other protocols, but software is required for all intelligent interpretation of their contents.

The synchronous line is capable of running at 64 Kbit/s (full duplex) for HDLC and SDLC protocols only. For DDCMP it will run at 19.2 Kbit/s. Other protocols are capable of running at 9600 bit/s.

#### 2.6 HDLC/SDLC SUPPORT (SYNC PORT)

The DMB32 supports HDLC/SDLC protocol message framing. No error recovery or message sequencing is carried out without software help.

#### 2.6.1 Message Definition

An HDLC/SDLC message is a frame consisting of a sequence of bits preceded by a flag character (01111110) and followed by either a flag character or a 7-bit abort sequence (1111111). The bits between these delimiters are the data followed by the block check characters.

To prevent bit patterns in the data stream from being wrongly interpreted as flag characters, the data is transparently encoded by inserting an extra '0' bit following each '11111' sequence found in the data to be transmitted.

On reception, these inserted '0' bits are removed. This bit stuffing and stripping is carried out by the DMB32. Only messages which are a multiple of the character size long are legal. If the final flag is not on a character boundary then an error is indicated.

The block check is normally found in the final bits of the frame; however, if the frame is terminated by an abort sequence then there is no block check sequence in the frame. After the transmission of the closing flag of a frame, the DMB32 can either send further flag sequences or a continuous mark, depending on the state of the IDLE.SYNC bit.

At least one flag will be transmitted before a message, this flag can be the same flag that closes the previous message. Messages must have at least two data characters. If a shorter message is received it will be discarded.

#### 2.6.2 Block Check

The block check is normally CRC-CCITT, but the following block checks can also be specified:

- CRC-CCITT preset to 1s

- No block check no block check is transmitted, but one can be included at the end of the buffer if an alternative block check is desired.

#### 2.6.3 Character Size

Only the eight bit character size can be specified for HDLC/SDLC.

#### 2.6.4 Address Bytes

If the device is set up as a secondary station then the first one or two bytes of a message are inspected to determine if they match the station address, in ADDRESS1 and ADDRESS2. If they do not match then the received message is ignored and the receiver waits for the next message.

The address match procedure is not the same for SDLC and for HDLC. SDLC only uses one-byte addresses; the first byte of the message is compared with the first byte of the address. The all stations address (11111111) is also recognized as an address match.

HDLC can use one- or two-byte addresses. The low bit of the first address byte indicates whether one- or two-byte addresses are used. If this bit is a '0', two-byte addresses are used. If it is a '1', then one-byte addresses are used. The appropriate bytes of the message are compared with the address bytes provided by the host. The all stations address (1111111) is also recognized as an address match.

The ADCCP protocol can also be implemented using HDLC mode. ADCCP allows more than two bytes of address. In this case the DMB32 checks the first two bytes, further bytes are checked by the host.

#### 2.6.5 Aborting a Transmission

If the host aborts a transmission after the first byte has been passed to the USART, and before the final flag has been transmitted, then the DMB32 will transmit an 8-bit abort sequence (11111111) to abort transmission. A transmission may also be aborted if some error is discovered while transmitting a message; for example, memory error or transmit underrun condition.

#### 2.7 DDCMP SUPPORT (SYNC PORT)

The DMB32 supports the framing of DDCMP messages, valid start of message recognition, and CRC generation and checking. Software is required to support error recovery, message sequencing, and retransmission.

#### 2.7.1 Message Definition

The DMB32's interpretation and actions with regard to the structure of a DDCMP message are described as follows:

**2.7.1.1** SYNSEQ – A number of SYNC (synchronization) characters  $(96_{16})$  precede a DDCMP message. The DMB32 will accept abutting DDCMP messages that have no synchronization characters separating them, provided that no error has been detected and the QSYNC bit in the previous message is clear. The DMB32 will normally attempt to send abutting messages.

If a message that has the QSYNC bit set is sent, the DMB32 will send at least four synchronization characters following the message. If no message is available for transmission abutting a message with QSYNC clear (or the value in LPR1 is not zero), then at least 8 synchronization characters will be sent between messages. If any transmit error is detected; for example, memory error, or transmit underrun, then at least eight synchronization characters will be sent before the next message. The DMB32 will always send at least the number of synchronization characters specified in LPR1.

DDCMP requires that eight synchronization characters are transmitted before the following messages:

- Maintenance messages (starting with DLE)

- Messages with the SELECT bit set

- Messages with a change in the ADDR field

- Control messages other than ACK

- Any message after starting up

- Any message after idling mark

- The first message after receiving a NAK

- Messages with a change in the ADDR field

The DMB32 does not automatically send these synchronization sequences for the first five classes listed. The host is required to set the number of synchronization characters in LPR1 before initiating transmission. The DMB32 will force an eight byte sequence in the last two classes.

The DMB32 will not send PAD characters after a message if the next message abuts the first or is separated from it by exactly four synchronization characters (due to QSYNC being set).

#### 2.7.2 Start of Message (SOM)

A single character indicates the start of a DDCMP message. This character must be one of the following valid DDCMP start of message characters:

- SOH  $(81_{16})$  Data Message

- $ENQ (05_{16}) Control Message$

- DLE (90<sub>16</sub>) Maintenance Message (MOP)

The start of message character is transferred to memory on a received message.

If the first character of the message is not one of the valid starting characters then the DMB32 will resynchronize, looking for a new SYNC character.

**2.7.2.1** COUNT – This is a two byte field which indicates the number of characters in the data field of the message. Only the bottom 14 bits of this word are used as the count; the high order two bits are the control flags QSYNC and SELECT. The two bytes are transferred to memory on received messages. In a control message there is no data field and therefore no COUNT is required. In this case the count field contains control information.

**2.7.2.2 QSYNC** – This flag is bit six of the second byte of the COUNT field; it indicates that the next message will not abut this message. On transmission, the DMB32 uses the contents of the bit to check if it must insert SYNC characters between messages. On received messages the DMB32 uses the bit to check if it must re-synchronize at the end of the message.

**2.7.2.3** SELECT – This flag is used in DDCMP to control line turn around in half duplex working. The DMB32 does NOT use this bit.

**2.7.2.4** CONTROL – This field contains two bytes of control information on control messages. On received messages, the DMB32 will just transfer these bytes to memory.

**2.7.2.5** ADDR – This field is one byte in length and is used in DDCMP multi-point operation, however the DMB32 does not support DDCMP multi-point operation.

**2.7.2.6** CRC1 – This field is two bytes in length containing CRC-16 information for the message header: SOM, COUNT, CONTROL, and ADDR. This field is not transferred to memory on receive messages and is generated by the DMB32 on transmit messages. On received messages if this CRC is incorrect, reception is terminated and re-synchronization takes place.

**2.7.2.7** DATA – This field contains COUNT bytes of data that are transferred to memory on receive messages. This field is not present in a control message that is started by an ENQ character  $(05_{16})$ .

**2.7.2.8** CRC2 – This field contains two bytes of CRC-16 data for the DATA field that is not transferred to memory on receive messages. The DATA field is not present in control messages.

**2.7.2.9** PAD – The PAD field consists of a number of DEL bytes (FF<sub>16</sub>) which are transmitted following the final CRC. The DMB32 accepts messages that do not have these bytes. The DMB32 always transmits two PAD characters after a message. This field is not transferred to memory on received messages. If the character following the last byte of the last CRC in a message is not a DEL, DLE, SOH, ENQ or SYN then the last CRC is regarded as being invalid and re-synchronization takes place.

#### 2.7.3 Character Size

The only character size allowed is 8.

#### 2.7.4 Aborting Transmission

DDCMP does not allow a transmitter to abort transmission. If it is necessary to abort a transmission, for example, if a memory error occurs, then the DMB32 will transmit CAN characters  $(18_{16})$  until three characters after the following CRC would have been sent. This is likely to cause a CRC error to be detected by the other receiver. Following this it will send at least eight further synchronizing characters before the next message, to allow the other receiver to re-synchronize.

#### **2.8 IBM BISYNC SUPPORT (SYNC PORT)**

#### 2.8.1 Message Definition

The message defined here is the unit of transmission that is contained in one buffer, and does not correspond with the definition of a message used in the description of IBM BISYNC.

A message starts with the first non-synchronizing character, and continues until one of the following sequences is recognized:

- ENQ

- ACK0

- ACK1

- NAK

- WACK

- RVI

- TTD

- EOT

- ETB + block check

- ETX + block check

The DMB32 assumes that the data in a transmit buffer is a complete message, and thus does not check that the message ends with one of the above sequences.

When a message is received, the DMB32 automatically starts searching for a new synchronization sequence.

**2.8.1.1** Transparent Mode – It is not possible to transmit certain control characters in a message. If binary data is being transmitted, a transparent mode must be used to enable these characters to be sent.

Transparent mode is indicated by the sequence DLE, STX in the message. Once this sequence has been seen, the characters that follow are in transparent mode, until a block check sequence is received.

In transparent mode a DLE has to be transmitted before any of the following characters:

- ETB

- ETX

- SYN

- ENQ

- DLE to allow DLE to be part of the message

- ITB

Control characters received without the preceding DLE are assumed to be part of the text of the message. The DMB32 will transfer these DLE characters to the buffer that the host provides, on reception, and expects them to be in the transmit buffer. DLE characters are included in the block check.

Following a DLE, ITB, block-check sequence, non-transparent mode is entered. Normally a DLE, STX will be received which will return the DMB32 to transparent mode.

**2.8.1.2 Block Check** – Either VRC/LRC or CRC-16 are normally used with IBM BISYNC. VRC/LRC is normally used for ASCII, and CRC-16 for EBCDIC. The DMB32 will support either block check sequence for ASCII. If VRC is specified then 7-bit characters must also be specified. 8-bit characters must be specified with CRC-16.

The DMB32 will commence calculating the block check for a message, after it sees the first STX or SOH character. This character is not included in the block check. Other characters not included in the block check, are those preceding the STX or SOH.

The block check is inserted in transmitted messages and checked in received messages after the following characters; the character is included in the block check.

- ETX

- ETB

- ITB

ITB characters are used to separate records within one message. Each record has its own block check. If any of these checks fail in a received message, a block check error is indicated to the host.

On transmission, the VRC/LRC block check character is followed by two PAD characters, and if a PAD character is received it will be discarded. On reception, the block check characters are transferred to memory. On transmission, the host is expected to insert dummy characters in the buffer, and these are replaced by the calculated block check, unless the block check mode specifies that a block check is not required.

**2.8.1.3** Inserted SYNC Characters – SYNC characters can be embedded in messages. These characters are not included in the block check and are ignored when they are received. The DMB32 will insert a SYNC sequence whenever the transmission has been in progress without a SYNC for more than 1 second. Note that SYNC sequences in transparent messages are formed by the combination DLE SYN, and for normal messages by SYN SYN.

At least three SYNC characters are transmitted before each message to ensure that the receiver is synchronized. This value is taken from NUMBER.SYNC in LPR1. This is normally set to three for IBM BISYNC by the host.

**2.8.1.4** PAD Characters – A PAD character is transmitted after every message. This character is  $FF_{16}$ , and it is sent to ensure that data is passed to the modem before it turns the line round (BISYNC normally operates in half duplex mode). The DMB32 will ignore a PAD character following a message.

**2.8.1.5** Character Sets – IBM BISYNC can work in either ASCII or EBCDIC, selected by a bit in the line parameter register (6-bit transcode is not supported by the DMB32). The control characters used by BISYNC depend on which character set is selected.

**2.8.1.6** ASCII Character Set – The following control character sequences (in hexadecimal) are used in ASCII mode:

- SYN  $16_{16}$

- $ENQ 05_{16}$

- STX  $02_{16}$

- SOH 01<sub>16</sub>

- ETB  $17_{16}$

- EOT  $04_{16}$

- $ETX 03_{16}$

- NAK 15<sub>16</sub>

- ACK 06<sub>16</sub>

- ITB  $1F_{16}$

- ACK0 DLE, 30<sub>16</sub>

- ACK1 DLE, 31<sub>16</sub>

- WACK DLE,  $3B_{16}$

- DLE  $10_{16}$

- RVI DLE,  $3C_{16}$

- TTD STX, ENQ

- BEL  $07_{16}$

The character size must be seven with VRC checking, or eight without VRC checking.

2.8.1.7 EBCDIC Character Set – The following character sequences (in hexadecimal) are used in EBCDIC mode:

- SYN 32<sub>16</sub>

- $ENQ 2D_{16}$

- STX  $02_{16}$

- SOH 01<sub>16</sub>

- EOB/ETB 26<sub>16</sub>

- EOT 37<sub>16</sub>

- $ETX 03_{16}$

- NAK  $3D_{16}$

- ACK  $2E_{16}$

- ITB  $1F_{16}$

- ACK0 DLE, 70<sub>16</sub>

- ACK1 DLE, 61<sub>16</sub>

- WACK DLE,  $6B_{16}$

- DLE  $-10_{16}$

- RVI DLE,  $7C_{16}$

- TTD STX, ENQ

- BEL  $2F_{16}$

The character size must be eight.

**2.8.1.8** Aborting a Transmission – If the host aborts a transmission after the first byte has been passed to the USART, and before the final character has been transmitted, then the DMB32 will transmit an ENQ sequence (DLE ENQ in transparent mode) to abort the transmission. A transmission may also be aborted if some error is discovered while transmitting a message; for example, memory error or transmit underrun condition.

#### 2.9 GENERAL BYTE SUPPORT (SYNC PORT)

#### 2.9.1 General Description

The GEN BYTE protocol is provided as an aid in using protocols that are not directly supported by the DMB32. It allows the host to receive and send arbitrary synchronous characters.

2.9.1.1 Received Data – Once synchronization is established, using the synchronization character specified by the host, all received characters are transferred to memory. Embedded synchronization characters can be transferred or ignored, as desired by the host. Block check is calculated on all characters transferred to memory. A transfer terminates at the end of the buffer, when the optional match character is detected or when some error is detected; for example, modem status error, or memory error. The host is expected to do the analysis of message structure from the characters received in the buffer, the DMB32 does little more than transfer them into memory.

The byte count field in RXBUFCT(1/2) is updated after every DMA. This enables the host to determine how many characters have been received while a message is being received, thus allowing the host to process messages before the host buffer is filled up. This is useful because there are many protocols for which the DMB32 is not able to determine the end of message itself.

Because of the use of internal DMA files by the DMB32, a DMA transfer will normally take place when sufficient characters have been received to cross an octaword memory boundary. This means that the DMA byte count will often be up to 16 bytes behind the actual received characters. Due to internal buffering the DMA byte count can be up to 322 bytes out of date.

**2.9.1.2** Character Size – If VRC is not specified then a character size of 6 or 8 is selected. If VRC is specified then character size of 7 is selected.

NOTE If VRC/LRC is specified as the block check then a parity bit will be added to all characters transmitted. **2.9.1.3** Block Check – The following block checks are supported:

- No block check -6, 7, 8 bits per character only

- CRC-16 8 bits per character only

- VRC even 7 bits per character only

- VRC odd 7 bits per character only

- VRC/LRC even 7 bits per character only

- VRC/LRC odd 7 bits per character only

**2.9.1.4** Aborting a Message – If a transmission is aborted then either mark or SYNC characters will be sent, according to IDLE.SYNC.

#### 2.10 ASYNCHRONOUS INTERFACE

The DMB32 implements an 8-line asynchronous multiplexer, with split speed and full modem control capabilities. The following formats are supported in half duplex or full duplex modes:

- 1 start bit

- 5, 6, 7 or 8 Data bits

- Odd parity, even parity, or no parity

- 1, 1.5 or 2 stop bits

Electrically and mechanically, the T1012/H3033 asynchronous ports are:

- Compliant with RS-232-C

- Compatible with V.28/V.24

The T1012 module is also compliant with RS-423-A, V.10 and X.26, but the H3033 is not, due to pin limitations on the 25-way D-type connector.

Half duplex operation is only supported on systems using coded link control, because the DMB32 does not support the secondary transmit and receive signals which are often used for link control. The asynchronous ports are implemented using DUARTs and are associated in the following manner:

- Ports 0 and 1 use the same DUART

- Ports 2 and 3 use the same DUART

- Ports 4 and 5 use the same DUART

- Ports 6 and 7 use the same DUART

#### 2.10.1 Speeds

Split speed operation, using different transmit and receive speeds, is supported on the DMB32 asynchronous ports. The supported speeds are given in Table 2-3.

| Speed (bit/s) | Groups  |

|---------------|---------|

| 50            | Α       |

| 75            | В       |

| 110           | A and B |

| 134.5         | A and B |

| 150           | В       |

| 300           | A and B |

| 600           | A and B |

| 1200          | A and B |

| 1800          | В       |