DL11 asynchronous line interface manual

DL11 asynchronous line interface manual

digital equipment corporation · maynard, massachusetts

( )·

1st Edition, September 1972 2nd Printing, May 1973 3rd Printing (Rev), June 1974 4th Printing, January 1975 5th Printing (Rev), September 199

## Copyright © 1972, 1973, 1974, 1975 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DEC       | PDP          |

|-----------|--------------|

| FLIP CHIP | FOCAL        |

| DIGITAL   | COMPUTER LAB |

| UNIBUS    |              |

#### CONTENTS

## CHAPTER 1 INTRODUCTION

| 1.1 | Introduction             |   |

|-----|--------------------------|---|

| 1.2 | Scope 1-1                |   |

| 1.3 | Maintenance 1-3          | ; |

| 1.4 | Engineering Drawings 1-3 | ; |

## CHAPTER 2 GENERAL DESCRIPTION

| 2.1   | Introduction                  |

|-------|-------------------------------|

| 2.2   | Available Options 2-1         |

| 2.3   | Data Format                   |

| 2.4   | Functional Description 2-6    |

| 2.4.1 | DL11 Dataset Interface 2-6    |

| 2.4.2 | DL11 Teletype Control 2-8     |

| 2.4.3 | DL11 EIA Terminal Control 2-9 |

| 2.5   | Physical Description          |

| 2.6   | Specifications                |

## CHAPTER 3 INSTALLATION AND CONFIGURATION

| 3.1   | Introduction                     |

|-------|----------------------------------|

| 3.2   | Configuration                    |

| 3.3   | Installation                     |

| 3.3.1 | Power Connections                |

| 3.3.2 | Address and Priority Assignments |

| 3.3.3 | Installation Testing             |

| 3.4   | Cabling                          |

## CHAPTER 4 PROGRAMMING INFORMATION

| 4.1   | Scope                      |

|-------|----------------------------|

| 4.2   | Device Registers 4-1       |

| 4.3   | Interrupts 4-7             |

| 4.4   | Timing Considerations 4-8  |

| 4.4.1 | Receiver 4-8               |

| 4.4.2 | Transmitter                |

| 4.4.3 | Break Generation Logic 4-8 |

| 4.5   | Program Notes              |

| 4.6   | Program Example            |

|       |                            |

| CHAPTER 5 | DETAILED DESCRIPTION                                    |

|-----------|---------------------------------------------------------|

| 5.1       | Introduction                                            |

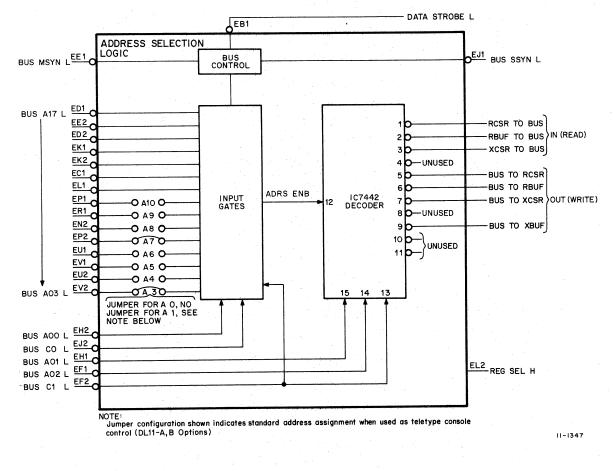

| 5.2       | Address Selection 5-2                                   |

| 5.2.1     | Inputs                                                  |

| 5.2.2     | Outputs                                                 |

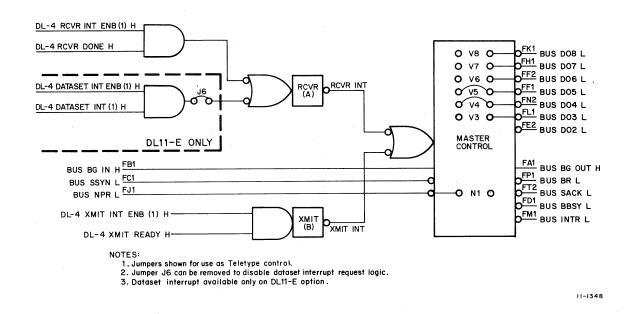

| 5.3       | Interrupt Control                                       |

| 5.4       | Registers 5-10                                          |

| 5.4.1     | Receiver Status Register (RCSR) 5-10                    |

| 5.4.1.1   | Dataset Interrupt Bit (15) 5-11                         |

| 5.4.1.2   | Dataset Status Bits (14, 13, 12, and 10) 5-12           |

| 5.4.1.3   | Receiver Done (07) 5-12                                 |

| 5.4.1.4   | Receiver Interrupt Enable (06) 5-13                     |

| 5.4.1.5   | Dataset Interrupt Enable (05)         5-13              |

| 5.4.1.6   | Secondary Transmit (03) 5-14                            |

| 5.4.1.7   | Request To Send (02) 5-14                               |

| 5.4.1.8   | Data Terminal Ready (01) 5-14                           |

| 5.4.1.9   | Reader Enable (00)         5-15                         |

| 5.4.2     | Receiver Buffer Register (RBUF) 5-15                    |

| 5.4.2.1   | Receiver Error Bits 5-16                                |

| 5.4.2.2   | Receiver Data Bits 5-16                                 |

| 5.4.3     | Transmitter Status Register (XCSR) 5-17                 |

| 5.4.3.1   | Transmitter Ready (07) 5-17                             |

| 5.4.3.2   | Transmitter Interrupt Enable (06) 5-18                  |

| 5.4.4     | Transmitter Buffer Register (XBUF) 5-18                 |

| 5.5       | Transmitter Control Logic 5-19                          |

| 5.6       | Receiver Control Logic                                  |

| 5.7       | Universal Asynchronous Receiver/Transmitter (UART) 5-21 |

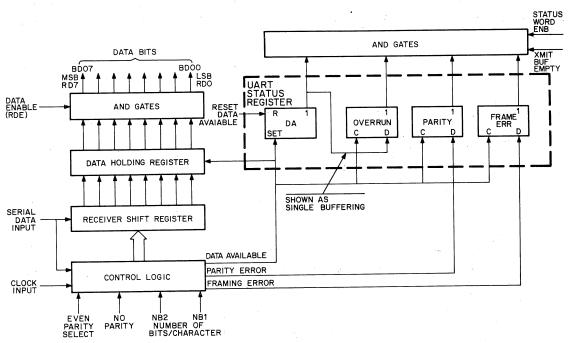

| 5.7.1     | Receiver Operation                                      |

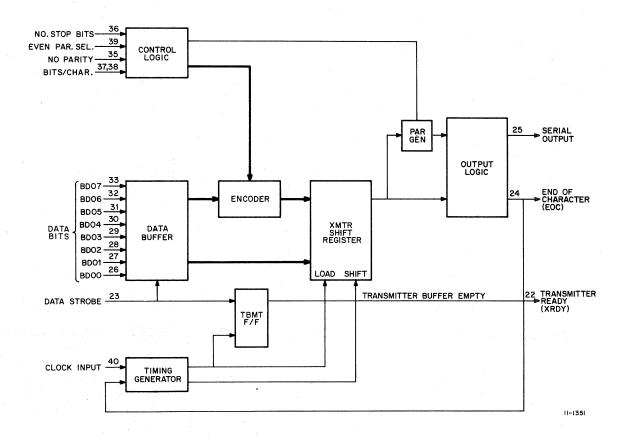

| 5.7.2     | Transmitter Operation                                   |

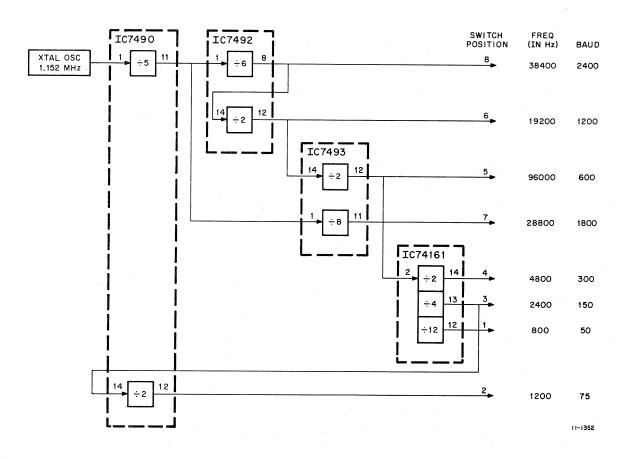

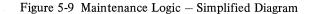

| 5.8       | Clock Logic                                             |

| 5.9       | Maintenance Mode Logic 5-26                             |

| 5.10      | Break Generation Logic 5-28                             |

|           |                                                         |

## APPENDIX A IC SCHEMATICS

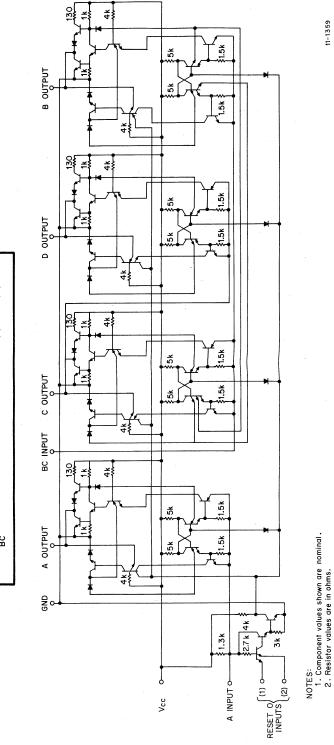

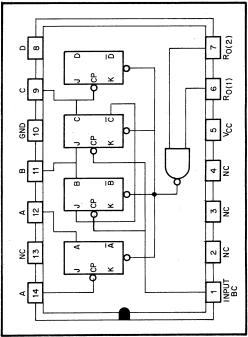

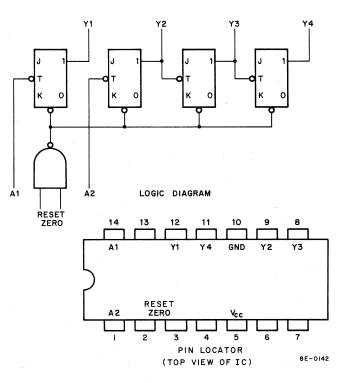

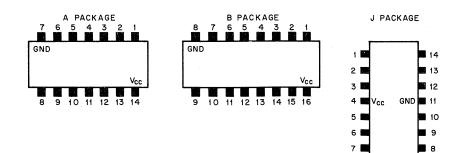

7490 Frequency Divider

7492 Frequency Divider

7493 Frequency Divider

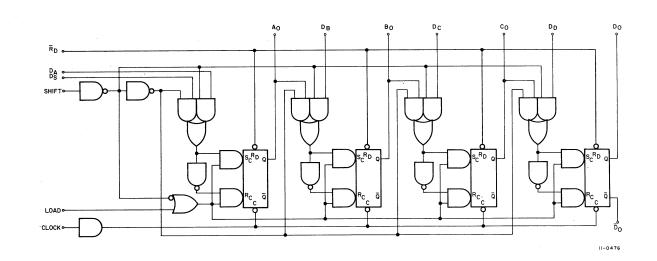

8271 4-Bit Shift Register

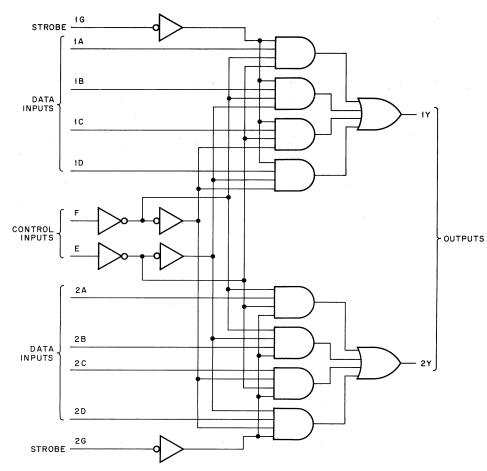

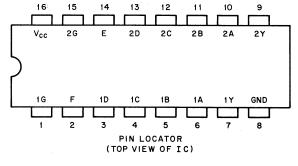

74153 4-Line To 1-Line Multiplexer

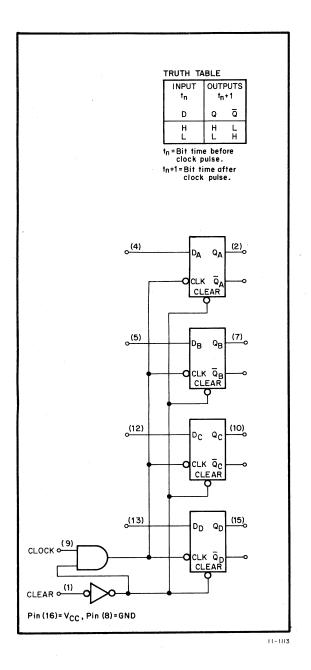

74175 Quad D-Type Flip-Flop

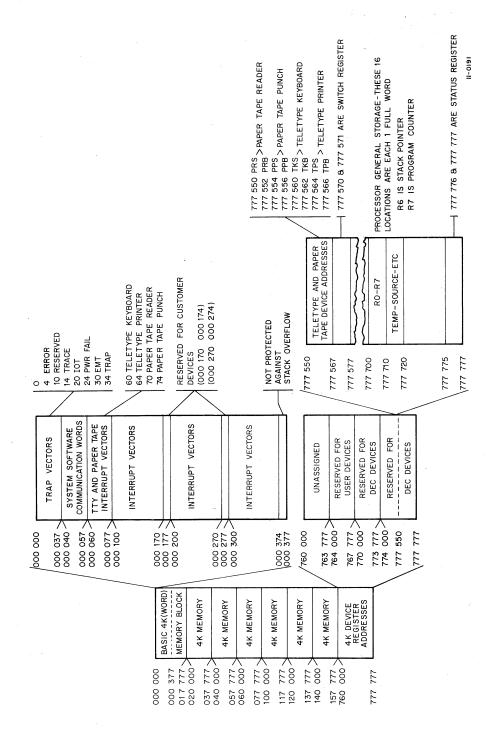

## APPENDIX B VECTOR ADDRESSING

| <b>B.</b> 1 | Introduction      | B-1        |

|-------------|-------------------|------------|

| B.2         | Interrupt Vectors | <b>B-2</b> |

## ILLUSTRATIONS

| Figure No. | Title Page                                                              |

|------------|-------------------------------------------------------------------------|

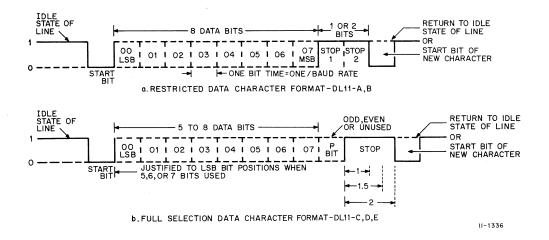

| 2-1        | DL11 Data Formats                                                       |

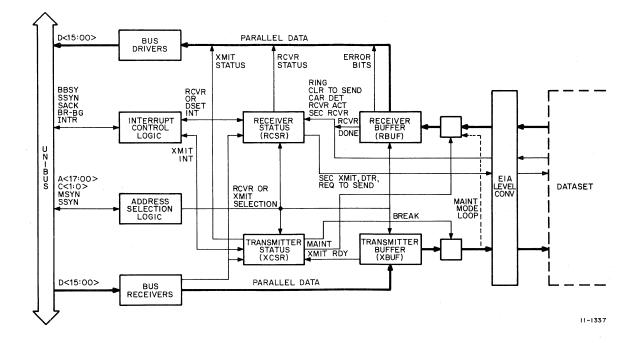

| 2-2        | DL11-E Block Diagram                                                    |

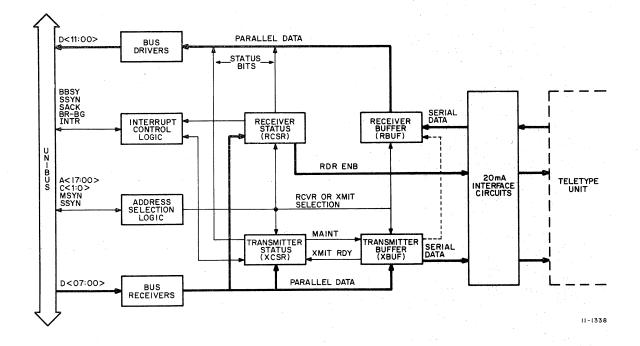

| 2-3        | DL11-A Block Diagram                                                    |

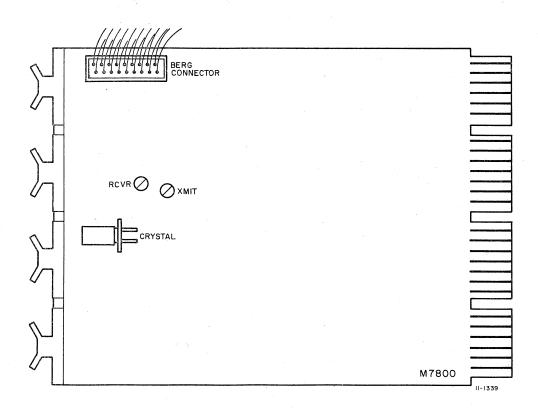

| 2-4        | Crystal and Switch Location                                             |

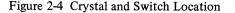

| 3-1        | DL11 (M7800 module) Mounted in DD11-A 3-2                               |

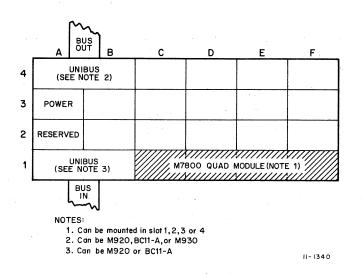

| 3-2        | Jumper Locations on the M7800 Module 3-4                                |

| 3-3        | DL11 Cable Connections 3-5                                              |

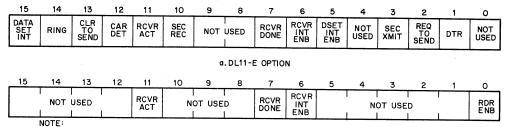

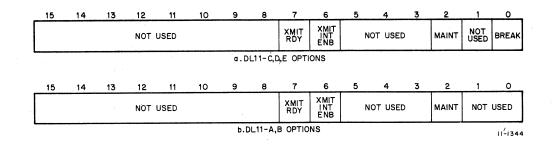

| 4-1        | Receiver Status Register (RCSR) – Bit Assignments                       |

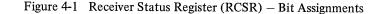

| 4-2        | Receiver Buffer Register (RBUF) – Bit Assignments                       |

| 4-3        | Transmitter Status Register (XCSR) – Bit Assignments                    |

| 4-4        | Transmitter Buffer Register (XBUF) – Bit Assignments                    |

| 5-1        | Address Selection Logic – Simplified Diagram 5-5                        |

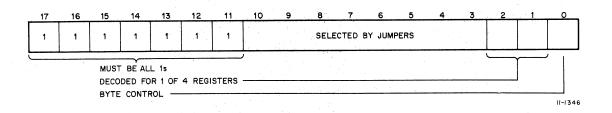

| 5-2        | Interface Select Address Format 5-5                                     |

| 5-3        | Interrupt Control Logic – Simplified Diagram                            |

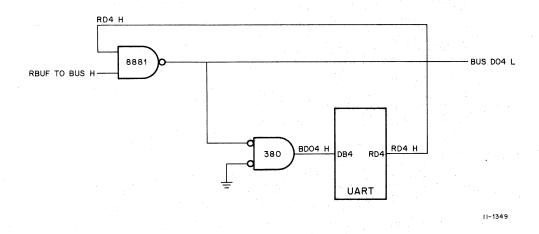

| 5-4        | RBUF and XBUF Gating Logic – Simplified Diagram (one bit position) 5-17 |

| 5-5        | UART Receiver – Block Diagram 5-23                                      |

| 5-6        | UART Transmitter – Block Diagram 5-24                                   |

| 5-7        | Frequency Divider Logic – Simplified Diagram 5-26                       |

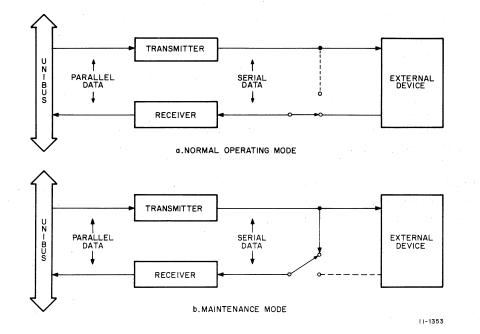

| 5-8        | Operating Modes 5-27                                                    |

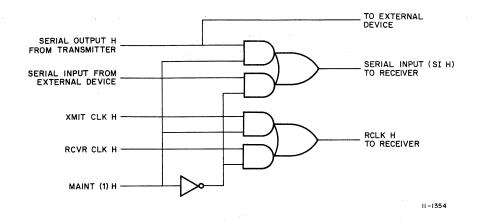

| 5-9        | Maintenance Logic – Simplified Diagram 5-28                             |

| B-1        | Address Map B-4                                                         |

## TABLES

## Table No.

≪3

## Title

Page

| 1-1 | Applicable PDP-11 Documents 1-2       |

|-----|---------------------------------------|

| 1-2 | Applicable Device Documents 1-3       |

| 2-1 | DL11 Options                          |

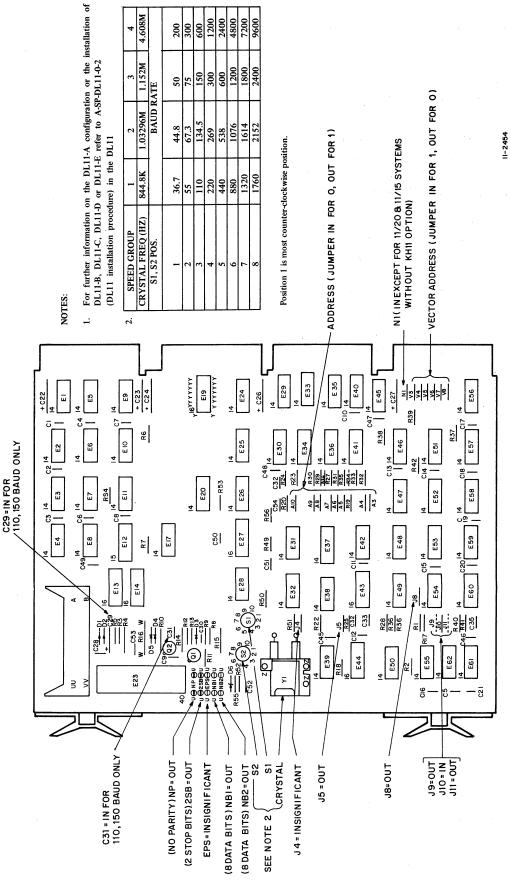

| 2-2 | Baud Rates with Standard Crystals 2-3 |

| 2-3 | Data Format Jumpers 2-5               |

| 2-4 | DL11 Operating Specifications 2-11    |

| 3-1 | Option Configurations 3-2             |

| 3-2 | Pin Connections                       |

| 3-3 | Input/Output Signals 3-7              |

| 3-4 | 7008360 Connections 3-7               |

| 3-5 | 7008519 Connections 3-8               |

| 3-6 | BC05C Connections 3-8                 |

| 4-1 | Standard DL11 Register Assignments 4-1 |

|-----|----------------------------------------|

| 5-1 | DL11 Functional Units 5-1              |

| 5-2 | DL11 Address Assignments 5-3           |

| 5-3 | Register Selection Signals 5-6         |

| 5-4 | DL11 Vectors and Priority Levels 5-7   |

| 5-5 | Device Register Functions 5-11         |

| 5-6 | Transmitter Control and Input Logic    |

| 5-7 | Receiver Status and Control Logic 5-21 |

|     |                                        |

# CHAPTER 1 INTRODUCTION

#### 1.1 INTRODUCTION

The DL11 Asynchronous Line Interface is a character-buffered communications interface designed to assemble or disassemble the serial information required by a communications device for parallel transfer to, or from, the PDP-11 Unibus. The interface consists of a single integrated circuit quad module containing two independent units (receiver and transmitter) capable of simultaneous 2-way communication.

The DL11 interface provides the logic and buffer register necessary for program-controlled transfer of data between a PDP-11 system requiring parallel data and an external device requiring serial data. The interface also includes status and control bits that may be controlled by the program, the interface, or the external device for command, monitoring, and interrupt functions.

Five available DL11 options (DL11-A through DL11-E) provide the flexibility needed to handle a variety of terminals. For example, the user can use a DL11-A as a Teletype<sup>®</sup> Control or a DL11-E for complete dataset control of communications datasets such as the Bell Model 103 or 202. Depending on the option used, the user has a choice of line speeds (baud rates), character size, stop-code length, parity selection, line control functions, and status indications.

Although each option uses an M7800 module, certain discrete component variations exist for each specific option so that the interface performs the intended function. Therefore, although generally similar, each option uses a slightly different M7800 variation which is not interchangeable with other options. These variations are installed at the factory only. For example, an M7800 used as a DL11-A could be used as another DL11-A but not in place of a DL11-B, C, D, or E.

A description of the individual options is given in Chapter 2 of this manual.

#### 1.2 SCOPE

This manual provides the user with the theory of operation and logic diagrams necessary to understand and maintain the DL11 Asynchronous Line Interface. The level of discussion assumes that the reader is familiar with basic digital computer theory.

1-1

<sup>®</sup> Teletype is a registered trademark of Teletype Corporation.

The manual is divided into five major chapters: Introduction, General Description, Installation and Configuration, Programming, and Theory of Operation. A complete set of engineering drawings is provided with each DL11 interface and is bound in a separate volume entitled *DL11 Asynchronous Line Interface, Engineering Drawings*.

In all cases, the information contained in this manual refers to all five options (DL11-A through DL11-E) unless specifically stated otherwise. Although control signals and data are transferred between the interface and the Unibus, and between the interface and the communications device, this manual is limited to coverage of only the interface itself.

Table 1-1 lists related PDP-11 system documents that are applicable to the DL11 Asynchronous Line Interface. Table 1-2 lists documents applicable to communications devices that may be used with the interface. Note that this latter table lists only representative manuals and is not intended to be an all-inclusive list.

| Title                                       | Number           | Description                                                                                                                                                                                                                                               |

|---------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PDP-11 System Manual                        |                  | Provides detailed theory of operation, flow, logic diagrams, operation, installation, and maintenance for components of the applicable PDP-11 system including processor, memory, console, and power supply.                                              |

| PDP-11 Peripherals Handbook                 |                  | Provides a discussion of the various peripherals used with PDP-11 systems. It also provides detailed theory, flow, and logic descriptions of the Unibus and external device logic; methods of interface construction; and examples of typical interfaces. |

| Paper-Tape Software<br>Programming Handbook | DEC-11-XPTSA-A-D | Provides a detailed discussion of the PDP-11 software<br>system used to load, dump, edit, assemble, and debug<br>PDP-11 programs; input/output programming and the<br>floating-point and math package.                                                    |

# Table 1-1Applicable PDP-11 Documents

| Tabl           | e 1-2          |

|----------------|----------------|

| Applicable Dev | rice Documents |

| Title                                                          | Number                                           | Description                                                                                                                                     |

|----------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Automatic Send-Receive<br>Sets, Manual                         | Bulletin 273B<br>(two volumes)<br>Teletype Corp. | Describes operation and maintenance of the Model 33 ASR<br>Teletype unit used as an input/output device.                                        |

| Model 33 Page<br>Printer Set, Parts                            | Bulletin 1184B<br>Teletype Corp.                 | Contains an illustrated parts breakdown to serve as a guide for disassembly, reassembly, and parts ordering for the Model 33 ASR Teletype unit. |

|                                                                |                                                  | NOTE                                                                                                                                            |

|                                                                | Comparable manuals as the Model 28, Mod          | exist for other available Teletypes such<br>lel 35, and Model 37.                                                                               |

| VT05 Alphanumeric<br>Display Terminal                          | EK-VT05-HR-002                                   | Describes purpose and operation of the VT05 Display used as an input/output device.                                                             |

| VT05 Alphanumeric<br>Display Terminal,<br>Maintenance Manuals, | EK-VT05-MM-005                                   | Provides detailed theory of operation and maintenance procedures for the VT05 Display.                                                          |

| VT06 Maintenance<br>Manual                                     | Datapoint Corp.                                  | Provides detailed theory of operation and maintenance data for<br>the VT06 Data Display Terminal.                                               |

| Bell System Data<br>Communications Data<br>Sets 103 E/G/H      |                                                  | Provides dataset interface specifications; includes dataset description and options including interface signals and timing.                     |

| Bell System Data<br>Communications Data<br>Sets 202 C/D        |                                                  | Provides dataset interface specifications; includes dataset description and options including interface signals and timing.                     |

#### **1.3 MAINTENANCE**

The basic maintenance philosophy of the DL11 Asynchronous Line Interface is to present the user with the information necessary to understand normal system operation. The user can utilize this information when analyzing trouble symptoms to determine necessary corrective action. A Modem Test Connector (Engineering Drawing D-CS-H315-0-1) can be used in troubleshooting the DL11.

#### 1.4 ENGINEERING DRAWINGS

A complete set of engineering drawings and circuit schematics is provided in a companion volume to this manual entitled *DL11 Asynchronous Line Interface*, *Engineering Drawings*. The following paragraphs describe the signal nomenclature conventions used on the drawing set.

Signal names in the DL11 print set are in the following basic form:

| <br>SOURCE | SIGNAL NAME | POLARITY |

|------------|-------------|----------|

| L          |             |          |

SOURCE indicates the drawing number of the print set where the signal originates. The drawing number of a print is located in the lower right-hand corner of the print title block (DL-1, DL-2, DL-3, etc.).

SIGNAL NAME is the name proper of the signal. The names used on the print set are also used in this manual for correlation between the two.

POLARITY is either H or L to indicate the voltage level of the signal: H means +3V; L means ground.

As an example, the signal:

DL-4 RCVR DONE H

originates on sheet 4 of the M7800 module drawing and is read, "when RCVR DONE is true, this signal is at +3V."

Unibus signal lines do not carry a SOURCE indicator. These signal names represent a bidirectional wire-ORed bus; as a result, multiple sources for a particular bus signal exist. Each Unibus signal name is prefixed with the word BUS.

Interface signals fed to, or received from, the Berg connector on the M7800 module are preceded by the pin number in parentheses:

(DD) EIA DATA TERMINAL READY

## CHAPTER 2 GENERAL DESCRIPTION

### 2.1 INTRODUCTION

The DL11 Asynchronous Line Interface is a character-buffered communications interface designed to translate serial bit stream data to parallel character data. The interface contains two independent units (receiver and transmitter) capable of simultaneous 2-way communication.

The five available DL11 options (DL11-A through DL11-E) provide the flexibility needed to handle a variety of terminals. For example, the user can select an option for interfacing a Teletype or display keyboard, for handling EIA data, or for handling dataset devices. In addition, depending on the option used, the user has a choice of line speeds, character size, stop-code length, and parity.

This chapter is divided into five major portions: available options, data format, functional description, physical description, and specifications.

#### 2.2 AVAILABLE OPTIONS

There are five available DL11 options: DL11-A through DL11-E. The major differences among these options are the data code, baud rates, and certain control and monitoring bits in the status registers. Although there are five options, they may be divided into the following functional groups:

| a. | Teletype<br>Control        | · | DL11-A<br>DL11-C | <br>   | The DL11-A and DL11-C both use a 20-mA current loop<br>for receive, transmit, and reader run operations necessary<br>for Teletype or display terminal control. |

|----|----------------------------|---|------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                            |   |                  |        | The DL11-C is simply a more flexible version of the DL11-A and includes data code and baud rate selection.                                                     |

| b. | EIA<br>Terminal<br>Control |   | DL11-B<br>DL11-D |        | The DL11-B and DL11-D both contain EIA drivers and receivers for compatability with the logic levels required for EIA terminals such as the VT06 display.      |

|    |                            |   |                  |        | The DL11-D is simply a more flexible version of the DL11-B and includes data code and baud rate selection.                                                     |

| c. | Data Set<br>Control        | _ | DL11-E           | -<br>- | The DL11-E provides complete data set control for communications modems such as Bell Model 103 or 202.                                                         |

A brief description of each of these options is included in Table 2-1 and a listing of available standard baud rates is given in Table 2-2. Note that these baud rates are based on the standard crystals supplied by DEC; however, the user may order special crystals, if desired. The physical differences of each option (cables, connectors, etc.) are described in Paragraph 2.5.

| Option | Data Code                        | Typical Use                                                     | Baud Rates                                              | Notes                                                                                                                                                                                     | Description                                                                                                                   |

|--------|----------------------------------|-----------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| DL11-A | Restricted <sup>(1)</sup>        | Model 33 or<br>35 Teletype<br>Model VT05<br>Display<br>Terminal | 110<br>150<br>300<br>600<br>1200<br>2400                | a. No dataset bits<br>a. No BREAK or<br>ERROR bits<br>c. No 1200/110 split                                                                                                                | Uses 20-mA current loop<br>operation for receive, transmit,<br>and reader run.                                                |

| DL11-B | Restricted <sup>(1)</sup>        | Model VT05<br>or VT06<br>Display<br>Terminal                    | Same as<br>DL11-A                                       | <ul> <li>a. No dataset bits</li> <li>b. No BREAK or<br/>ERROR bits</li> <li>c. No 1200/110<br/>split</li> <li>d. DATA TERM-<br/>INAL RDY and<br/>REQ TO SEND<br/>bits strapped</li> </ul> | Has EIA drivers and receivers<br>for compatability with EIA<br>terminals.                                                     |

| DL11-C | Full                             | Model 28                                                        | Crystal                                                 | on permanently<br>e. Null modem<br>usually re-<br>quired for<br>local EIA<br>terminal<br>a. No dataset bits                                                                               | Basically identical to DL11-A                                                                                                 |

|        | Selection <sup>(2)</sup>         | Teletype                                                        | and switch<br>select-<br>able <sup>(3)</sup>            | b. BREAK and<br>ERROR bits<br>enabled                                                                                                                                                     | except has full code and baud<br>rate selection. Also includes<br>both BREAK and ERROR bits.                                  |

| DL11-D | Full<br>Selection <sup>(2)</sup> | Model 37<br>Teletype<br>(null modem<br>required)                | Crystal<br>and switch<br>select-<br>able <sup>(3)</sup> | <ul> <li>a. No dataset bits</li> <li>b. BREAK and<br/>ERROR bits<br/>enabled</li> <li>c. DATA TERM-<br/>INAL RDY and<br/>REQ TO SEND<br/>bits strapped<br/>on permanently</li> </ul>      | Basically identical to DL11-B<br>except has full code and baud<br>rate selection. Also includes<br>both BREAK and ERROR bits. |

Table 2-1 DL11 Options

| Option | Data Code                        | Typical Use                   | Baud Rates                                              | Notes                      | Description                                                                                                                                                                           |

|--------|----------------------------------|-------------------------------|---------------------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DL11-E | Full<br>Selection <sup>(2)</sup> | Model 103<br>or 202<br>modems | Crystal<br>and switch<br>select-<br>able <sup>(3)</sup> | a. Full dataset<br>control | Provides complete dataset<br>control.<br>Dataset lines monitored by<br>this interface are: RING,<br>RECEIVE DATA, CARRIER<br>DETECT, CLEAR TO<br>SEND, and SECONDARY<br>RECEIVE DATA. |

|        |                                  |                               |                                                         |                            | Dataset lines controlled by<br>the program are: TRANS-<br>MITTED DATA, REQUEST<br>TO SEND, SECONDARY<br>TRANSMITTED DATA, and<br>DATA TERMINAL READY.                                 |

## Table 2-1 (Cont) DL11 Options

NOTES: 1. Restricted data code = 8 data bits, no partiy, 1 or 2 stop bits.

2. Full selection data code = 5, 6, 7, or 8 data bits; parity off, even, or odd; and 1, 1.5, or 2 stop bits.

3. Baud rates that may be selected by the crystal and switch are listed in Table 2-2.

| Switch<br>Position | Crystal #1<br>(844.8 kHz) | Crystal #2<br>(1.03296 MHz) | Crystal #3<br>(1.152 MHz) | Crystal #4<br>(4.608 MHz) |

|--------------------|---------------------------|-----------------------------|---------------------------|---------------------------|

| 1                  | 36.7                      | 44.8                        | 50                        | 200                       |

| 2                  | 55                        | 67.3                        | 75                        | 300                       |

| 3                  | 110                       | 134.5                       | 150                       | 600                       |

| 4                  | 220                       | 269                         | 300                       | 1200                      |

| 5                  | 440                       | 538                         | 600                       | 2400                      |

| 6                  | 880                       | 1076                        | 1200                      | 4800                      |

| 7                  | 1320                      | 1614                        | 1800                      | 7200                      |

| 8                  | 1760                      | 2152                        | 2400                      | 9600                      |

| 9*                 | _                         | _                           | -                         | -                         |

| 10*                | _                         |                             |                           | -                         |

Table 2-2Baud Rates with Standard Crystals

\*These switch positions are for external clock inputs and do not tap off the crystal oscillator.

NOTE: The baud rates in italics are the most commonly used.

#### 2.3 DATA FORMAT

There are two basic data formats used with the DL11 interface options. The first format (Figure 2-1,a) is referred to as "restricted" because the only variable is the number of STOP bits. A character in this format consists of a START bit, eight DATA bits, and one or two STOP bits. This code is used only with the DL11-A and DL11-B options.

The second format (Figure 2-1,b) is referred to as "full selection" because there is a number of variables. This format consists of a START bit, five to eight DATA bits, a PARITY bit or no PARITY bit, and one, one and one-half, or two STOP bits.

Figure 2-1 DL11 Data Formats

When less than eight DATA bits are selected in the second format, the hardware justifies the bits into the least significant bit positions for characters received by the interface. When transmitting characters, the program provides the justification into the least significant bits. The PARITY bit may be either on or off; when on, it can be selected for checking either odd or even parity during receive and for providing an extra PARITY bit during transmit.

All variable items within any data format are selected by jumpers on the DL11 module. None of the variables can be controlled by the program. Split lugs are provided on the module for installation of appropriate jumpers. These jumpers are listed in Table 2-3 and described more fully in Chapter 5.

Note that a jumper indicates a low (0) and no jumper indicates a high (1). The jumper locations are shown on DL11 drawing DL-4.

| Table 2-3           |  |

|---------------------|--|

| Data Format Jumpers |  |

| Name                | Jumper     | UART<br>Pin No. | Function                                                                                                                                                                                                  |  |

|---------------------|------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| No Parity           | NP         | 35              | Enables or disables the parity bit in the data character.                                                                                                                                                 |  |

|                     |            |                 | When enabled, the value of the parity bit is dependen<br>the type of parity (odd or even) selected by the oparity select (EPS) jumper.                                                                    |  |

|                     |            |                 | When disabled, the STOP bits immediately follow the las<br>DATA bit during transmission. During reception, the<br>receiver does not check for parity.                                                     |  |

|                     |            |                 | jumper – parity enabled<br>no jumper – parity disabled                                                                                                                                                    |  |

| Even Parity         | EPS        | 39              | Determines whether odd or even parity is to be used. The<br>receiver checks the incoming character for appropriate<br>parity; the transmitter inserts the appropriate parity value<br>jumper – odd parity |  |

|                     |            |                 | no jumper – even parity                                                                                                                                                                                   |  |

| STOP Bit            | 2SB        | 36              | Used in conjunction with three other jumpers (J9, J10 and J11) to select the desired number of STOP bits.                                                                                                 |  |

|                     |            |                 | 1 STOP bit – jumper in 2SB<br>jumper in J10<br>no jumpers in J9, J11                                                                                                                                      |  |

|                     |            |                 | 2 STOP bits – no jumper in 2SB<br>no jumpers in J9, J11<br>jumper in J10                                                                                                                                  |  |

|                     |            |                 | 1.5 STOP bits – jumper in 2SB<br>jumper in J9 or J11<br>no jumper in J10                                                                                                                                  |  |

| Number of Data Bits | NB1<br>NB2 | 38<br>37        | These two jumpers are used together to provide a cod<br>that selects the desired number of DATA bits in th<br>character.                                                                                  |  |

|                     |            |                 | Note that in the following code, a 0 indicates a jumper, 1 indicates no jumper:                                                                                                                           |  |

|                     |            |                 | NB2         NB1         No. of DATA Bits           0         0         5           0         1         6           1         0         7           1         1         8                                  |  |

)

(

2-5

#### 2.4 FUNCTIONAL DESCRIPTION

The DL11 is a character-buffered communications interface that performs two basic operations: receiving and transmitting asynchronous data. When receiving data, the interface converts an asynchronous serial character from an external device into the parallel character required for transfer to the Unibus. This parallel character can then be gated through the bus to memory, a processor register, or some other device. When transmitting data, a parallel character from the bus is converted to a serial line for transmission to the external device. Because the two data transfer units (receiver and transmitter) are independent, they are capable of simultaneous 2-way communication. The receiver and transmitter each operate through two related registers: a control and status register for command and monitoring functions, and a data buffer register for storing data prior to transfer to the bus or the external device.

Although there are actually five DL11 options, the prime functional differences can be shown by presenting three typical cases: a DL11 used for dataset devices, a DL11 used as a Teletype control, and a DL11 used with EIA level converters. Each of these three cases is covered separately in Paragraphs 2.4.1 through 2.4.3, respectively.

#### 2.4.1 DL11 Dataset Interface

Only the DL11-E (Figure 2-2) option can be used to interface to datasets. The DL11 uses call and acknowledge signals from the computer and the dataset, translates these signals to set up a handshaking sequence, and thus establish a data communication channel.

Figure 2-2 DL11-E Block Diagram

A typical method of establishing a data communication channel is as follows: the dataset at the computer is called by another remote dataset and a RING signal is transmitted to the DL11 interface. This RING signal initiates an interrupt provided the DATASET INT ENB bit in the DL11 register is set. The program then determines if the interrupt was caused by RING and, through a service routine, issues a DATA TERMINAL READY and a REQ TO SEND signal. These signals cause the dataset to answer the call and send a carrier signal or tone to the caller. The caller acknowledges the carrier signal with its own carrier signal which, when detected by the dataset, causes another interrupt (CARRIER) sequence to be initiated. Upon recognizing the CARRIER interrupt, the program can then either receive or transmit data. The only two prerequisites for the handshaking sequence are that the program use appropriate service routines and that the DATASET INT ENB bit in the DL11 status register is set prior to setting up the data channel.

Once the data channel is set up, the DL11-E receiver accepts incoming serial data from the dataset lines for parallel conversion and transfer to the Unibus. The transmitter converts parallel data from the bus and shifts the resultant serial data onto the dataset lines.

The receiver offers serial-to-parallel conversion of 5, 6, 7, or 8 level codes. This serial character code is described in Paragraph 2.3. Once the character has been received, a parity error flag, if selected, is available to the programmer for testing. An interrupt request (RCVR DONE flag) is initiated in the middle of the first STOP bit of the character being received. This indicates that the character is stored in the receiver holding register. If the program does not transfer the character from the holding register before the middle of the first STOP bit of the next character, a data overflow error (OR ERR) bit is set in the receiver buffer register. This buffer also provides other error indications such as framing error (FR ERR) which indicates that the character had no valid STOP bit, and partiy error (P ERR) which indicates that the received parity did not agree with the expected parity. It should be noted that both the receiver and transmitter character length and format are controlled by jumpers on the module and are always identical.

The transmitter performs parallel-to-serial conversion of 5, 6, 7, or 8 level codes. Data from the Unibus is loaded in parallel into the holding register. When the transmitter shift register is empty, the contents of the holding register is shifted into the transmitter shift register and the XMIT RDY flag comes up. A second character from the bus can then be loaded into the holding register. However, because the shift register is still working on previous data, the shifting operation of the second character is delayed until the previous character has been completely transmitted. Once the last bit of a character is transferred to the dataset (because of double-buffering, this is actually the last bit of the first character in a 2-character pair), the interface initiates an interrupt request (XMIT RDY) to indicate that the buffer is empty and can now be loaded with another character for transfer to the dataset. The transmitter status register contains a BREAK bit that can be set to transmit a continuous space to the dataset. A maintenance (MAINT) bit is also available for connecting the serial output of the transmitter to the input of the receiver and to force the receiver clock speed to be the same as the transmitter speed.

The rest of the control portion of the DL11-E is available through the receiver status register, and provides the necessary command and monitoring functions for use with Bell 103 and 202 type datasets. This register monitors such functions as: CLEAR TO SEND, which indicates the operating condition of the dataset; CAR DET, which indicates that the carrier is being received; RCVR ACT, which indicates that the receiver is accepting a character; and RCVR DONE, which indicates that a full character is stored in the receiver buffer.

Dataset interrupt requests are initiated at the transition of RING, CAR DET, CLR TO SEND, or SEC REC signals. The SEC REC (secondary or supervisory received data) and the SEC XMIT (secondary or supervisory transmitted data) bits provide receive and transmit capabilities for the reverse channel of a remote station. The DTR bit functions as a control lead for the dataset communication channel and permits the channel to be either connected or disconnected.

The DL11-E option contains EIA level converters for changing the bipolar inputs to TTL logic levels and the TTL logic level outputs to the bipolar signals required by the dataset. The EIA converters provide failsafe operation of the control leads because they appear off if the dataset loses power.

#### 2.4.2 DL11 Teletype Control

Both the DL11-A and DL11-C options can be used to interface Teletype units. The prime difference between the two is that the DL11-C can operate with a variable character format and is available in several different baud rates. The DL11-A option (Figure 2-3) is normally used to interface Model 33 and 35 Teletypes; the DL11-C option could be used to interface Model 28 Teletypes.

Figure 2-3 DL11-A Block Diagram

Serial information read or written by the Teletype unit is assembled or disassembled by the DL11 interface for parallel transfer to, or from, the Unibus. When the processor addresses the bus, the DL11 interface decodes the address to determine if the Teletype is the selected external device and, if selected, whether it is to perform an input (read) or output (punch) operation.

If, for example, the Teletype has been selected to accept information for printout, parallel data from the Unibus is loaded into the DL11 transmitter (punch) buffer. At this point, the XMIT RDY flag drops because the transmitter (punch) logic has been activated (the flag comes back after a fraction of a bit time if the transmitter is not presently active). The interface generates a START bit, shifts the data from the buffer into the Teletype one bit at a time, again sets the XMIT RDY flag (as soon as the holding register of the double-buffering is empty, even though the shift register is active), and then times out the required number of STOP bits.

Thus, if the DL11-A option is being used, the 8-bit parallel bus data is converted to the 11-bit serial input required by the Teletype. If the DL11-C option is used, the format and character length may be different, but the parallel-to-serial conversion is accomplished in the same manner. Note that whenever a series of characters is to be loaded into the Teletype, the XMIT RDY flag is set prior to generation of the STOP bits and the shifting out of the character in the holding register, thus allowing another character to be loaded from the bus as soon as the transmitter holding buffer is empty. The XMIT RDY flag is used to initiate an interrupt sequence to inform the processor that the interface is ready to transfer another character to the Teletype for printing.

When receiving data from the Teletype unit, the operation is essentially the reverse. The START bit of the Teletype serial data activates the interface receiver logic, and data is loaded one bit at a time into the reader buffer register. When loading of the buffer is complete, the buffer contents is transferred to the holding register and the interface sets the RCVR DONE flag, indicating to the program that a character has been assembled and is ready for transfer to the bus. The RCVR DONE flag, if RCVR INT ENB is also set, initiates an interrupt sequence, thereby causing a vectored interrupt.

The DL11-A and DL11-C options both have a reader enable (RDR ENB) bit that can be set to advance the paper-tape reader in the Teletype. When set, this bit clears the RCVR DONE flag. As soon as the Teletype sends another character, the START bit clears the RDR ENB bit, thus allowing just one character to be read.

The DL11-A and DL11-C options also have a receiver active (RCVR ACT) bit which indicates that the DL11 interface is receiving data from the Teletype. This bit is set at the center of the START bit, which is the beginning of the input serial data, and is cleared by the leading edge of the RCVR DONE bit. The DL11-C also has a BREAK bit which can be set by the program to transmit a continuous space to the Teletype.

The DL11-A and DL11-C options, as well as all other DL11 options, can be operated in a maintenance mode which is selected by the program by setting the MAINT bit in the transmitter status register. When in this mode, special logic is used to perform a closed loop test of interface logic circuits. A character from the bus is loaded in parallel into the transmitter (punch) buffer register. The serial output of this register, besides entering the Teletype, enters the receiver (reader) buffer register where it is converted back into parallel data and transferred to the bus. If the DL11 is functioning properly, the character in the reader buffer (RBUF) is identical to the character loaded into the transmitter buffer (XBUF).

#### 2.4.3 DL11 EIA Terminal Control

Both the DL11-B and DL11-D options provide the control logic required for interfacing EIA terminals such as the VT06 Display or the Model 37 Teletype. The prime difference between these two options is that the DL11-D can operate with a variable format and is available in several baud rates.

Functionally, the DL11-B and DL11-D operate in an identical manner to the DL11-A and DL11-C, respectively (Paragraph 2.4.2). However, both the DL11-B and DL11-D options have additional logic consisting of EIA level converters for changing bipolar inputs to TTL logic levels and for changing the TTL logic level outputs to the bipolar signals required by EIA terminals.

#### 2.5 PHYSICAL DESCRIPTION

The DL11 interface is packaged on a single M7800 Quad Intergrated Circuit Module that can easily be plugged into either a small peripheral controller slot in the processor or into one of the four slots in a DD11-A Peripheral Mounting Panel. When the DD11-A is used, up to four DL11 interfaces can be mounted in a single system unit.

Power is applied to the logic through the power harness already provided in the BA11 Mounting Box. The required current is approximately  $\overline{1.8A}$  at +5V and 150 mA at -15V. If one of the EIA options is used (DL11-B, D, or E), then 50 mA of current, at a level between +9V and +15V, is also required.

The M7800 module has a Berg connector for all user input/output signals. The specific signals fed to this connector depend on the particular option used. The signals transferred between the M7800 and the external device are dependent on the specific cable used with the selected option. Mounting, cabling, and connector information is given in Chapter 3.

The specific baud rate used with the DL11 interface is selected by a switch which taps off the frequency divider output of a crystal oscillator.

2-10

One of four available crystals (1.03296 MHz, 844.8 kHz, 1.152 MHz, or 4.608 MHz) is mounted on the M7800 module as shown on Figure 2-4. The user may use a different crystal if desired, but the DL11 operating speed is limited from 40 baud to 10K baud.

Figure 2-4 also shows the position of the two switches used to select the baud rate. Both switches are identical: one is used for the receiver portion of the interface, the other is used for the transmitter. Each switch is a 10-position rotary switch. Positions 9 and 10 are used to select an external clock. Positions 1 through 8 are used to select the baud rate from the crystal. The standard available baud rates selected by each switch position are listed in Table 2-2. A detailed description of the frequency division is given in Chapter 5 of this manual.

#### 2.6 SPECIFICATIONS

Operating and physical specifications for the DL11 Asynchronous Line Interface are given in Table 2-4. Unless otherwise specified in the table, the specifications refer to all five DL11 options.

| Specification                  | Options                         | Description                                                                                                                                                                                                                                        |

|--------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Registers                      | A11                             | Receiver Status Register(RCSR)Receiver Buffer Register(RBUF)Transmitter Status Register(XCSR)Transmitter Buffer Register(XBUF)                                                                                                                     |

| Register<br>Addresses          | DL11-A or<br>DL11-B             | RCSR 777560<br>RBUF 777562<br>XCSR 777564<br>XBUF 777566<br>When used as console                                                                                                                                                                   |

|                                |                                 | $ \left. \begin{array}{ccc} \text{RCSR} & 776XX0 \\ \text{RBUF} & 776XX2 \\ \text{XCSR} & 776XX4 \\ \text{XBUF} & 776XX6 \end{array} \right\} XX = 50 \text{ through 67 for up to} \\ 16 \text{ interfaces} \\ 16 \text{ interfaces} \end{array} $ |

|                                | DL11-C, D,<br>or E              | $ \left. \begin{array}{ccc} RCSR & 77XXX0 \\ RBUF & 77XXX2 \\ XCSR & 77XXX4 \\ XBUF & 77XXX6 \end{array} \right\} XXX = 561 \text{ through } 617 \text{ for up} \\ \text{to } 31 \text{ interfaces} \end{array} $                                  |

| Interrupt<br>Vector<br>Address | DL11-A or<br>DL11-B             | $\begin{array}{l} 060 = \text{Receiver} \\ 064 = \text{Transmitter} \end{array}  \text{when used as console} \end{array}$                                                                                                                          |

| Priority<br>Level              | All<br>DL11-A, B, C,<br>D, or E | Floating Vectors (Appendix B)<br>BR4 (may be changed by jumper plug)                                                                                                                                                                               |

# Table 2-4DL11 Operating Specifications

| Specification                                                                                                   | Options                                  | Description                                                              |

|-----------------------------------------------------------------------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------|

|                                                                                                                 |                                          | Transmitter Ready (XMIT RDY)                                             |

| Interrupt<br>Types                                                                                              | DL11-A, B,<br>C, or D                    | Receiver Done (RCVR DONE)                                                |

|                                                                                                                 | DL11-E                                   | Transmitter Ready (XMIT RDY)                                             |

|                                                                                                                 |                                          | Receiver Done (RCVR DONE)                                                |

|                                                                                                                 |                                          | Dataset Interrupt (DATASET INT) which is caused by one of the following: |

|                                                                                                                 |                                          | CAR DET (carrier detect)                                                 |

|                                                                                                                 |                                          | RCV ACT (receiver active)                                                |

|                                                                                                                 |                                          | SEC REC (secondary receiver)                                             |

|                                                                                                                 |                                          | RING (ringing signal)                                                    |

| Commands                                                                                                        | DL11-A, B                                | Receiver Interrupt Enable (RCVR INT ENB)                                 |

|                                                                                                                 |                                          | Transmitter Interrupt Enable (XMIT INT ENB)                              |

|                                                                                                                 |                                          | Reader Enable (RDR ENB)                                                  |

|                                                                                                                 |                                          | Maintenance Mode (MAINT)                                                 |

|                                                                                                                 | DL11-C, D                                | All of the above commands plus BREAK.                                    |

|                                                                                                                 | DL11-E                                   | All of the above commands plus the following com-                        |

|                                                                                                                 |                                          | mands:                                                                   |

|                                                                                                                 |                                          | Dataset Interrupt Enable (DATASET INT ENB)                               |

|                                                                                                                 |                                          | Secondary Transmit (SEC XMIT)                                            |

|                                                                                                                 |                                          | Request to Send (REQ TO SEND)                                            |

|                                                                                                                 |                                          | Data Terminal Ready (DTR)                                                |

| Status                                                                                                          | DL11-A, B                                | Receiver Active (RCVR ACT)                                               |

| Indications                                                                                                     |                                          | Transmitter Ready (XMIT RDY)                                             |

|                                                                                                                 |                                          | Receiver Done (RCVR DONE)                                                |

|                                                                                                                 | DL11-C, D                                | Same as DL11-A plus the following:                                       |

|                                                                                                                 |                                          | Error (ERROR)                                                            |

| in the second | an a | Overrun (OR ERR)                                                         |

|                                                                                                                 |                                          | Framing Error (FR ERR)                                                   |

|                                                                                                                 |                                          | Parity Error (P ERR)                                                     |

|                                                                                                                 | DL11-E                                   | Same as DL11-C plus the following:                                       |

|                                                                                                                 |                                          | Clear to Send (CLR TO SEND)                                              |

|                                                                                                                 |                                          | Carrier Detect (CAR DET)                                                 |

|                                                                                                                 |                                          | Secondary Receive (SEC REC)                                              |

|                                                                                                                 |                                          | Ring (RING)                                                              |

|                                                                                                                 |                                          |                                                                          |

Table 2-4 (Cont)DL11 Operating Specifications

| Specification            | Options            | Description                                                                                                                                                    |  |  |

|--------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Data Input<br>and Output | DL11-A, C          | Serial data, 20-mA active current loop.                                                                                                                        |  |  |

|                          | DL11-B, D          | Serial data, conforms to EIA and CCITT specifications.                                                                                                         |  |  |

|                          | DL11-E             | Serial data, EIA and CCITT specifications, compatible with Bell 103 and 202 datasets.                                                                          |  |  |

| Data Format              | DL11-A, B          | 1 START bit, 8-bit DATA character, 1 or 2 STOP bits.                                                                                                           |  |  |

|                          | DL11-C, D<br>or E  | 1 START bit; 5, 6, 7, or 8 bit DATA character;<br>PARITY bit (odd, even, or unused); 1, 1.5, or 2 STOP<br>bits.                                                |  |  |

| Data Rates               | DL11-A, B          | Baud rate restricted to 110, 150, 300, 600, 1200, and 2400. No 1200/110 split.                                                                                 |  |  |

|                          | DL11-C, D,<br>or E | Baud rate dependent on crystal used and switch position (Table 2-2).                                                                                           |  |  |

| Clock Rates              | DL11-A, B          | Crystal oscillator at one of two standard frequencies; 844.8 kHz or 1.152 MHz.                                                                                 |  |  |

|                          |                    | External clock can be connected to two switch position (9 and 10).                                                                                             |  |  |

|                          | DL11-C, D,<br>or E | Crystal oscillator at one of four standard frequencies: 1.03296 MHz, 844.8 kHz, 1.152 MHz, or 4.608 MHz.                                                       |  |  |

|                          |                    | External clock can be connected to two switch positions (9 and 10).                                                                                            |  |  |

|                          |                    | Special crystal frequencies can be ordered from DEC.                                                                                                           |  |  |

| Bit Transfer<br>Order    | All                | Low-order bit (LSB) first.                                                                                                                                     |  |  |

| Parity                   | DL11-C, D,<br>or E | Computed on incoming data or inserted on outgoing data dependent on type of parity (odd or even) used.                                                         |  |  |

|                          |                    | Parity may be odd, even, or unused.                                                                                                                            |  |  |

| Size                     | All                | Consists of a single quad module (M7800) that<br>occupies ¼ of a DD11-A or one of two controller slots<br>in a KA11, KC11, or other PDP-11 processor system un |  |  |

)

# Table 2-4 (Cont)DL11 Operating Specifications

| Specification     | Options            | Description                                                                                                                    |  |  |

|-------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|

| Cables            | DL11-A, C          | One 7008360 cable (2-ft length) with Berg connector<br>for mating to M7800 and female Mate-N-Lok for<br>mating to device.      |  |  |

|                   | DL11-B, D,<br>or E | One BC05C-25 (25-ft length) cable with Berg connector<br>for mating to M7800 and male Cinch connector for<br>mating to device. |  |  |

| Power<br>Required | DL11-A, C          | 1.8A at +5V<br>150 mA at -15V                                                                                                  |  |  |

|                   | DL11-B, D,<br>or E | 1.8A at +5V<br>150 mA at -15V<br>50 mA at level between +9V and +15V                                                           |  |  |

| Table 2-4 (Cont)                     |

|--------------------------------------|

| <b>DL11 Operating Specifications</b> |

# CHAPTER 3 INSTALLATION AND CONFIGURATION

#### 3.1 INTRODUCTION

This chapter describes the physical components which constitute each of the five DL11 Asynchronous Line Interface options, and methods of mounting and connecting the DL11 to other devices. The chapter is divided into three major parts: configuration, installation, and cabling.

#### 3.2 CONFIGURATION

Each DL11 option basically consists of an M7800 quad module, either a standard crystal (one of four available from DEC) or a special crystal (also available from DEC), and associated cabling. The specific components of each of the five options are listed in Table 3-1.

Although general operation of the M7800 is similar for each option, specific functions of this module differ from option to option. This is due partially to the jumpers which may be added to or removed from the logic to enable or disable certain signals, partially due to the specific cable used with the module which may or may not connect all lines between the module and the external device, and partially due to the addition or deletion of certain discrete components on the module so that the M7800 can perform the logic functions required for a particular option. In effect, there are five different versions of the M7800.

The crystals covered in Table 3-1 are the standard crystals available from DEC. The customer may substitute a special crystal, if desired. However, the resultant baud rate must remain within the range of 40 baud to 10K baud. Derivation of baud rates from the crystal oscillator frequency divider logic is described in Chapter 5.

#### 3.3 INSTALLATION

The DL11 interface can be mounted in either a small peripheral controller slot in the PDP-11 processor or in one of the four slots in a DD11-A Peripheral Mounting Panel as shown in Figure 3-1. Note that the DL11 can be mounted in any one of the four slots and up to four DL11 interfaces can be mounted in a single system unit.

A DL11 interface can also be mounted in one of the four slots of a BB11 system unit, provided that slot has been wired as a DD11-A or equivalent. Once the M7800 module has been installed, the appropriate cable must be connected as described in Paragraph 3.4.

| Option | Module | Cables                | Crystal              | Notes                                                 |

|--------|--------|-----------------------|----------------------|-------------------------------------------------------|

| DL11-A | M7800  | 7008360<br>(2-1/4 ft) | #1 or #3<br>only     | Cable mates to Model 33 or Model 35 Teletype.         |

| DL11-B | M7800  | BC05C-25<br>(25 ft)   | #1 or #3<br>only     |                                                       |

| DL11-C | M7800  | 7008360<br>(2-1/4 ft) | #1, #2, #3,<br>or #4 |                                                       |

| DL11-D | M7800  | BC05C-25<br>(25 ft)   | #1, #2, #3,<br>or #4 | Model 37 Teletype, VT05, or VT06 null modem required. |

| DL11-E | M7800  | BC05C-25<br>(25 ft)   | #1, #2, #3,<br>or #4 | Cable mates to Bell 103 or 202 modem.                 |

Table 3-1Option Configurations

NOTES: 1. Crystal frequencies are: #1 = 844.8 kHz

#2 = 1.03296 MHz#3 = 1.152 MHz

#4 = 4.608 MHz

2. Although each option uses an M7800 module, the signals supplied on the specific module depend on the option used.

Figure 3-1 DL11 (M7800 module) Mounted in DD11-A

#### **3.3.1** Power Connections

Power connections to the DL11 interface are provided by the associated PDP-11 system via the power supply in the BA11 mounting box. When power is applied to the PDP-11 system, the DL11 receives power also. These power connections are described in detail in the *PDP-11 Peripherals Handbook*.

When using the DL11-B, D, or E option, a positive voltage is required between 9 and 15V to operate the EIA drivers. For PDP-11/15 and PDP-11/20 systems with an H720 Power Supply, a G8000 module must be installed to provide this voltage. This module uses a filter network to convert the full-wave rectified +8V/rms signal to a positive dc voltage. Installation of the G8000 module is performed as follows:

- 1. Install the G8000 module into slot A02 of the DD11-A.

- 2. Connect a wire between A03V2 and A02V2.

- 3. Connect a wire between A02N2 and CXXU1 where XX is the slot location of the M7800 module.

#### 3.3.2 Address and Priority Assignments

The DL11 interface is addressed through the address selection logic and its interrupt vector determined by the interrupt control logic. Each specific DL11 interface has a unique address and vector, both determined by jumpers on the M7800 module. Figure 3-2 shows the locations of the jumpers on the M7800 module. The addressing scheme is described in Paragraph 5.2 and the vector address (interrupt control) scheme is covered in Paragraph 5.3. The priority level is determined by the priority plug on the module and is normally a BR4 level for options DL11-A through DL11-D (refer to Engineering Drawing C-IA-5408776-0-0). However, this priority level may be changed, if desired, by changing the priority plug.

#### 3.3.3 Installation Testing

Installation testing is performed by running the appropriate diagnostic program after the DL11 interface has been completely installed. This program is contained on the diagnostic tape supplied with the interface. Instructions for running the diagnostic are included with the program tape.

Depending on the option used, the following diagnostic programs are supplied:

a. DL11-A option

b. DL11-B option

c. DL11-C option

d. DL11-D option

e. DL11-E option

KL11 Teletype Tests VT05 Tests Off-Line Test Off-Line Test Off-Line Test On-Line Test MAINDEC-11-DZKLA MAINDEC-11-DZVTB MAINDEC-11-DZDLA MAINDEC-11-DZDLA MAINDEC-11-DZDLA MAINDEC-11-DZDLB

#### 3.4 CABLING

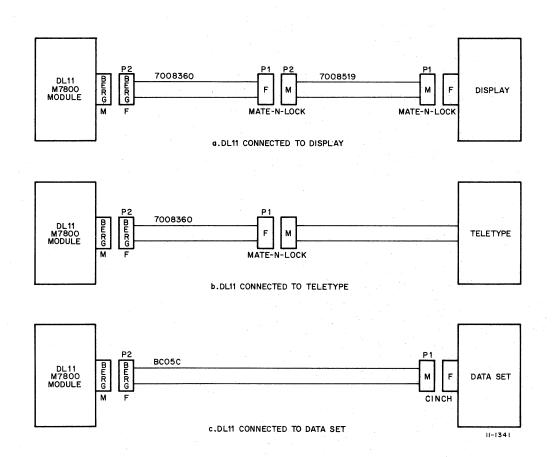

Figure 3-3 illustrates the method of connecting cables between the various DL11 options and associated external devices.

Table 3-2 lists the signal names and associated pins on the Berg connector mounted on the M7800 module. This table also lists the associated signals supplied on the 7008360 and BC05C cables.

DL11-A

4.608M

600

300

2400 4800 7200 9600

Figure 3-2 Jumper Locations on the M7800 Module

Table 3-3 provides a quick reference of M7800 input/output signals for TTL, EIA, and 20-mA current loop devices.

Table 3-4 lists connector pin numbers and signals for the 7008360 cable.

Table 3-5 lists connector pin numbers and signals for the 7008519 cable connector which is used in conjunction with the 7008360 cable.

Table 3-6 lists connector pin numbers for the BC05C cable connectors.

Figure 3-3 DL11 Cable Connections

| Berg<br>Pin | M7800 Module            | BC05C Modem Cable    | 7008360 Cable      |

|-------------|-------------------------|----------------------|--------------------|

| Α           | Ground                  | Ground               | Ground             |

| В           | Ground                  | Ground               |                    |

| С           | Force Busy (EIA)        | Force Busy           |                    |

| D           |                         | Sec. Clear to Send   |                    |

| E           | Serial Input (TTL)      | Interlock In         | Interlock In       |

| F           | Serial Output (EIA)     | Transmitted Data     |                    |

| н           | 20 mA Interlock         |                      | Interlock Out      |

| J           | Serial Input (EIA)      | Received Data        |                    |

| K           | Serial Input + (20 mA)  |                      | Received Data +    |

| L           |                         | External Clock       |                    |

| M           | EIA Interlock           | Interlock Out        |                    |

| N           |                         | Serial Clock Xmit    |                    |

| <b>)</b>    |                         | Sec. Request to Send |                    |

| R           |                         | Serial Clock Rcvr    |                    |

| S           | Serial Input - (20 mA)  |                      | Received Data -    |

| Г           | Clear to Send (EIA)     | Clear to Send        | Received Bata      |

| J.          |                         |                      |                    |

| V           | Request to Send (EIA)   | Request to Send      |                    |

| W           |                         | - Power              |                    |

| X           | Ring (EIA)              | Ring                 |                    |

| Y .         |                         | + Power              |                    |

| 7           |                         | Data Set Ready       |                    |

| ΑA          | Serial Output + (20 mA) | Dutu Set Ready       | Transmitted Data + |

| 3B          | Carrier (EIA)           | Carrier              | Transmitted Data   |

| CC          | Clock Input (TTL)       |                      |                    |

| DD          | Data Terminal Rdy (EIA) | Data Terminal Ready  |                    |

| ΞE          | Reader Run - (20 mA)    | Data Terminar Ready  | Reader Run -       |

| FF          | Secondary Xmit (EIA)    | 202 Sec. Xmit        | Reduct Rull -      |

| ŦH          | Berg Clock Enb          | 202 Sec. Allit       |                    |

| J           | Secondary Rec (EIA)     | 202 Sec. Rcvr        |                    |

| KK          | Serial Output - (20 mA) | 202 500. ROM         | Transmitted Data - |

|             | Soma Output - (20 mA)   | EIA Sec. Xmit        | Tansinitteu Data - |

| MM          | 2004 - C                | Signal Quality       |                    |

| NN          |                         |                      |                    |

| PP          | Reader Run + (20 mA)    | EIA Sec. Rcvr        | Reader Run +       |

| RR          |                         | Signal Rate          | Reauer Kun +       |

| SS          | Serial Output (TTL)     | Signal Kate          |                    |

| IT          | +5V                     |                      |                    |

|             | Ground                  | Cround               | Carry              |

| JU          |                         | Ground               | Ground             |

| vv          | Ground                  | Ground               | Ground             |

Table 3-2Pin Connections

| Туре          |         | Signals                             | Pin No. |

|---------------|---------|-------------------------------------|---------|

| TTL Signals   | INPUT:  | Serial Data                         | E       |

|               |         | Clock                               | CC      |

|               |         | Clock Enable                        | HH      |

|               | OUTPUT: | Serial Data                         | SS      |

| 20-mA Current | INPUT:  | + Serial Data                       | K       |

| Loop Signals  |         | - Serial Data                       | S       |

|               | OUTPUT: | + Serial Data                       | AA      |

|               |         | - Serial Data                       | KK      |

|               |         | + Reader Run (RDR ENB)              | PP      |

|               |         | - Reader Run $\int_{0}^{(RDR ENB)}$ | EE      |

| EIA Signals   | INPUT:  | Serial Data                         | J       |

|               |         | Clear to Send                       | T       |

|               |         | Ring                                | X       |

|               |         | Carrier                             | BB      |

|               |         | Secondary Receive                   | JJ      |

|               | OUTPUT: | Serial Data                         | F       |

|               |         | Force Busy                          | C       |

|               |         | Request to Send                     | V       |

|               |         | Data Terminal Ready                 | DD      |

|               |         | Secondary Transmit                  | FF      |

Table 3-3Input/Output Signals

Table 3-47008360 Connections

| Twisted Pair | Color | Mate-N-Lok<br>Connector P1<br>(To Device) | Berg<br>Connector P2<br>(To DL11)            | Signal                        |

|--------------|-------|-------------------------------------------|----------------------------------------------|-------------------------------|

| Black/Red    | Black | 2                                         | КК                                           | - Transmitted Data            |

|              | Red   | 3                                         | S                                            | - Received Data               |

| Black/White  | Black | 4                                         | EE                                           | - Reader Run                  |

|              | White | 5                                         | AA                                           | + Transmitted Data            |

| Black/Green  | Black | 6                                         | PP                                           | + Reader Run                  |

|              | Green | · · 7 · ·                                 | K                                            | + Received Data               |

|              |       |                                           | $black \begin{bmatrix} E \\ H \end{bmatrix}$ | Interlock In<br>Interlock Out |

NOTES: 1. Connector on ASR Teletype uses all pins (2-7).

2. Connector on KSR Teletype does not use pins 4 or 6 (Reader Run - and +).