# DHV11 Technical Manual

# DHV11 Technical Manual

Prepared by Educational Services of Digital Equipment Corporation

# Copyright © 1983 by Digital Equipment Corporation All Rights Reserved

The information in this document is subject to change without notice. Digital Equipment Corporation assumes no responsibility for any errors herein.

#### Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation.

|     |   |    |   | Th |

|-----|---|----|---|----|

| d i | g | jį | а |    |

|     |   |    |   |    |

DIBOL

**DEC MASSBUS UNIBUS DEC**mate **PDP** VAX P/OS DECsystem-10 **VMS DECSYSTEM-20** Professional VT **DECUS** Rainbow **RSTS DECwriter** Work Processor

**RSX**

## CONTENTS

| CHAPTER 1    | INTRODUCTION                            | Page |

|--------------|-----------------------------------------|------|

|              |                                         |      |

| 1.1          | SCOPE                                   | 1-1  |

| 1.2          | OVERVIEW                                | 1-1  |

| 1.2.1        | General Description                     | 1-1  |

| 1.2.2        | Physical Description                    |      |

| 1.2.3        | Versions of DHV11                       | 1-4  |

| 1.2.4        | Configurations                          |      |

| 1.2.5        | Connections                             |      |

| 1.3          | SPECIFICATION                           |      |

| 1.3.1        | Environment Conditions                  |      |

| 1.3.2        | Electrical Requirements                 |      |

| 1.3.3        | Performance                             |      |

| 1.3.3.1      | Data Rates                              |      |

| 1.3.3.2      | Throughput                              |      |

| 1.4          | INTERFACES                              |      |

| 1.4.1        | System Bus Interface                    |      |

| 1.4.1        | Serial Interfaces                       | 1 Q  |

| 1.4.2.1      | Interface Standards                     |      |

|              | Serial Data Format.                     | 1 10 |

| 1.4.2.2      | Senai Data Format                       | 1-10 |

| 1.4.2.3      | Line Receivers                          |      |

| 1.4.2.4      | Line Transmitters                       | 1-11 |

| 1.4.2.5      | Speed/Distance Considerations           | 1-11 |

| 1.5          | FUNCTIONAL DESCRIPTION                  | 1-12 |

| 1.5.1        | Control Function                        | 1-12 |

| 1.5.2        | Q-Bus Interface                         | 1-12 |

| 1.5.3        | Serial Interfaces                       | 1-12 |

| CHAPTER 2    | INSTALLATION                            |      |

| CHAITER 2    |                                         |      |

| 2.1          | SCOPE                                   | 2-1  |

| 2.2          | UNPACKING AND INSPECTION                |      |

| 2.3          | INSTALLATION CHECKS                     |      |

| 2.3.1        | Address Switches                        |      |

| 2.3.2        | Vector Switches                         |      |

| 2.3.2        | Backplane                               |      |

| 2.3.3.1      | Connection to the Q-Bus                 |      |

| 2.3.3.2      | Bus Grant Continuity Jumpers            | 2-5  |

|              | PRIORITY SELECTION                      |      |

| 2.4<br>2.4.1 | DMA Request                             |      |

|              |                                         |      |

| 2.4.2        | Interrupt Request                       |      |

| 2.5          | MODULE INSTALLATION                     |      |

| 2.6          | CABLES AND CONNECTORS                   |      |

| 2.6.1        | Distribution Panel                      | 2-9  |

| 2.6.2        | Staggered Loopback Test Connector H3277 |      |

| 2.6.3        | Line Loopback Test Connector H325       |      |

| 2.6.4        | Null Modem Cables                       |      |

| 2.6.5        | Full Modem Cables                       |      |

| 2.6.6        | Data Rate to Cable Length Relationships | 2-16 |

| 2.7          | MULTIPLE COMMUNICATIONS OPTIONS         |      |

| 2.7.1        | Floating Device Addresses               | 2-16 |

| 2.7.2<br>2.8 | Floating Vectors                                     | 2-22 |

|--------------|------------------------------------------------------|------|

| 2.8.1        | Installation Tests                                   | 2-22 |

| CHAPTER 3    | PROGRAMMING                                          |      |

| 3.1          | SCOPE                                                | 3-1  |

| 3.2          | REGISTERS                                            |      |

| 3.2.1        | Register Access                                      | 3_1  |

| 3.2.2        | Register Bit Definitions                             | 3_3  |

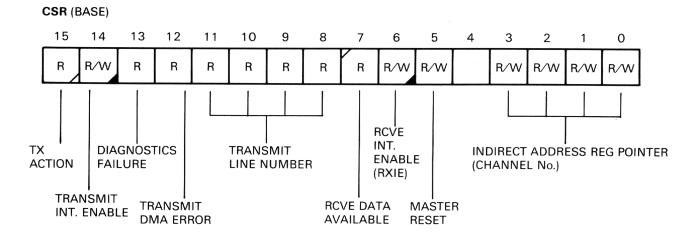

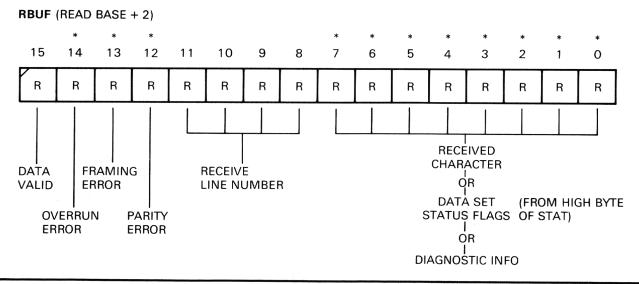

| 3.2.2.1      | Control and Status Register (CSR)                    | 3_1  |

| 3.2.2.2      | Receive Buffer (RBUF)                                | 3 6  |

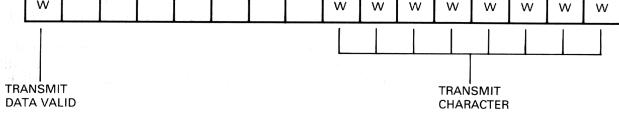

| 3.2.2.3      | Transmit Character Register (TXCHAR)                 | 2 0  |

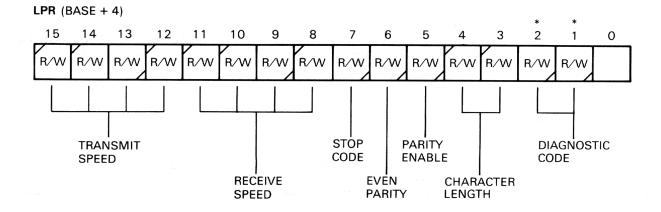

| 3.2.2.4      | Line Parameter Register (LPR)                        | 3-0  |

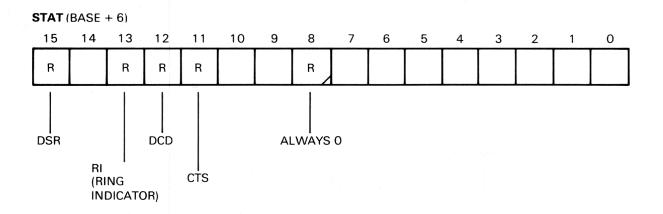

| 3.2.2.5      | Line Status Register (STAT)                          | 3-0  |

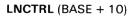

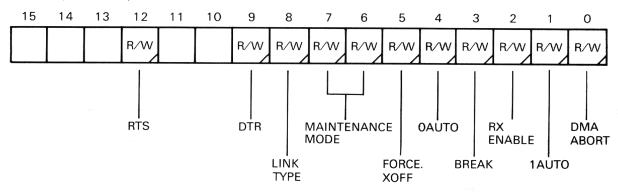

| 3.2.2.6      | Line Control Register (LNCTRL).                      | 3-11 |

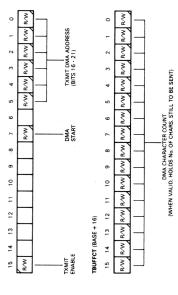

| 3.2.2.7      | Transmit Duffer Address Desister Number 1 (TDIETAD1) | 3-12 |

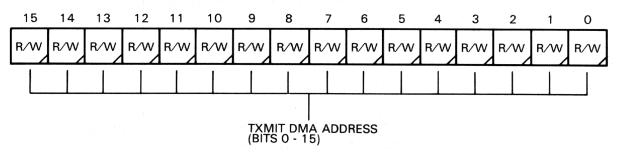

| 3.2.2.8      | Transmit Buffer Address Register Number 1 (TBUFFAD1) | 3-15 |

| 3.2.2.9      | Transmit Buffer Address Register Number 2 (TBUFFAD2) | 3-15 |

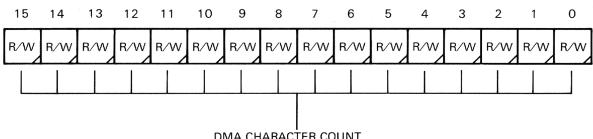

| 3.2.2.9      | Transmit DMA Buffer Counter (TBUFFCT)                | 3-16 |

|              | PROGRAMMING FEATURES                                 |      |

| 3.3.1        | Initialization                                       |      |

| 3.3.2        | Configuration                                        |      |

| 3.3.3        | Transmitting                                         |      |

| 3.3.3.1      | DMA Transfers                                        |      |

| 3.3.3.2      | Single Character Programmed Transfers                |      |

| 3.3.3.3      | Methods of Control                                   |      |

| 3.3.4        | Receiving                                            | 3-19 |

| 3.3.5        | Interrupt Control                                    | 3-19 |

| 3.3.6        | Auto X-ON and X-OFF                                  | 3-19 |

| 3.3.7        | Error Indication                                     |      |

| 3.3.8        | Modem Control                                        |      |

| 3.3.9        | Maintenance Programming                              | 3-22 |

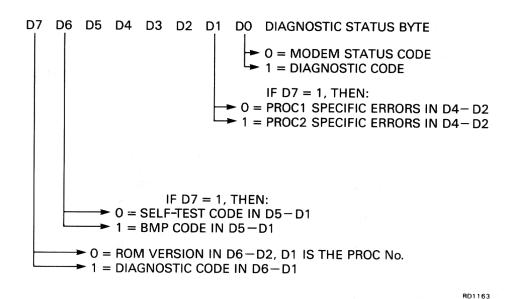

| 3.3.10       | Diagnostic Codes                                     |      |

|              | Self-Test Diagnostic Codes                           |      |

| 3.3.10.2     | Interpretation of Self-Test Codes                    | 3.22 |

| 3.3.10.3     | Skipping Self-Test                                   | 3 22 |

| 3.3.10.4     | Background Monitor Program (BMP)                     | 3 24 |

| 3.4          | PROGRAMMING EXAMPLES                                 | 3 24 |

| 3.4.1        | Resetting the DHV11                                  | 3 24 |

| 3.4.2        | Configuration                                        | 3 25 |

| 3.4.3        | Transmitting                                         | 2 26 |

| 3.4.3.1      | Single Character Programmed Transfer                 | 3-20 |

| 3.4.3.2      |                                                      |      |

| 3.4.3.3      | DMA Transfer                                         | 3-21 |

| 3.4.4        | Aborting a DMA Transfer                              | 3-28 |

| 3.4.5        | Receiving                                            | 3-28 |

| 3.4.6        | Auto X-ON and X-OFF                                  | 3-29 |

| 3.4.7        | Checking Diagnostic Codes                            | 3-30 |

| 3.4.7        | Modem Control                                        | 3-31 |

| CHAPTER 4    | TECHNICAL DESCRIPTION                                |      |

| 4.1          | SCOPE                                                | 4-1  |

| 4.2          | Q-BUS INTERFACE                                      | 4-1  |

| 4.3       | SERIAL INTERFACES                               | 4-6  |

|-----------|-------------------------------------------------|------|

| 4.3.1     | Modem Control and Status Lines                  | 4-6  |

| 4.3.2.    | EIA/TTL Level Conversion                        | 4-6  |

| 4.4       | CONTROL SECTION                                 | 4-6  |

| 4.4.1     | General                                         | 4-6  |

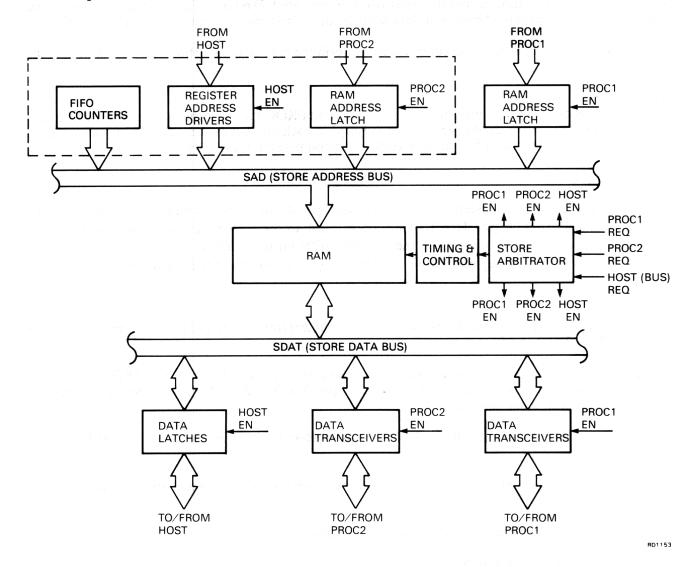

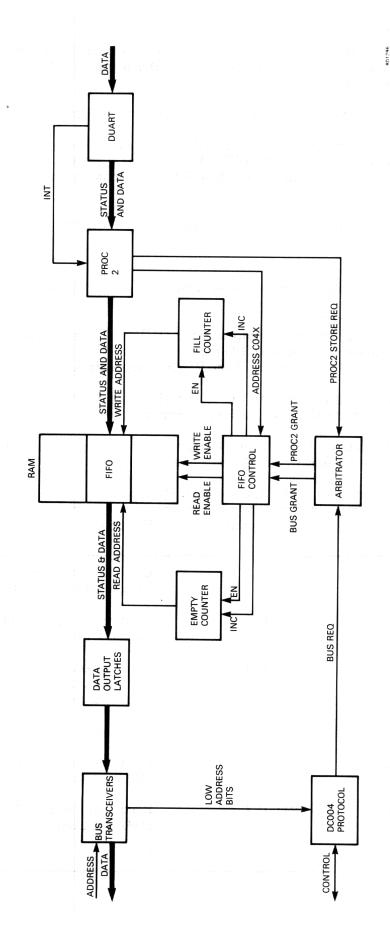

| 4.4.2     | Common RAM                                      | 4-7  |

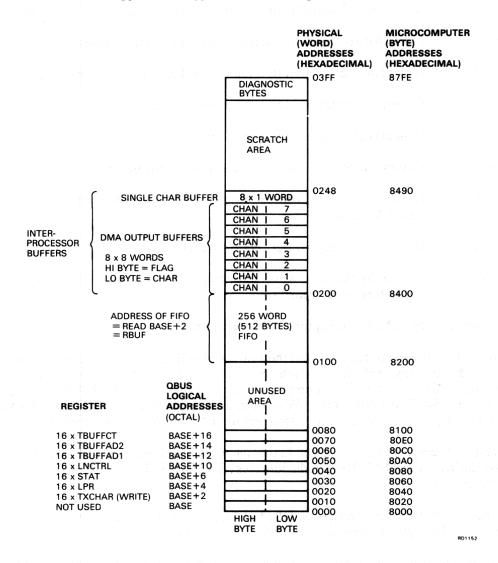

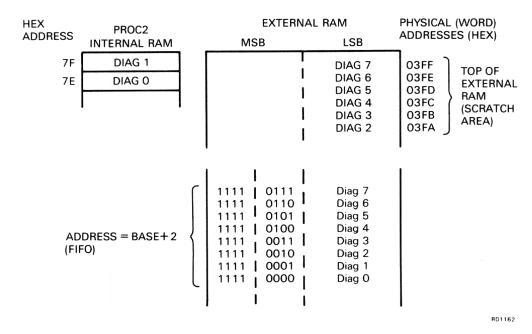

| 4.4.2.1   | Memory Map                                      | 4-7  |

| 4.4.2.2   | Registers                                       | 4-8  |

| 4.4.2.3   | FIFO                                            | 4-8  |

| 4.4.3     | RAM Access                                      | 4-9  |

| 4.4.4     | Store Arbitrator                                | 4-10 |

| 4.4.5     | Microcomputers                                  | 4-10 |

| 4.4.6     | Address and Data Latches                        | 4-10 |

| 4.4.7     | FIFO Addresses                                  | 4-11 |

| 4.4.8     | FIFO Control                                    | 4-11 |

| 4.5       | OTHER CIRCUITS                                  | 4-11 |

| 4.5.1     | Voltage Converter                               | 4-11 |

| 4.5.2     | Oscillators                                     | 4-11 |

| 4.6       | DATA FLOW                                       | 4-11 |

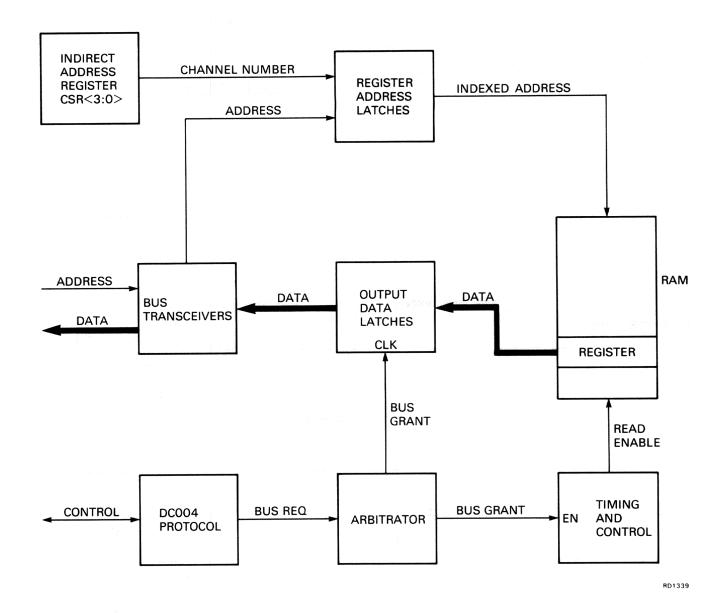

| 4.6.1     | Host Read from a Register                       | 4-12 |

| 4.6.2     | Writing to a Register                           | 4-13 |

| 4.6.3     | Single-Character Transmit                       | 4-14 |

| 4.6.4     | DMA Transmissions                               | 4-15 |

| 4.6.4.1   | DMA Block Transmit                              | 4-17 |

| 4.6.4.2   | DMA Data Management                             | 4-17 |

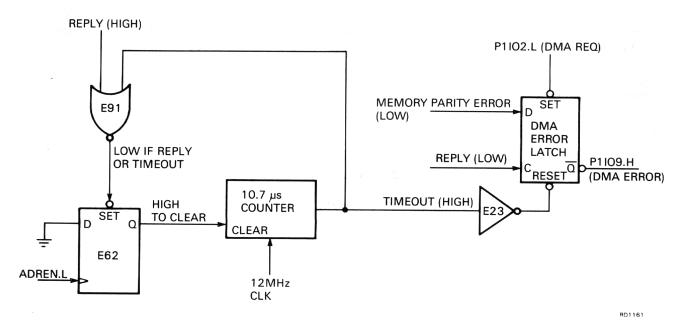

| 4.6.4.3   | DMA Error Detection and Timeout                 | 4-17 |

| 4.6.4.4   | DMA Abort                                       | 4-18 |

| 4.6.5     | Receiving                                       | 4-18 |

| 4.7       | TECHNICAL DETAIL                                | 4-20 |

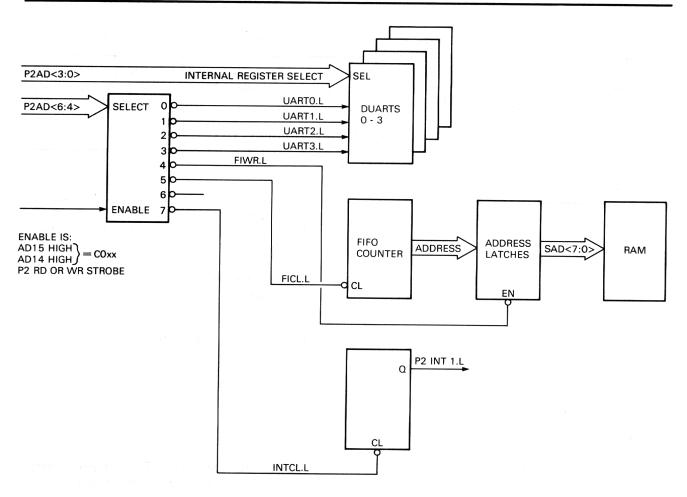

| 4.7.1     | DHV11 Internal I/O Control                      | 4-20 |

| 4.7.1.1   | PROC1 Memory-Mapped I/O                         | 4-20 |

| 4.7.1.2   | PROC1 Integral I/O Port Functions               | 4-22 |

| 4.7.1.3   | PROC2 Memory-Mapped I/O                         | 4-23 |

| 4.7.1.4   | PROC2 Integral I/O Port Functions               | 4-25 |

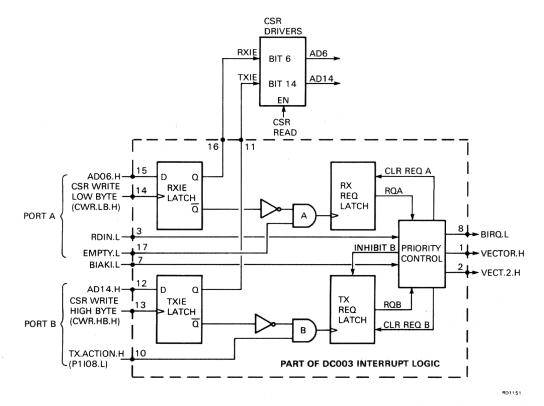

| 4.7.2     | O-Bus Interrupts                                | 4-25 |

| 4.7.3     | Common RAM Arbitration                          | 4-27 |

| 4.7.4     | FIFO Counter Control                            | 4-30 |

| 4.7.4.1   | Host Read from the FIFO                         | 4-31 |

| 4.7.4.2   | PROC2 Write to the FIFO                         | 4-31 |

| 4.7.5     | Control/Status Register (CSR)                   | 4-31 |

| 4.7.6     | Voltage Converter (SMPS)                        | 4-33 |

| 4.8       | ROM-BASED DIAGNOSTICS                           | 4-35 |

| 4.8.1     | Self-Test                                       | 4-35 |

| 4.8.1.1   | General                                         | 4-35 |

| 4.8.1.2   | Location and Interpretation of Diagnostic Codes | 4-35 |

| 4.8.2     | Background Monitor Program (BMP)                | 4-36 |

| CHAPTER 5 | MAINTENANCE                                     |      |

| E 1       | SCOPE                                           | 5-1  |

| 5.1       | MAINTENANCE STRATEGY                            | 5-1  |

| 5.2       | Preventive Maintenance                          | 5_1  |

| 5.2.1     | Corrective Maintenance                          | 5-1  |

| 5.2.2     | CONTECUTE INTAINTENANCE                         | -    |

| 5.3                                      | INTERNAL DIAGNOSTICS                              | 5.3        |

|------------------------------------------|---------------------------------------------------|------------|

| 5.3.1                                    | Self-Test                                         | 5-2        |

| 5.3.2                                    | Background Monitor Program (BMP)                  | 5-2        |

| 5.4                                      | XXDP+ DIAGNOSTICS                                 | 5-2        |

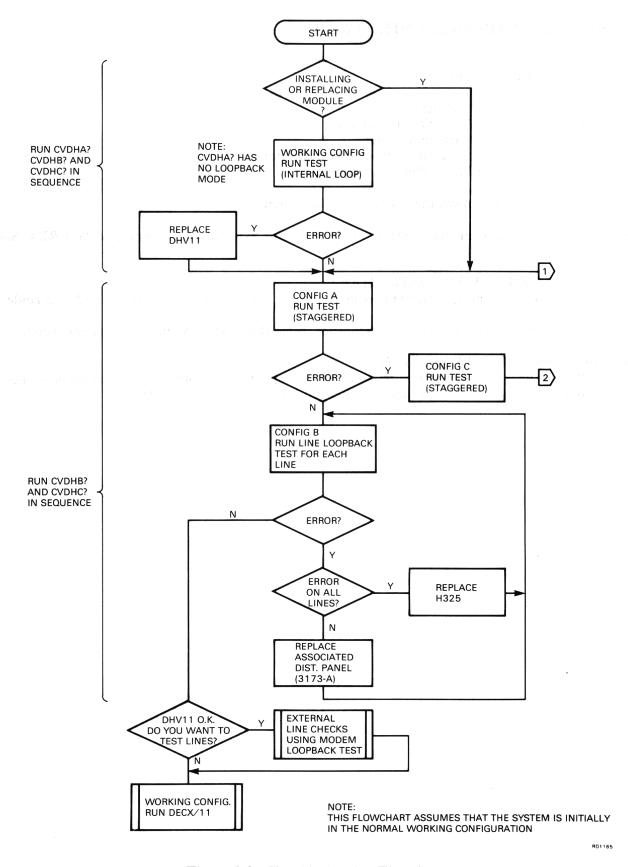

| 5.4.1                                    | CVDHA?, CVDHB?, and CVDHC?                        | 5-2        |

| 5.4.1.1                                  | Functions of CVDHA?                               | 5-2        |

| 5.4.1.2                                  | Functions of CVDHB?                               | 5-3        |

| 5.4.1.3                                  | Functions of CVDUC?                               | 5-3        |

| 5.4.2                                    | Functions of CVDHC?                               | 5-3        |

| 5.5                                      | DECX/11 Exerciser. DIAGNOSTIC SUPERVISOR SUMMARY. | 5-3        |

| 5.5.1                                    | Loading the Supervisor Diagnostic                 | 5-3        |

| 5.5.2                                    | Loading the Supervisor Diagnostic.                | 5-4        |

| 5.5.3                                    | Four Steps to Run a Supervisor Diagnostic         | 5-4        |

| 5.5.3.1                                  | Supervisor Commands                               | 5-5        |

| 5.5.4                                    | Command Switches                                  | 5-6        |

| 5.5.5                                    | Control/Escape Characters Supported               | 5-6        |

| 5.6                                      | Example Printouts                                 | 5-7        |

| 5.7                                      | FIELD REPLACEABLE UNITS (FRUs)                    | 5-9        |

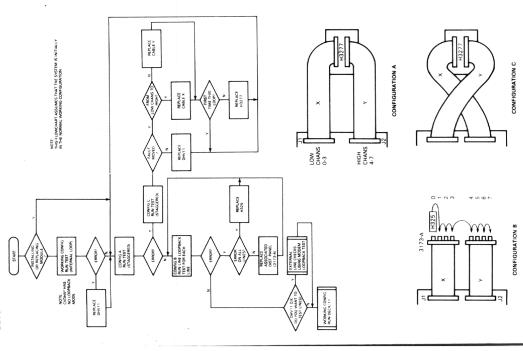

| 5.8                                      | TROUBLESHOOTING FLOWCHART                         | 5-9        |

| 3.8                                      | COMPONENT REPLACEMENT                             | 5-9        |

| ADDENIDIVA                               | IC DESCRIPTIONS                                   |            |

| APPENDIX A                               | IC DESCRIPTIONS                                   |            |

|                                          | CORR                                              |            |

| A.1                                      | SCOPE                                             | A-1        |

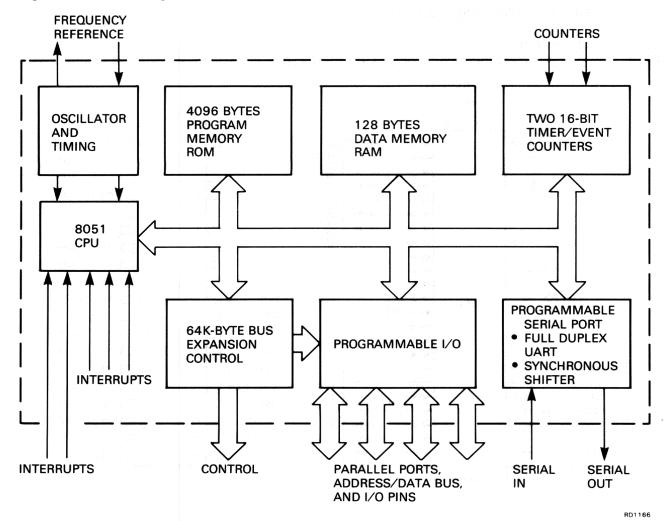

| A.2                                      | 8051 MICROPROCESSOR/MICROCOMPITER                 | A 1        |

| A.2.1                                    | 8051 Block Description                            | Δ_1        |

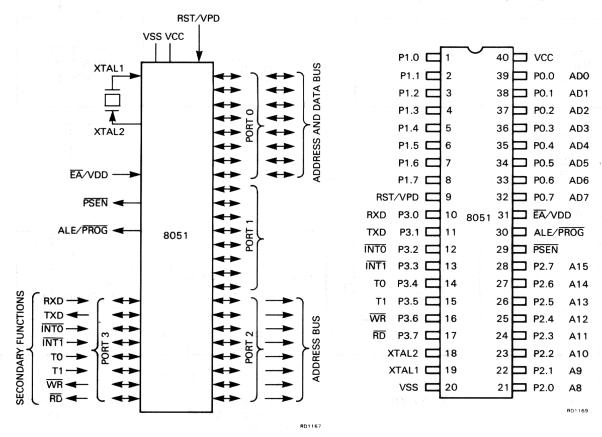

| A.2.2                                    | Configuration                                     | A-2        |

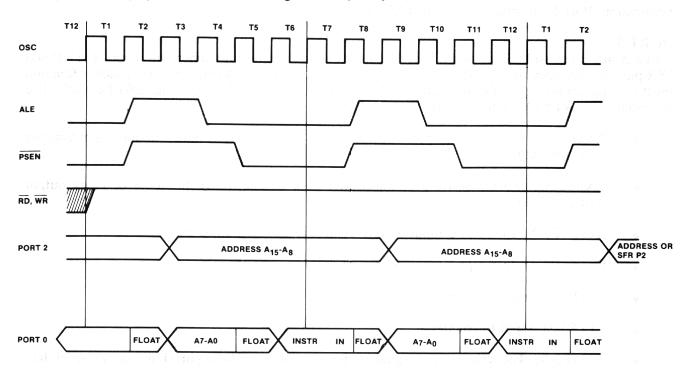

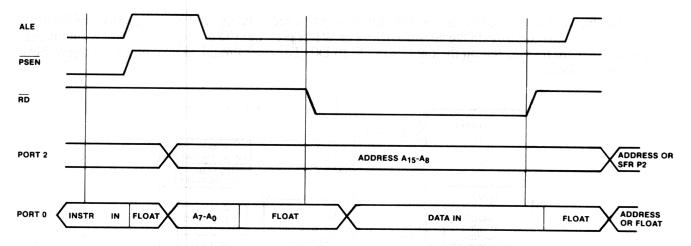

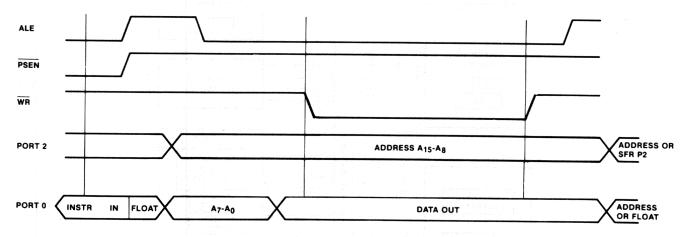

| A.2.3                                    | Read/ write Timing                                | A 1        |

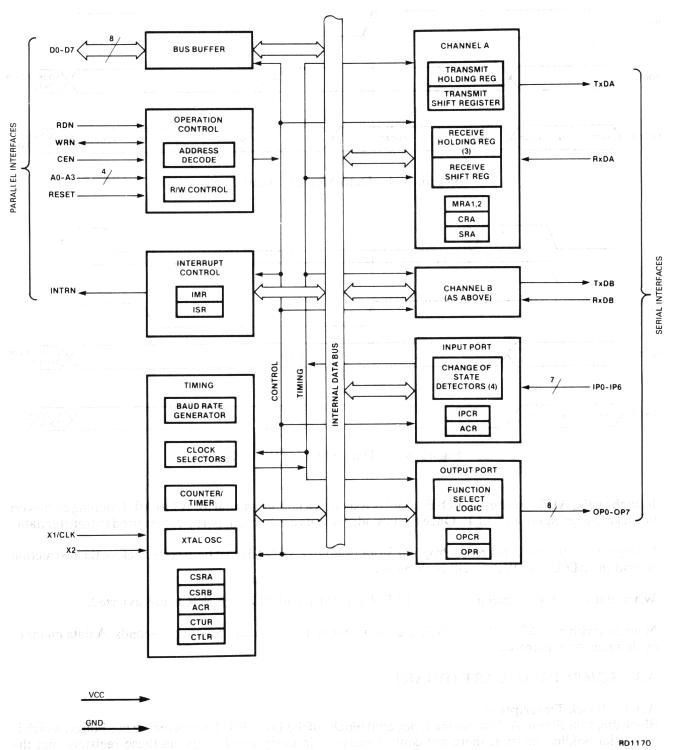

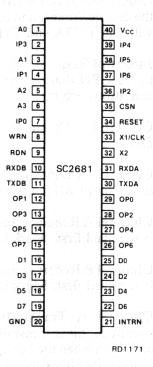

| A.3                                      | SC2081 DUAL UARI (DUARI)                          | Δ_5        |

| A.3.1                                    | block Description                                 | A_5        |

| A.3.2                                    | Pin-Out Information                               | A 7        |

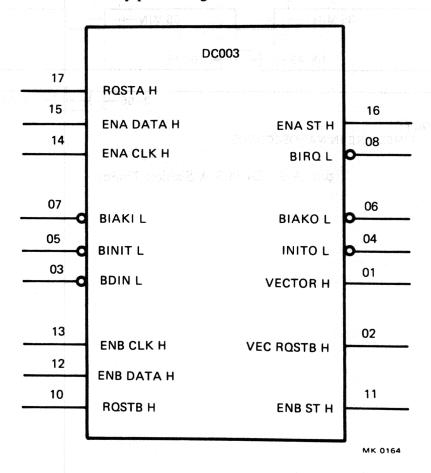

| A.4                                      | DC003 INTERRUPT IC                                | A 0        |

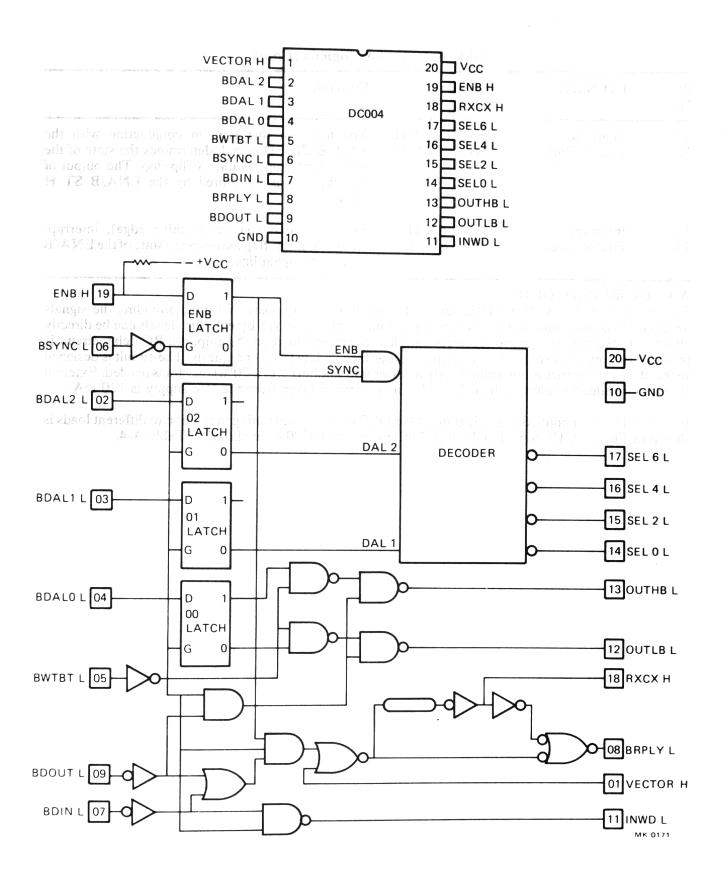

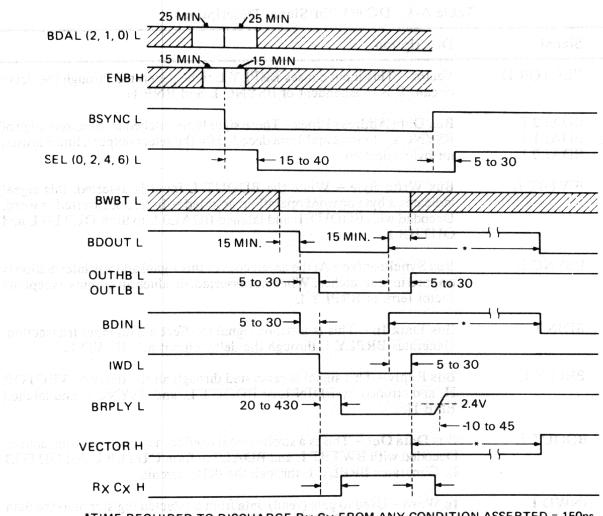

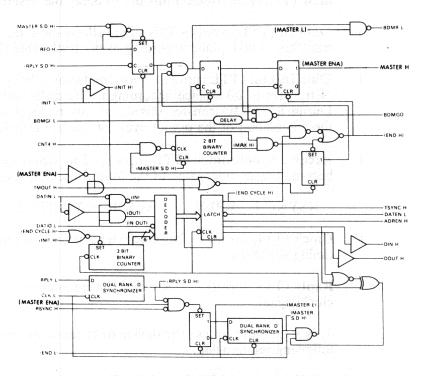

| A.5                                      | DC004 PROTOCOLIC                                  | A 12       |

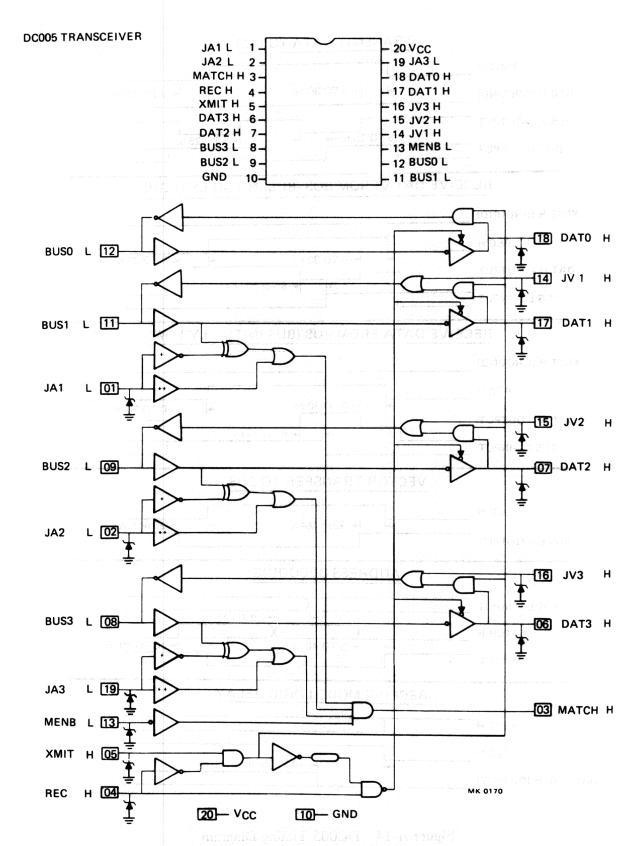

| <b>A.</b> 6                              | DC003 BUS TRAINSCEIVER IC                         | A 17       |

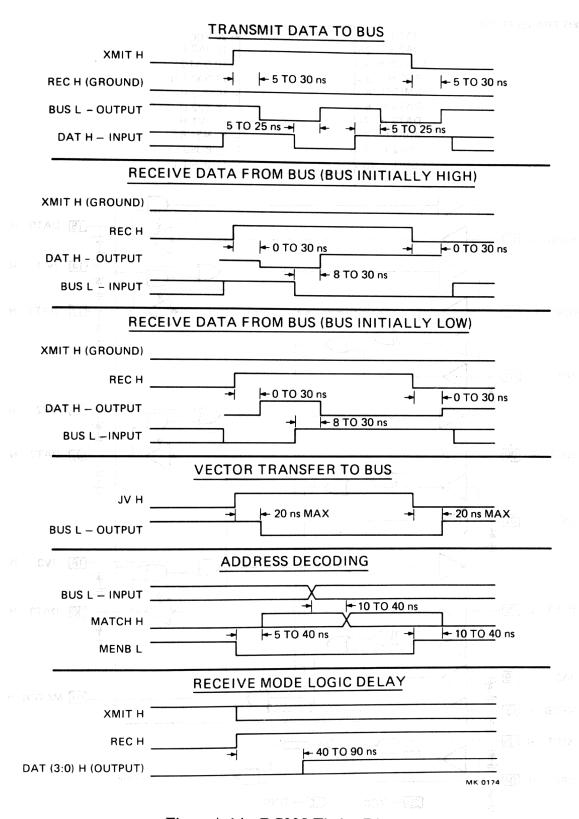

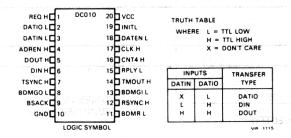

| A.7                                      | DC010 DIRECT MEMORY ACCESS LOGIC                  | A-21       |

| <u> 1814 - Janes II.</u>                 |                                                   |            |

| APPENDIX B                               | MODEM CONTROL                                     |            |

|                                          |                                                   |            |

| B.1                                      | SCOPE                                             | R-1        |

| B.2                                      | MODEM CONTROL                                     | R-1        |

| B.2.1                                    | Example of Auto-Answer Modem Control for the PSTN | B-2        |

|                                          |                                                   |            |

| ADDENITIVA                               |                                                   |            |

| AFFENDIA C                               | GLOSSARY OF TERMS                                 |            |

|                                          | GLOSSARY OF TERMS                                 |            |

| - (1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 | GLOSSARY OF TERMS SCOPE                           | C-1        |

| C.1 C.2                                  |                                                   | C-1<br>C-2 |

### FIGURES

| Figure No. | Title                                                           | Page        |

|------------|-----------------------------------------------------------------|-------------|

| 1-1        | M3104 Module                                                    | 1-3         |

| 1-2        | Example of DHV11 Configuration                                  | 1-5         |

| 1-3        | DHV11 Connections                                               | 1-6         |

| 1-4        | Serial Character Format                                         | 1-10        |

| 1-5        | DHV11 Functional Block                                          | 1-11        |

| 2-1        | Switch and Jumper Locations                                     | 2-3         |

| 2-2        | Bus Grant Continuity                                            | 2-6         |

| 2-3        | DHV11 Installation                                              | 2-8         |

| 2-4        | H3173-A Layout                                                  | 2-9         |

| 2-5        | H3173-A Circuit Diagram                                         | 2-10        |

| 2-6        | Staggered Loopback Test Connector                               | 2-12        |

| 2-7        | Line Loopback Test Connector                                    | 2-13        |

| 2-8        | Null Modem Cable Connections                                    | 2-15        |

| 3-1        | Register Coding                                                 | 3-3         |

| 3-2        | Diagnostic/Status Byte                                          |             |

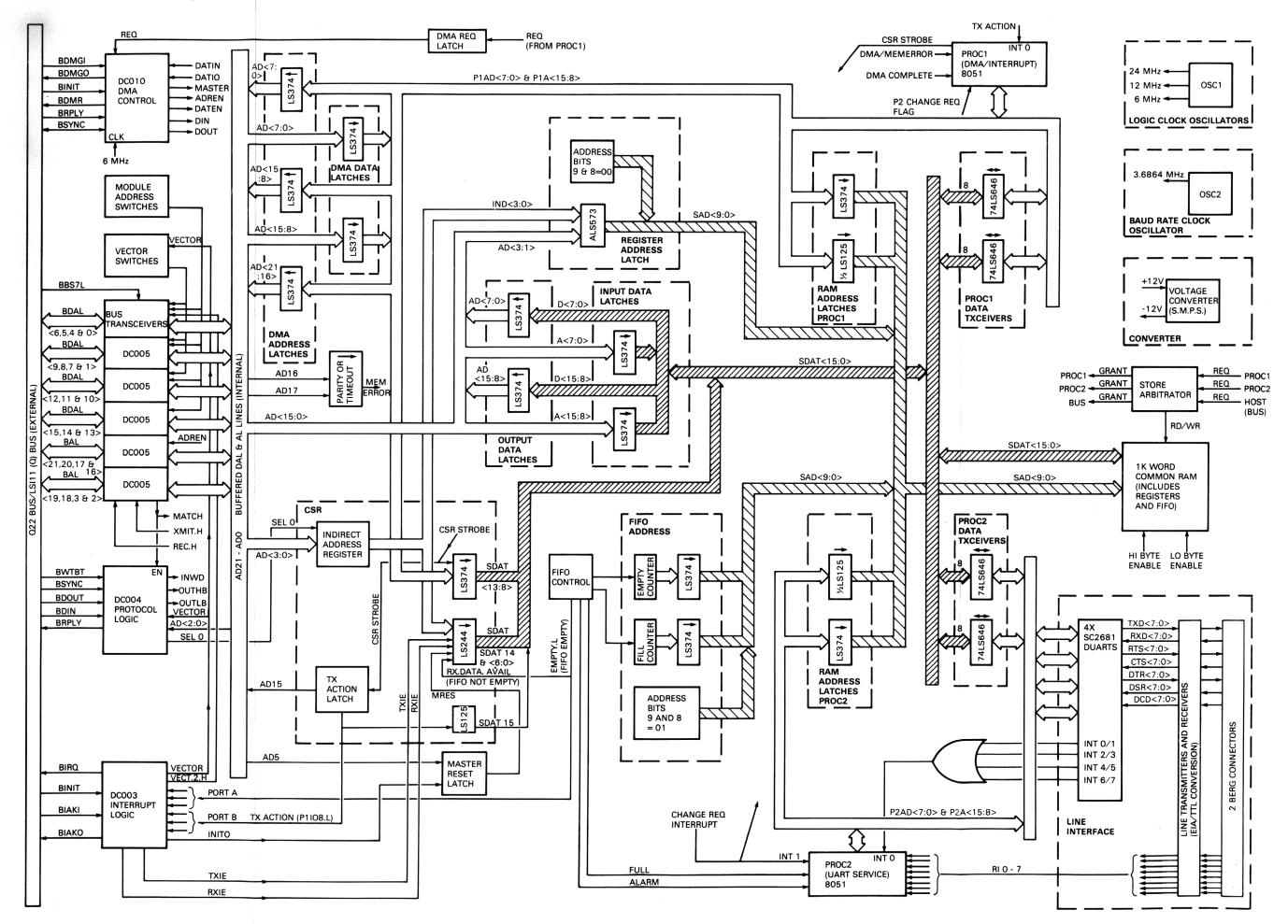

| 4-1        | DHV11 Block Diagram                                             |             |

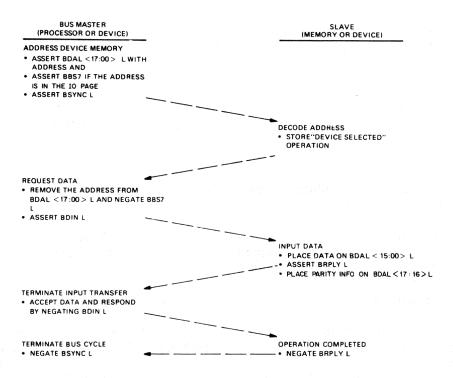

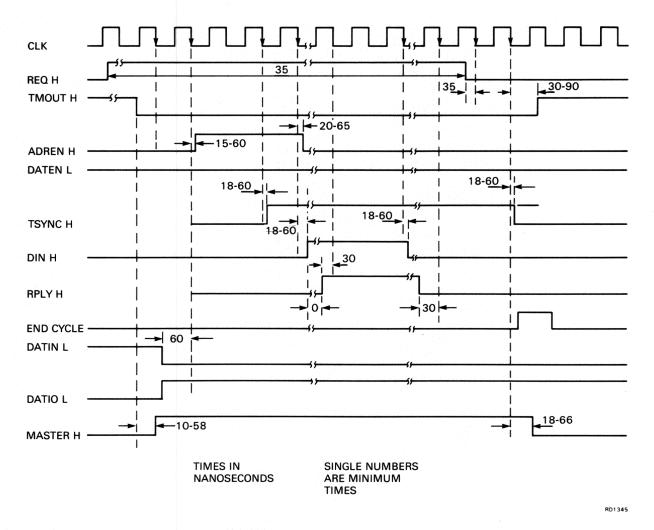

| 4-2        | DATI Bus Cycle                                                  | 4-4         |

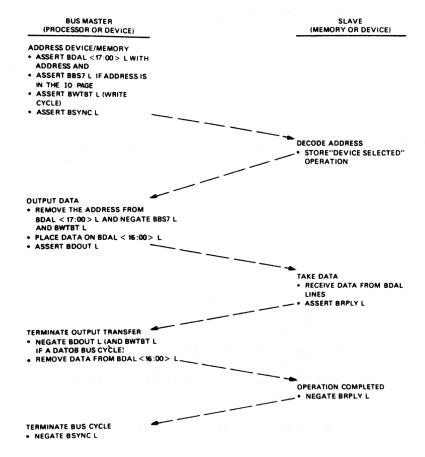

| 4-3        | DATO or DATOB Bus Cycle                                         |             |

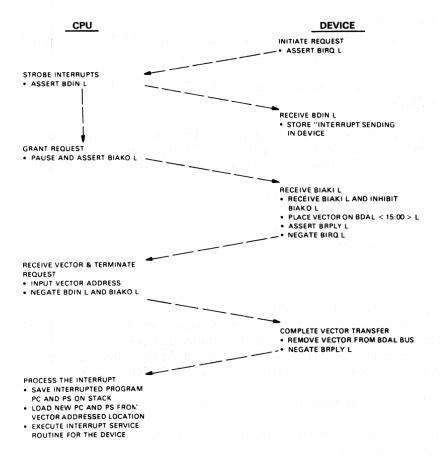

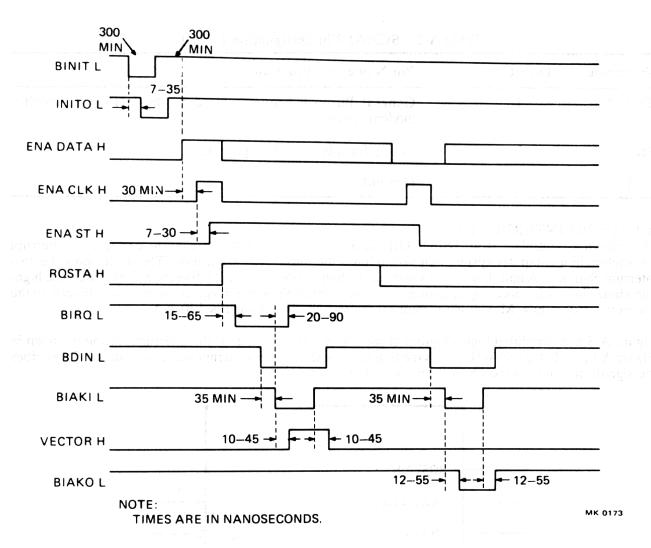

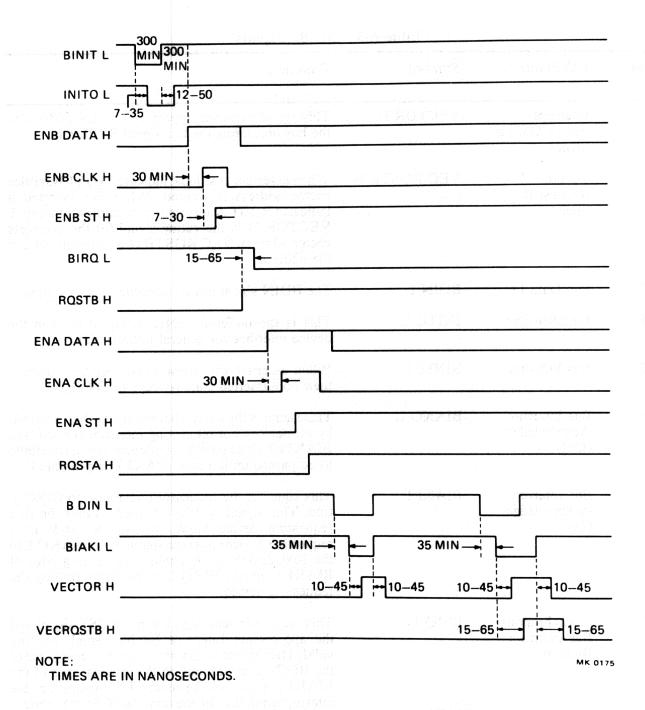

| 4-4        | Interrupt Request/Acknowledge Sequence                          | 4-5         |

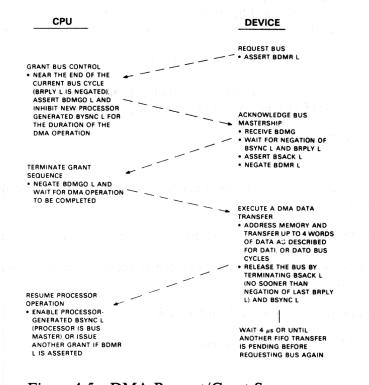

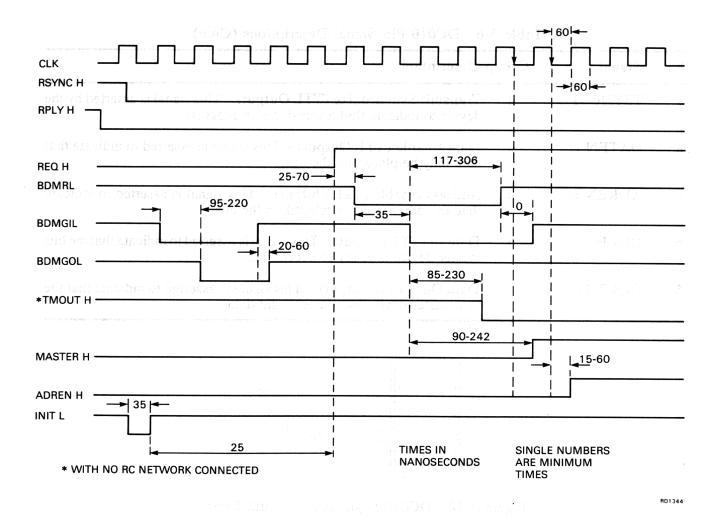

| 4-5        | DMA Request/Grant Sequence                                      |             |

| 4-6        | Common RAM – Memory Map                                         |             |

| 4-7        | Common RAM Access                                               |             |

| 4-8        | Reading from a Register                                         | 4-13        |

| 4-9        | Writing to a Register                                           |             |

| 4-10       | Single-Character Transmit                                       | 4-15        |

| 4-11       | DMA Data Transfer                                               | 4-16        |

| 4-12       | DMA Character Handling                                          |             |

| 4-13       | DMA/Memory Error Generation                                     |             |

| 4-14       | Receiving a Character                                           |             |

| 4-15       | PROC1 I/O Decoding                                              |             |

| 4-16       | PROC2 I/O Decoding                                              |             |

| 4-17       | Interrupt Logic                                                 |             |

| 4-18       | RAM Arbitration and Timing                                      |             |

| 4-19       | Store Access Timing Cycle                                       | 4-29        |

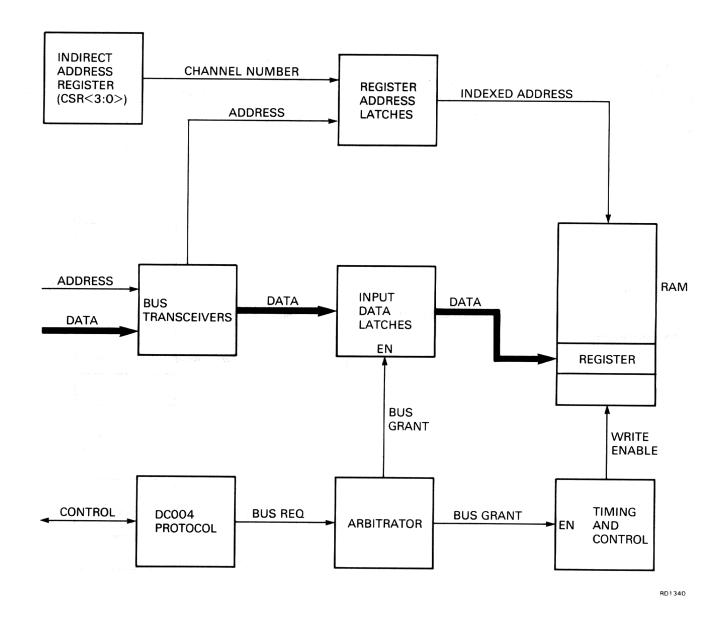

| 4-20       | CSR and Register Address Circuits                               | 4-32        |

| 4-21       | DHV11 Voltage Converter                                         | 4-34        |

| 4-22       | Register Contents After Self-Test                               | 4-35        |

| 5-1        | Troubleshooting Connection Diagram                              | 5-1         |

| 5-2        | Troubleshooting Flowchart                                       | 5-10        |

| A-1        | 8051 Block Diagram                                              | <b>A</b> -1 |

| A-2        | 8051 Symbol and Pin-Out Diagrams                                |             |

| A-3        | Program Memory Read Cycle                                       |             |

| A-4        | Data Memory Read Cycle                                          |             |

| A-5        | Data Memory Write Cycle                                         | A-5         |

| A-6        | SC2681 Dual Universal Asynchronous Receiver Transmitter (DUART) | <b>A-6</b>  |

| A-7        | SC2681 Pin-Out Diagram                                          |             |

| A-8        | DC003 Logic Symbol                                              |             |

| A-9        | DC003 A Section Timing                                          | A-10        |

| A-10       | DC003 A and B Section Timing                                    | A-11        |

| A-11<br>A-12<br>A-13<br>A-14<br>A-15<br>A-16<br>A-17<br>A-18<br>A-19                                                                                   | DC004 Simplified Logic Diagram DC004 Timing Diagram DC005 Simplified Logic Diagram DC005 Timing Diagram DC010 Simplified Logic Diagram DC010 Logic Symbol/Truth Table DC010 Voltage Waveforms DC010 Timing Diagram, DMA Request/Grant DC010 Timing Diagram                                                                                                                                                                                                                                                                                                                                              | A-15<br>A-19<br>A-20<br>A-21<br>A-23<br>A-23<br>A-24                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                        | TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                       |

|                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                       |

| Table No.                                                                                                                                              | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Page                                                                                                                                                  |

| 1-1<br>1-2<br>2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>3-1<br>3-2<br>3-3<br>4-1<br>4-2<br>4-3<br>4-4<br>A-1<br>A-2<br>A-3<br>A-4<br>A-5<br>A-6 | DHV11 Data Rates EIA/CCITT Signal Relationships Device Address Selection Guide Vector Address Selection Guide DHV11 Bus Connections H3173-A Connections Data-Rate/Cable-Length Relationships. Floating Device Address Assignments Floating Vector Address Assignments DHV11 Registers Data Rates DHV11 Self-Test Error Codes. PROC1 Memory-Mapped I/O PROC1 Integral I/O Port Functions. PROC2 Memory-Mapped I/O PROC2 Integral I/O Port Functions. 8051 Pin Description SC2681 Pin Designation DC003 Signals DC004 Pin/Signal Descriptions DC005 Pin/Signal Descriptions DC010 Pin/Signal Descriptions | 1-9<br>2-2<br>2-4<br>2-5<br>2-11<br>2-16<br>2-17<br>2-20<br>3-2<br>3-10<br>3-23<br>4-20<br>4-22<br>4-23<br>4-25<br>A-3<br>A-8<br>A-12<br>A-16<br>A-17 |

#### **PREFACE**

This document describes the installation requirements and servicing procedures for the DHV11 asynchronous multiplexer. It contains information for first-line service, field service support, and for customer engineers. A substantial programming chapter is included. Appendix C contains a glossary of terms used in this manual.

The manual is organized into five chapters plus appendices.

| Chapter 1  |                | Introduction                    |

|------------|----------------|---------------------------------|

| Chapter 2  |                | Installation                    |

| Chapter 3  | _              | Programming                     |

| Chapter 4  | , <u></u> 1, 7 | Technical Description           |

| Chapter 5  | -              | Maintenance                     |

| Appendix A | 4-5            | Integrated Circuit Descriptions |

| Appendix B | _              | Modem Control                   |

| Appendix C | _              | Glossary of Terms               |

The following is a list of related titles and document numbers.

| Document                                 | Number             |

|------------------------------------------|--------------------|

| LSI-11 Microcomputer Interfaces Handbook | EB-20175-20        |

| LSI-11 Systems Service Manual            | <b>EK-LSIFS-SV</b> |

| Communications Mini-Reference Guide      | <b>EK-CMINI-RM</b> |

| Terminals and Communications Handbook    | EB-20752-20        |

| Microcomputers and Memories              | EB-20912-20        |

| DHV11 Print Set                          | MP01793            |

| DHV11 Maintenance Card                   | EK-DHV11-MC        |

#### ORDERING THIS MANUAL

#### **DIGITAL Personnel Ordering**

Additional copies of this document and printed copies of the documents listed may be obtained from:

Digital Equipment Corporation 444 Whitney Street

Northboro, Massachusetts 01532

ATTN: Printing and Circulation Services (NR2/M15) Customer Services Section

rdering Information

#### **Customer Ordering Information**

Purchase orders for supplies and accessories should be sent to:

Digital Equipment Corporation Accessories and Supplies Group Cotton Road Nashua, New Hampshire 03060

Contact your local sales office or call DIGITAL Direct Catalog Sales toll-free 800-258-1710 from 8.30 a.m. to 5.00 p.m. eastern standard time (US customers only). New Hampshire, Alaska, and Hawaii customers should dial (603)-884-6660. Terms and conditions include net 30 days and F.O.B. DIGITAL factory. Freight charges will be prepaid by DIGITAL and added to the invoice. Minimum order is \$35,00. Minimum does not apply when full payment is sent in with an order. Checks and money orders should be made out to Digital Equipment Corporation.

#### **European Customers**

European customers should order the manual from their local Accessories and Supplies Group (A and SG).

# CHAPTER 1 INTRODUCTION

#### 1.1 SCOPE

Chapter 1 provides general information and specifications. It describes how the module can be configured, and how it interfaces with the system bus and the serial data lines. Physical and functional descriptions are also included.

#### 1.2 OVERVIEW

The DHV11 is an LSI-11/Q-bus option. All future references to the bus will be by the global term Q-bus. The specific terms Q16, Q18, or Q22 will be used where needed to identify versions with 16-, 18-, or 22-bit addresses.

1.2.1 General Description

The DHV11 option is an asynchronous multiplexer which provides eight full-duplex asynchronous serial data channels on Q-bus systems. The option can be used in many applications. These include data concentration, terminal interfacing, and cluster controlling.

The main features of the DHV11 are as follows:

- Eight full-duplex asynchronous data channels

- Direct Memory Access (DMA) or single-character programmed transfers on transmit

- Large 256-entry First-In-First-Out (FIFO) buffer for received characters, dataset status changes, and diagnostic information

- RS-423-A/V.10/X.26 and RS-232-C/V.28 compatible

- Full-duplex point-to-point or auto-answer dial-up operation

- Programmable split speed per line

- Total module throughput of 15000 characters per second

- Q16, Q18, and Q22 bus compatible

- Automatic flow control of transmitted and received data

- Self-test and background monitor diagnostics

- Programmable test facilities

- Single quad-height module (M3104)

- All functions are programmable, except for device address and vector selection which are done by hardware switches on the module.

Enough modem control is provided on all eight channels to allow auto-answer dial-up operation over the Public Switched Telephone Network (PSTN). Suitable modems to use this facility are the Bell models 103, 113, 212, or equivalent. The DHV11 can also be used for point-to-point operation over private lines. Modem control is implemented by software in the host.

The module provides DMA or single-character transfers from the host system to the serial lines. A 256-character FIFO buffer is provided for data received from the serial lines.

By using microcomputers (referred to as PROC 1 and PROC 2 in this manual), the DHV11 releases the host system from many of the data handling tasks.

One 8051 microcomputer controls DMA and single-character transmissions from the host system to the DHV11. A second 8051 controls four SC2681 Dual Universal Asynchronous Receiver Transmitters (DUARTs) which carry out the serial/parallel and parallel/serial conversion of data.

The DHV11 carries ROM-based diagnostics which are executed independently of the host. A full range of diagnostic programs is also available. These run under the PDP-11 Diagnostic Run-time Services (DRS).

A green LED gives the GO/NO-GO status of the module. More detailed diagnostic information is also made available to the host system via the FIFO buffer. Loopback test connectors are available for use with the system-based diagnostics.

I/O addresses and interrupt vectors for the module are selected on two Dual-In-Line (DIL) switchpacks. All other DHV11 functions and configurations are programmable.

To prevent data loss at high throughput levels, the DHV11 can be programmed for automatic X-ON and X-OFF operation.

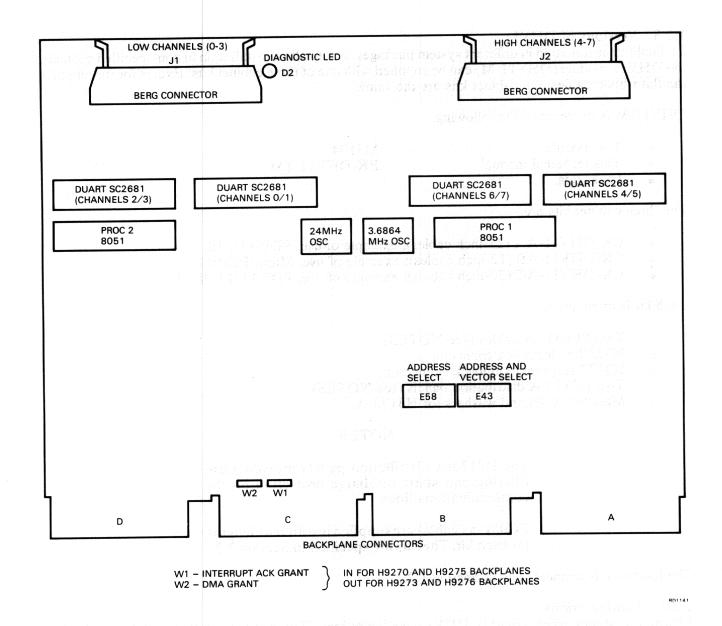

#### 1.2.2 Physical Description

The option is based on a standard quad-height module (M3104). The layout of this module is shown in Figure 1-1. The dimensions are 21.6 cm x 26.5 cm (8.51 inches x 10.44 inches).

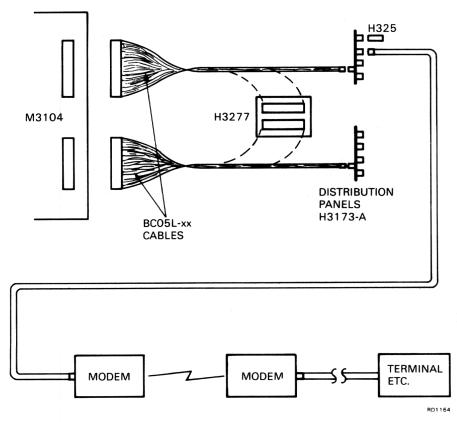

The module is connected to the Q-bus via connectors A and B. J1 and J2 are connected to the communications lines via BC05L-xx cables and H3173-A distribution panels.

On some backplanes, jumpers W1 (BIAK) and W2 (BDMG) extend the bus grant signals to the next module slot via connectors C and D.

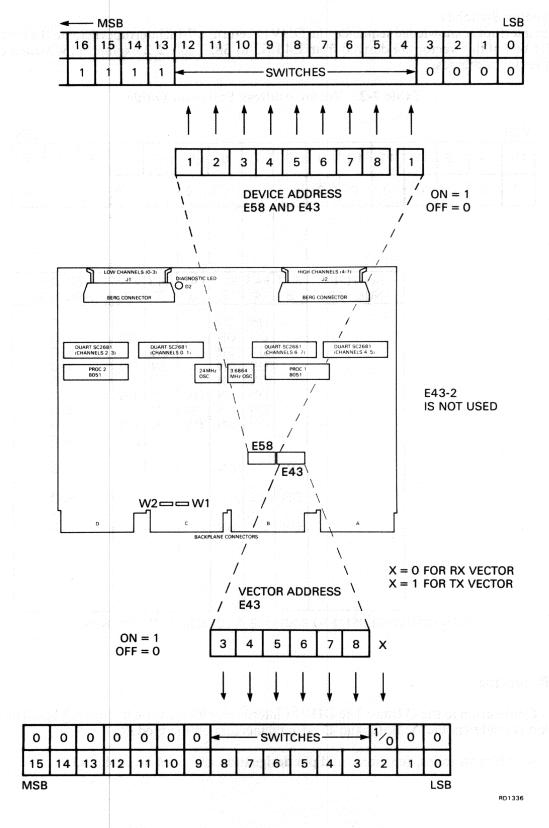

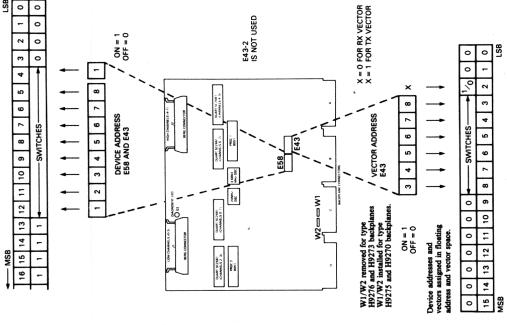

DIL switchpacks E58 and E43 select the device address and vector address of the module.

Figure 1-1 M3104 Module

#### 1.2.3 Versions of DHV11

To facilitate installation in different system packages, and to allow installation in non-specified cabinets, the DHV11 module (DHV11-M) can be supplied with one of three cabinet kits. Except for the length of the flat ribbon cables, the cabinet kits are the same.

#### DHV11-M is made up of the following:

• The module

M3104

This technical manual

EK-DHV11-TM

Packaging.

#### The three cabinet kits are:

• CK-DHV11-AA (21-inch cables); example of use, PDP-11/23S

• CK-DHV11-AB (12-inch cables); example of use, Micro/PDP-11

• CK-DHV11-AC (30-inch cables); example of use, PDP-11/23 PLUS

#### Each kit is made up of:

Two BC05L-xx cables (see NOTES)

• H325 line loopback connector

H3277 staggered loopback connector

Two H3173-A distribution panels (see NOTES)

Mounting bolts and washers for H3173-A.

#### **NOTES**

The H3173-A distribution panels provide noise filtering and static discharge protection on the communications lines.

BC05L-xx cables are supplied in different lengths for each kit. The kits are specified in Section 2.2.

The hardware is connected as in Section 1.2.5.

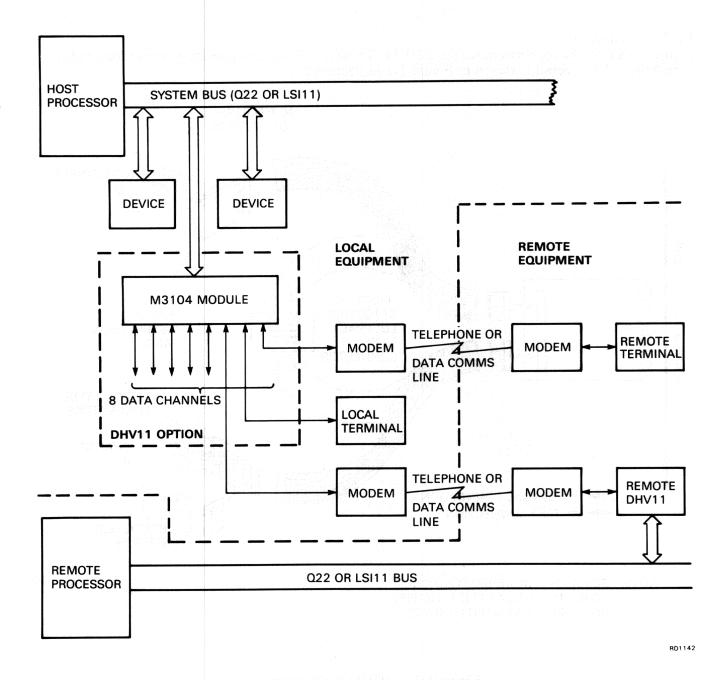

#### 1.2.4 Configurations

Figure 1-2 shows some possible DHV11 configurations. The position of the module on the bus (backplane) determines its DMA and interrupt priorities. A guide to positioning is given in Section 2.4. Any or all of the data channels can be connected to a terminal or to a data communications line.

Figure 1-2 Example of DHV11 Configuration

#### 1.2.5 Connections

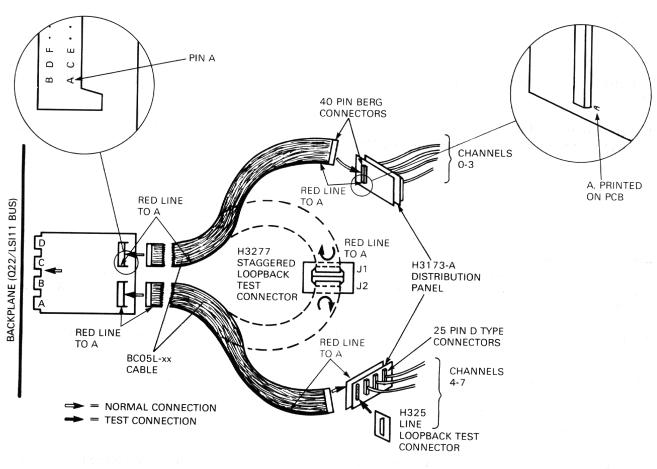

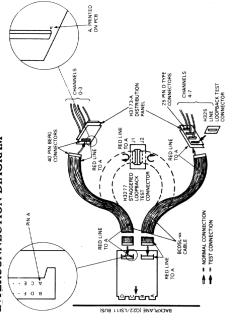

Figure 1-3 shows the connections for the DHV11. These include normal operating connections and test connections. More detail is shown in Figure 2-3 in Section 2.

Figure 1-3 DHV11 Connections

#### 1.3 SPECIFICATION

#### 1.3.1 Environment Conditions

- Storage temperature: 0°C to 66°C (32°F to 151°F)

- Operating temperature: 5°C to 60°C (41°F to 140°F)

- Relative humidity: 10% to 95% non-condensing (complies with DEC STD 102 class C)

#### 1.3.2 Electrical Requirements

```

+5 V dc + or - 5% at 4.3 A (typical), 6.6 A (maximum)

+12 V dc + or - 3% at 475 mA (typical), 980 mA (maximum)

```

Negative 12 V dc is generated by a Switch Mode Power Supply (SMPS) circuit on the DHV11. It has the following specification:

-11.85 V dc + or - 7.25% at 400 mA (maximum) Output ripple is 200 mV peak to peak at 33.3 kHz

Loads applied to the Q-bus are as follows:

Q-bus ac loads - 2.9 ac loads Q-bus dc loads - 1.0 dc loads

#### 1.3.3 Performance

1.3.3.1 Data Rates – Each channel can be programmed to operate at one of a number of speeds. If needed, the transmission and reception rates can be different (split speed). Table 1-1 shows the data rates which are possible. The maximum rate per channel is 38400 bits per second (bits/s).

The eight serial channels are implemented with four DUART ICs (Integrated Circuits). Channels are paired as follows: 0/1, 2/3, 4/5, 6/7. Because of the method of data rate generation, all transmit and receive rates for a DUART channel-pair must be in the same group (A or B).

Table 1-1 DHV11 Data Rates

| Speed (Bits/s) | Groups  |  |

|----------------|---------|--|

| 50             | Α       |  |

| 75             | В       |  |

| 110            | A and B |  |

| 134.5          | A and B |  |

| 150            | В       |  |

| 300            | A and B |  |

| 600            | A and B |  |

| 1200           | A and B |  |

| 1800           | В       |  |

| 2000           | В       |  |

| 2400           | A and B |  |

| 4800           | A and B |  |

| 7200           | Α       |  |

| 9600           | A and B |  |

| 19200          | В       |  |

| 38400          | Α       |  |

Data rate selection is covered in Chapter 3 (Programming).

1.3.3.2 Throughput – Each channel is capable of full-duplex operation at data rates of up to 38400 bits/s. The DHV11, however, cannot handle eight channels operating at this rate at the same time. Total maximum throughput is also dependent on the application and configuration.

#### Maximum throughput:

Per channel (send) - 1000 characters per second in single-character transfer mode

2000 characters per second in DMA mode

(receive) - 4000 characters per second.

On any channel, the DHV11 can send at one of the above transmit rates and receive at 4000 characters per second at the same time.

Total (8 channels) - 15000 characters per second

#### NOTES

The DMA firmware cannot handle transmit data faster than 2000 characters per second (19200 bits/s). If the transmit data rate is increased to 38400 bits/s, the duration of each character will be halved but there will be gaps in transmission.

15000 characters per second is the sum of both transmitted and received characters on all channels. This throughput could support all channels transmitting or receiving at 19200 bits/s, or all channels transmitting and receiving at 9600 bits/s. The above figures are based on a 7-bit character with start bit, parity bit, and one stop bit.

#### 1.4 INTERFACES

#### 1.4.1 System Bus Interface

The M3104 module will connect directly to the Q-bus via connectors A and B. To make the module compatible with backplanes which have Q-bus on C and D also, two jumpers (W1 and W2) are provided. The use of these jumpers is described in Section 2.3. Backplane signals, together with pin details, are listed in Table 2-3.

#### 1.4.2 Serial Interfaces

1.4.2.1 Interface Standards – The DHV11 provides interface signals which conform to a subset of the EIA/CCITT standard RS-232-C/V.24. The electrical characteristics conform to EIA/CCITT standards RS-232-C/V.24 and RS-423-A/V.28 (unbalanced interface). The interface is compatible with X.26/V.10 standards but does not comply with the slew rate requirements.

Connections to the external equipment are via 25-pin male subminiature D-type connectors, as specified for RS-232-C.

By means of suitable cables and connectors (not supplied or supported by DIGITAL) the channels can be made compatible with the following:

- 1. Subset of EIA interchange standard RS-449

- 2. EIA electrical standard RS-422 (balanced).

#### NOTE

Even when RS-422 is implemented; RS-423-A cable length/data rate recommendations should be followed.

Table 1-2 shows RS-232-C/V.24/RS-449 signal relationships, and pin connections for the male subminiature D-type connectors.

Table 1-2 EIA/CCITT Signal Relationships

| Signal<br>Name      |           | D-Type<br>Pin | RS-232-C | Circuit<br>CCITT V.24 | Circuit<br>RS-449 |

|---------------------|-----------|---------------|----------|-----------------------|-------------------|

| Protective Ground   | (GND)     | lo lo         | AA       |                       |                   |

| Signal Ground       | (SIG GND) | 4.7           | AB       | 102                   | SG                |

| Transmitted Data    | (TXD)     | 2             | ВА       | 103                   | SD                |

| Received Data       | (RXD)     | 3             | BB y     | 104                   | RD AIR            |

| Request to Send     | (RTS)     | 4             | CA       | 105                   | RS                |

| Clear to Send       | (CTS)     | 5             | СВ       | 106                   | CS                |

| Data Set Ready      | (DSR)     | 6             | СС       | 107                   | DM                |

| Data Terminal Read  | y (DTR)   | 20            | CD       | 108/2                 | TR                |

| Ring Indicator      | (RI)      | 22            | CE       | 125                   | IC                |

| Data Carrier Detect | (DCD)     | 8             | CF       | 109                   | RR                |

#### NOTE

The backward channels listed below are not supported. However, by using another channel for this function, and by connecting a suitable cable (H1200 or H1201 for example), backward channel operation is possible.

| Circuit No.                     | <b>Function</b><br>Ar (IACLORG yellostin gage as berlags errors motormood                                                                                                    |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 118<br>120<br>119<br>121<br>122 | Transmitted backward channel data Transmit backward channel line signal Received backward channel data Backward channel ready Backward channel received line signal detector |

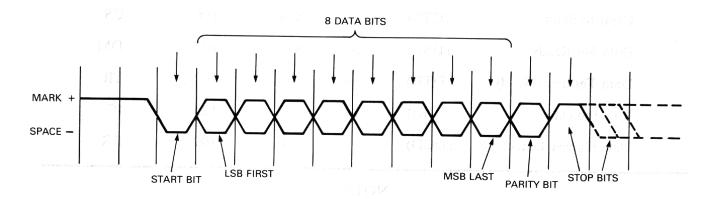

1.4.2.2 Serial Data Format – Serial characters are made up of a coded sequence of bits which are enclosed between a start and a stop signal. The start signal is always 1 bit long but the stop signal is programmable to 1, 1.5, or 2 bits. The duration of a bit is dependent on the selected data rate.

Character codes may be 5, 6, 7, or 8 bits long, optionally followed by a parity bit. Parity can be programmed as even, odd, or no parity.

On serial data channels controlled via the DHV11, the data line is held marking when inactive. Transfer of each character begins with a start bit (space) and ends with one or more stop bits (mark).

Figure 1-4 shows the reception of an 8-bit character with parity. The Least-Significant Bit (LSB) of the character code is transmitted first. If another character is not ready for transmission, the line will stay marking. The figure shows 1, 1.5, and 2 stop bits.

#### **NOTE**

This description applies to signals at the DUART pins. Signals measured on the interchange circuits will have the opposite polarity to those shown.

The data rate clock which times the serial data, is 16 times the programmed data rate. Arrows show when the bits are tested for polarity.

Figure 1-4 Serial Character Format

The DHV11 allows the following serial character formats:

- Characters of 5, 6, 7, or 8 bits with or without parity and with 1 stop bit

- Characters of 6, 7, or 8 bits with or without parity and with 2 stop bits

- Characters of 5 bits with or without parity and with 1.5 stop bits.

1.4.2.3 Line Receivers – The serial line receivers used in this module are 9637AC or equivalent. They convert the EIA input signals to TTL levels suitable for the DUARTs.

Signals are inverted by the receivers.

1.4.2.4 Line Transmitters – The serial line transmitters used in this module are 9636AC or equivalent. They convert TTL level signals from the DUARTs to EIA levels on the data lines.

Signals are inverted by the transmitters.

- 1.4.2.5 Speed/Distance Considerations The maximum data rate which can be used on a line depends upon a number of factors. These are:

- 1. The characteristics of the line transmitters and receivers

- 2. The characteristics of the serial cable (or link)

- 3. The length of the cable

- 4. Noise (interference) which affects the line.

A 'speed against distance' table for typical conditions is provided in Section 2.6.6.

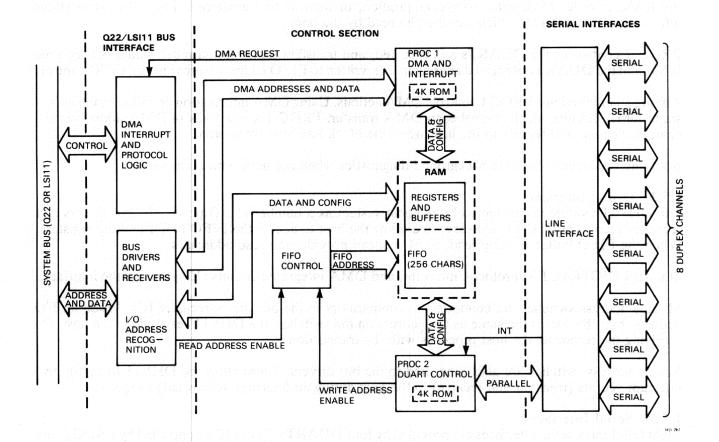

Figure 1-5 DHV11 Functional Block

#### 1.5 FUNCTIONAL DESCRIPTION

#### 1.5.1 Control Function

In the DHV11 module (Figure 1-5), data is transferred by three methods:

- 1. By DMA. Blocks of data are transferred from system memory to the serial interface. DMA data is routed via the bus receivers, PROC1, the RAM, and PROC2.

- 2. In the non-DMA mode, single characters can be transferred from the host system to the serial interface. The route for single characters is via the bus receivers, the RAM, PROC1, the RAM, and PROC2.

- 3. Single characters can be transferred from the serial interface to the host system. The route for received characters is via PROC2, the FIFO buffer, and the bus drivers.

At the center of the control section is a 1K-word RAM. By writing control words to registers in the RAM, the host can indirectly configure and command the module. The host can also write data bytes to registers in the RAM.

Two microcomputers (PROC 1 and PROC 2), which contain their own programs in internal ROM, scan the RAM in order to detect a new configuration, or data to be transferred. They also write status information to the RAM, which can then be read by the host.

PROC 2 configures the DUARTs as instructed, and transfers transmit and receive data between the RAM and the DUARTs. Received characters are written to FIFO addresses provided by FIFO control.

Among other functions, PROC 1 controls DMA actions. Using DMA information provided by the host, it starts DMA circuits which control each DMA transfer. PROC 1 keeps track of DMA addresses and character count, and reports to the host when the block has been transferred.

Both microcomputers execute background diagnostics when not busy with other tasks.

#### 1.5.2 Q-Bus Interface

The DHV11 module is considered by the host system as a number of I/O ports. The bus drivers and receivers recognize DHV11 addresses and allow the host to access the FIFO buffer and the registers. When the FIFO buffer is being read, FIFO control provides the read addresses.

Standard DIGITAL LSI protocol, interrupt, and DMA integrated circuits (ICs) control the interface.

Module address switches are connected to comparators in the bus driver/receiver ICs. When an I/O address from the host is the same as the address on the switches, the DHV11 responds to the host. On receiving the response, the host proceeds with the transaction.

Vector address switches are also connected to the bus drivers. These allow the DHV11 to supply two interrupt vectors (transmit and receive) to the host during an interrupt acknowledge sequence.

#### 1.5.3 Serial Interfaces

Eight full-duplex serial interfaces are provided by four DUARTs. These ICs, controlled by PROC 2, are configured as needed by the host system. They carry out the serial/parallel and parallel/serial conversion. When a received character is assembled PROC 2 is interrupted.

The status of modem control lines for each channel is polled by PROC 2. If programmed to do so, the DHV11 will report changes of modem status to the host. Such reports are made via the FIFO buffer and the device registers.

### CHAPTER 2 INSTALLATION

#### 2.1 SCOPE

This chapter contains information on how to prepare and install the DHV11 option. It contains sections on the following:

- Device and vector address selection

- Rules for backplane positioning

- Recommended cables

- Test connectors

- Floating address and vector assignment

- Testing after installation.

#### 2.2 UNPACKING AND INSPECTION

There are a number of versions of the DHV11, all of which are based on the module kit DHV11-M. This may be ordered with one of the three cabinet kits listed below. Examine all parts for physical damage. Report damaged or missing items to the shipper and the DIGITAL representative.

#### DHV11-M:

| Part Number          | Description Quantity              |

|----------------------|-----------------------------------|

| M3104<br>EK-DHV11-TM | DHV11 module 1 Technical manual 1 |

#### CK-DHV11-AA, 21-inch cab-kit:

| Part Number | Description                  | Quantity |  |

|-------------|------------------------------|----------|--|

| H3173-A     | Distribution panel           | 2        |  |

| BC05L-1K    | 40-conductor cable           | 2        |  |

| H325        | Line loopback connector      | 1        |  |

| H3277       | Staggered loopback connector | 1        |  |

| 90-06021-01 | Bolt                         | 8        |  |

| 90-06633-00 | Washer                       | 8        |  |

#### CK-DHV11-AB, 12-inch cab-kit:

As for 21-inch cab-kit but with BC05L-01 cables.

#### CK-DHV11-AC, 30-inch cab-kit:

As for 21-inch cab-kit but with BC05L-2F cables.

#### **NOTE**

BC05L-1K is 53.34 cm (21 inches) long BC05L-01 is 30.48 cm (12 inches) long BC05L-2F is 76.20 cm (30 inches) long

#### 2.3 INSTALLATION CHECKS

#### 2.3.1 Address Switches

The device address for the DHV11 is set on switchpacks E58 and E43 (Figure 2-1). Table 2-1 explains the relationship between device addresses and switch positions. The table gives the Q22 bus address for each entry. The equivalent Q16 and Q18 bus addresses will be 16xxxx and 76xxxx respectively.

**MSB** LSB 16 15 14 13 12 10 3 2 0 1 1 **SWITCHES** 0 0 0 0 **SWITCH** E58 E58 E58 E58 E58 E58 E58 E43 DEVICE NUMBER 1 3 4 5 6 **ADDRESS** ON 17760020 ON 17760040 ON ON 17760060 ON 17760100 ON 17760200 ON ON 17760300 ON 17760400 ON ON 17760500 ON ON 17760600 ON ON ON 17760700 ON 17761000 ON 17762000 ON ON 17763000 ON 17764000 ON 17770000

Table 2-1 Device Address Selection Guide

ON = SWITCH CLOSED TO RESPOND TO A LOGICAL 1 ON THE BUS

RD1337

Figure 2-1 Switch and Jumper Locations

#### 2.3.2 Vector Switches

During an interrupt acknowledge sequence, the DHV11 returns a 7-bit interrupt vector to the host. The six high-order bits of this vector are derived from E43-S3 to S8. Table 2-2 explains how switch positions relate to vector addresses.

**MSB** LSB 15 14 13 12 11 10 9 8 7 6 5 3 4 2 0 0 0 0 0 0 0 0 **SWITCHES** 1/0 0 **SWITCH** E43 | E43 | E43 | E43 E43 E43 **VECTOR NUMBER** 3 4 5 6 **ADDRESS** ON ON 300 ON ON ON 310 ON ON ON 320 ON ON ON ON 330 ON ON ON 340 ON ON ON ON 350 ON UΝ ON ON 360 ON ON ON ON ON 370 ON 400 ON ON 500 ON ON 600 ON ON ON 700

Table 2-2 Vector Address Selection Guide

ON = SWITCH CLOSED TO PRODUCE A LOGICAL 1 ON THE BUS

RD1338

#### 2.3.3 Backplane

2.3.3.1 Connection to the Q Bus – The DHV11 interfaces with the system via the Q-bus. The physical connection is made via the A, B, C, and D edge connectors on the module.

Bus signals, their categories, functions, and pin designation are listed in Table 2-3.

Table 2-3 DHV11 Bus Connections

| Category          | Signal          | Function              | Pin Number |

|-------------------|-----------------|-----------------------|------------|

| Data/Address      | BDAL0.L – 1.L   | Data/Address Lines    | AU2 – AV2  |

|                   | BDAL1.L - 15.L  |                       | BE2 - BV2  |

|                   | BDAL16.L - 17.L |                       | AC1 – AD1  |

|                   | BDAL18.L - 21.L |                       | BC1 – BF1  |

| Data Control      | BDOUT.L         | Data Output Strobe    | AE2        |

|                   | BRPLY.L         | Reply Handshake       | AF2        |

|                   | BDIN.L          | Data Input Strobe     | AH2        |

|                   | BSYNC.L         | Synchronize Strobe    | AJ2        |

|                   | BWTBT.L         | Write Byte Control    | AK2        |

|                   | BBS7.L          | I/O Page Select       | AP2        |

| Interrupt Control | BIRQ.L          | Int. Req. Level 4     | AL2        |

|                   | BIAŘI.L         | Int. Ack. Input       | AM2        |

|                   | BIAKO.L         | Int. Ack. Output      | AN2        |

| DMA Control       | BDMR.L          | DMA Request           | AN1        |

|                   | BDMGI.L         | DMA Grant Input       | AR2        |

|                   | BDMGO.L         | DMA Grant Output      | AS2        |

|                   | BSACK.L         | Bus Grant Acknowledge | BN1        |

| System Control    | BINIT.L         | Initialization Strobe | AT2        |

| Power Supplies    | +5 V            | DC Volts              | AA2 – DA2  |

|                   | +12 V           | DC Volts              | BD2        |

| Grounds           | GND             | Ground Connections    | AC2 – DC2  |

|                   | GND             | Ground Connections    | AT1 – DT1  |

|                   | GND             | Ground Connections    | AJ1 – BJ1  |

|                   | GND             | Ground Connections    | AM1 – BM1  |

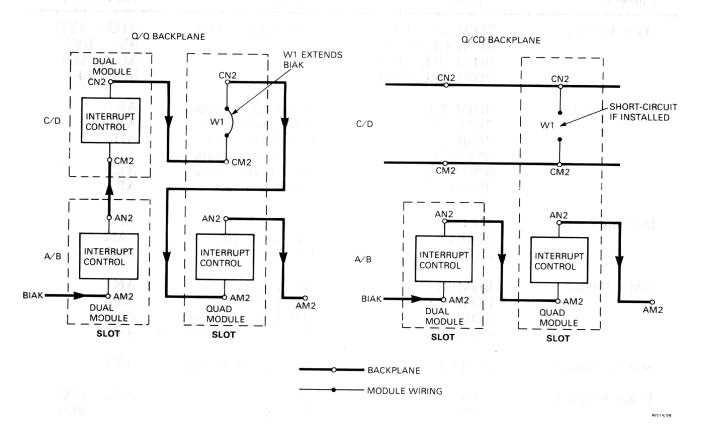

#### 2.3.3.2 Bus Grant Continuity Jumpers - Backplanes suitable for DHV11 fall into two groups:

Q/CD - Q-bus on A and B connectors, user-defined signals on C and D O/O - O-bus on A and B, and C and D connectors.

In Q/CD backplanes, bus grant signals pass through each installed module via the A and B connectors of each bus slot.

Q/Q backplanes are designed so that two dual-height options can be installed in a quad-height bus slot. The Q-bus lines are routed as follows:

AB, first slot

CD, first slot

CD, second slot

AB, second slot and so on.

Lines AM2, AN2, CM2, and CN2 (BIAK) and AR2, AS2, CR2, and CS2 (BDMG) carry the bus grant signals. Figure 2-2 uses BIAK as an example of bus grant routing. The same method is used for continuity of BDMG.

Figure 2-2 Bus Grant Continuity

Each dual-height module will extend the continuity of bus grant signals BIAK and BDMG to the next module.

If a quad-height option is installed, jumpers perform the grant continuity function of a dual option installed on C and D.

Therefore, with a Q/Q backplane, W1 and W2 should be installed. H9275 and H9270 are examples of this type of backplane.

In a Q/CD backplane, pins CM2, CN2, CR2, and CS2 are available for user-defined signals. Therefore W1 and W2 must be removed. H9276 and H9273 are examples of this type of backplane.

#### 2.4 PRIORITY SELECTION

The DHV11 uses the BIRQ4 line to request interrupt service. It does not monitor any of the higher-level interrupt request lines. Because of this, both the interrupt request and DMA (non-processor request) priorities of the DHV11, are selected by the position of the DHV11 on the bus.

The bus (backplane) position may be a compromise between DMA and interrupt priority requirements. As a general rule, DMA request priorities should be considered first, and then interrupt (bus) requests.

2.4.1 DMA Request

DMA request priority is usually selected on a basis of throughput. The faster devices (higher throughput) will usually have priority over slower DMA devices; for example, disk, tape, and then communications devices. This is because a fast device will usually reach an overrun/underrun condition sooner than a slower device.

The simple approach can be further complicated by hardware buffering in the device. For example, a disk controller may read a full sector of information into a hardware buffer. It may then raise a DMA request to move the data to system memory. If the request is not serviced immediately, there is no danger of data loss. However, a magnetic tape unit or a communications device without buffering may need to be serviced quickly. In this case the slower unit might be serviced first. This method of priority selection could, of course, reduce disk throughput.

The system designer should consider the following four factors in determining DMA priorities:

1. Device average service time

- 2. Maximum wait time to be allowed (before loss of data)

- 3. Average time between DMA requests

- 4. Slack time.

Using the above parameters, the system designer should assume that all DMA requests are made at the same time. He should then check that his selected priority sequence does not violate the parameters of any DMA device.

If there is only one DMA device in the system there is no DMA contention. The device's position on the bus will be determined by its interrupt (BIRQ) priority.

#### NOTE

If the system memory needs refresh cycles via the bus, these should be considered as DMA requests.

2.4.2 Interrupt Request

Interrupt requests have four levels of priority. The lowest is Level 4 and the highest is Level 7. Requests are made on bus interrupt request lines BIRQ4 to BIRQ7. To avoid contention, lower-priority devices usually monitor the higher request lines.

Within any priority group, priority is decided by backplane position. The most time-critical interrupts must be nearer the CPU.

There are two common types of configuration for devices which need interrupt service:

- 1. The position-independent configuration

- 2. The position-dependent configuration.

In the position-independent configuration, devices of different priority groups can be placed anywhere in the backplane.

In the position-dependent configuration, devices of different priority groups are positioned in descending order of priority from the CPU.

Because the DHV11 is a Level 4 device which does not monitor higher request lines, it must be positioned after all devices that do. Therefore DHV11 priority is position dependent in either configuration.

By assuming that all interrupts are raised at the same time, the system designer can check his priority sequence as for DMA requests.

The final configuration can be tested to some extent by the DECX/11 diagnostic. Some changes may be needed for optimum performance.

#### 2.5 MODULE INSTALLATION

Once the backplane position of the DHV11 has been defined, the module can be installed and the backplane checked with a testmeter.

#### **CAUTION**

Switch off power before inserting or removing modules. Be careful not to snag module components on the card guides or adjacent modules.

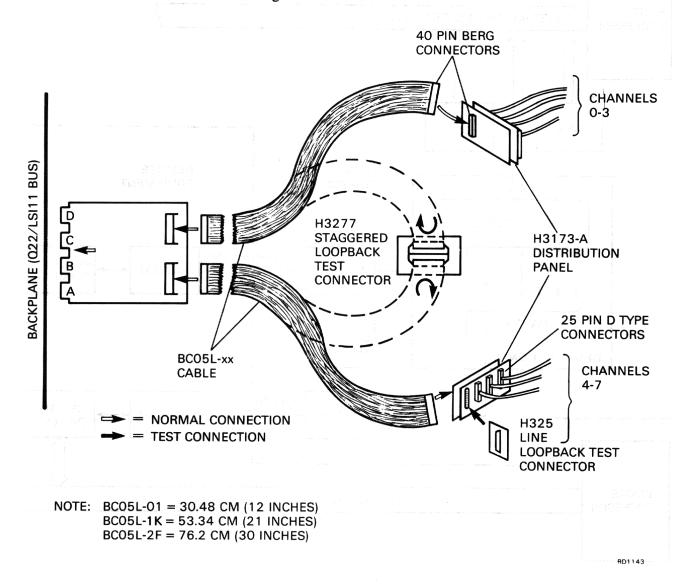

NOTE: BC05L-01 = 30.48 CM (12 INCHES) BC05L-1K = 53.34 CM (21 INCHES) BC05L-2F = 76.2 CM (30 INCHES)

Figure 2-3 DHV11 Installation

RD1540

- 1. Connect the BC05L cables to J1 and J2. Figure 2-3 shows how the parts of the option connect together.

- 2. Install the module in its correct backplane position as defined in Section 2.4.

- 3. Check that +5 V is present between AA2 and ground.

- 4. Check that +12 V is present between BD2 and ground.

#### 2.6 CABLES AND CONNECTORS

#### 2.6.1 Distribution Panel

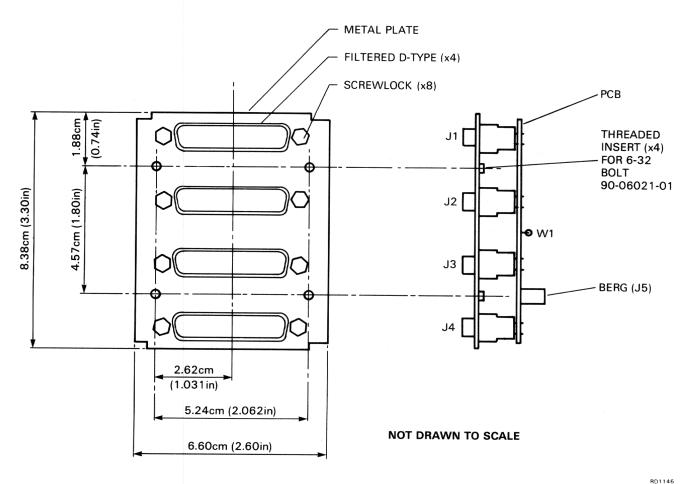

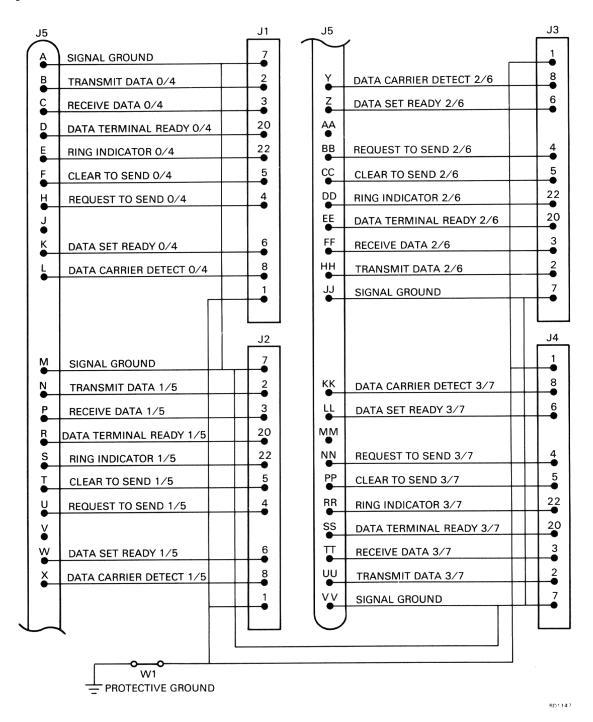

Each H3173-A distribution panel adapts one of the DHV11's berg connectors to four subminiature D-type RS-232-C connectors. Noise filtering is provided on each pin of the RS-232-C connectors. This reduces electromagnetic radiation from the cables. It also provides the logic with some protection against static discharge.

Figure 2-4 shows the layout and Figure 2-5 shows the circuit. There is no CCITT equivalent of EIA circuit AA (protective ground). The 0-ohm link W1 can be removed to disconnect this circuit as needed.

Table 2-4 is for two distribution panels. Information in parentheses applies to channels 4 to 7.

Figure 2-4 H3173-A Layout

...

The following is an example of the use of Table 2-4.

Signal TXD0 is the Transmitted Data line for channel 0. Its CCITT circuit number is 103. It is connected to J5 pin B on the H3173-A for channels 0 to 3.

Signal TXD4 is the Transmitted Data line for channel 4. Its CCITT circuit number is 103. It is connected to J5 pin B on the H3173-A for channels 4 to 7.

Figure 2-5 H3173-A Circuit Diagram

Table 2-4 H3173-A Connections

| Signal              | Name                  | Circuit No. | J5 Pin No.  |

|---------------------|-----------------------|-------------|-------------|

| SIG GND 0(4)        |                       | 102         | 1-A (2-A)   |

| TXD0(4)             | Transmitted Data      | 103         | 1-B (2-B)   |

| RXD0(4)             | Received Data         | 104         | 1-C (2-C)   |

| DTR0(4)             | Data Terminal Ready   | 108/2       | 1-D (2-D)   |

| RI0(4)              | Ringing Indicator     | 125         | 1-E (2-E)   |

| CTS0(4)             | Clear to Send         | 106         | 1-F (2-F)   |

| RTS0(4)             | Request to Send       | 105         | 1-H (2-H)   |

| DSR0(4)             | Data Set Ready        | 107         | 1-K (2-K)   |

| DCD0(4)             | Data Carrier Detected | 109         | 1-L (2-L)   |

| SIGGND 1(5)         |                       | 102         | 1-M (2-M)   |

| TXD1(5)             |                       | 103         | 1-N (2-N)   |

| RXD1(5)             |                       | 104         | 1-P (2-P)   |

| DTR1(5)             |                       | 108/2       | 1-R (2-R)   |

| RI1(5)              |                       | 125         | 1-S (2-S)   |

| CTS1(5)             |                       | 106         | 1-T (2-T)   |

| RTS1(5)             |                       | 105         | 1-U (2-U)   |

| DSR1(5)             |                       | 107         | 1-W (2-W)   |

| DCD1(5)             |                       | 109         | 1-X(2-X)    |

| DCD2(6)             |                       | 109         | 1-Y (2-Y)   |

| DSR2(6)             |                       | 107         | 1-Z(2-Z)    |

| RTS2(6)             |                       | 105         | 1-BB (2-BB) |

| CTS2(6)             |                       | 106         | 1-CC (2-CC) |

| RI2(6)              |                       | 125         | 1-DD (2-DD) |

| DTR2(6)             |                       | 108/2       | 1-EE (2-EE) |

| RXD2(6)             |                       | 104         | 1-FF (2-FF) |

| TXD2(6)             |                       | 103         | 1-HH (2-HH) |

| <b>SIG GND 2(6)</b> |                       | 102         | 1-JJ (2-JJ) |

| DCD3(7)             |                       | 109         | 1-KK (2-KK) |

| DSR3(7)             |                       | 107         | 1-LL (2-LL) |

| RTS3(7)             |                       | 105         | 1-NN (2-NN) |

| CTS3(7)             |                       | 106         | 1-PP (2-PP) |

| RI3(7)              |                       | 125         | 1-RR (2-RŔ) |

| DTR3(7)             |                       | 108/2       | 1-SS (2-SS) |

| RXD3(7)             |                       | 104         | 1-TT (2-TŤ) |

| TXD3(7)             |                       | 103         | 1-UU (2-UÚ) |

| SIG GND 3(7)        |                       | 102         | 1-VV (2-VV) |

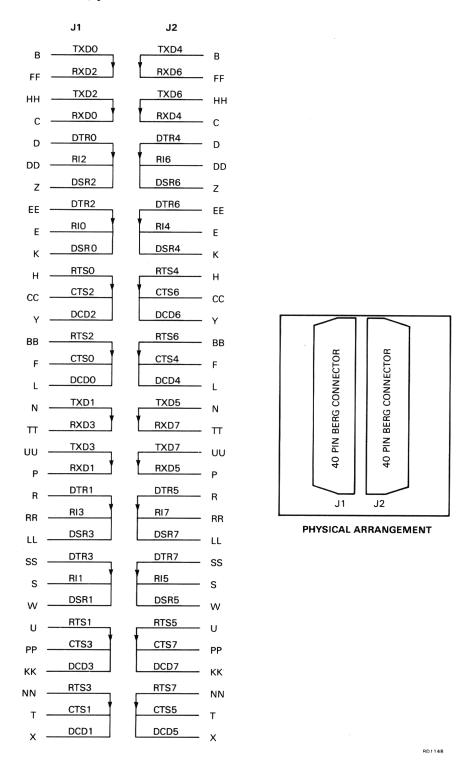

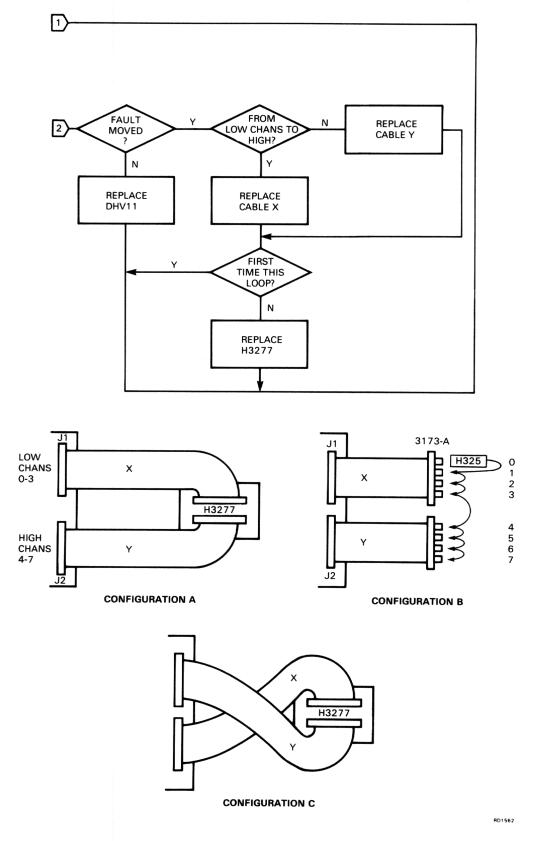

#### 2.6.2 Staggered Loopback Test Connector H3277

(See Figure 2-6.) The H3277 test connector is used during diagnostic tests. It allows all channels to be tested. Using this connector, you can trace a channel fault to one of two channels.

Figure 2-6 Staggered Loopback Test Connector

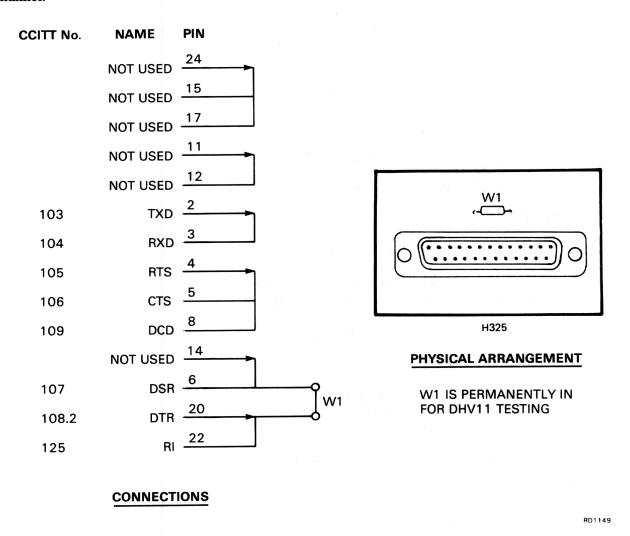

2.6.3 Line Loopback Test Connector H325

This connector is shown in Figure 2-7. It can be used during diagnostic tests to trace a fault to a single channel.

Figure 2-7 Line Loopback Test Connector

#### 2.6.4 Null Modem Cables

Null modem cables are used for local RS-232-C connection. Because of Federal Communications Commission (FCC) regulations, the cable specifications for the United States and Canada are different from those for non-FCC countries. Other countries may also have similar ElectroMagnetic Interference (EMI) control regulations. EMC/RFI shielded cabinets (see glossary) are now available for systems which conform to FCC requirements.

# Recommended null modem cables are as follows:

- 1. BC22D (for EMC/RFI shielded cabinets)

- Round 6-conductor fully shielded cable to FCC specification

- Subminiature 25-pin D-type female connector moulded on each end

- Lengths available:

```

BC22D-10 - 3.1 m (10 ft)

BC22D-25 - 7.62 m (25 ft)

BC22D-35 - 10.72 m (35 ft)

BC22D-50 - 15.24 m (50 ft)

BC22D-75 - 22.9 m (75 ft)

BC22D-A0 - 30.48 m (100 ft)

BC22D-B5 - 76.2 m (250 ft).

```

#### 2. BC03M

- Round 6-conductor (three twisted pairs), each pair shielded

- Cables over 30.48 m (100 ft) have a 25-pin subminiature D-type female connector at one end. The other end is unterminated for passing through conduit.

- Cables 30.48 m (100 ft) and less have a similar connector at each end.

- Lengths available:

```

BC03M-25 - 7.62 m (25 ft)

BC03M-A0 - 30.48 m (100 ft)

BC03M-B5 - 76.2 m (250 ft)

BC03M-E0 - 152.4 m (500 ft)

BC03M-L0 - 304.8 m (1000 ft).

```

#### 3. BC22A

- Round 6-conductor cable

- Subminiature 25-pin D-type female connector moulded at each end

- Lengths available:

```

BC22A-10 - 3.1 m (10 ft)

BC22A-25 - 7.62 m (25 ft).

```

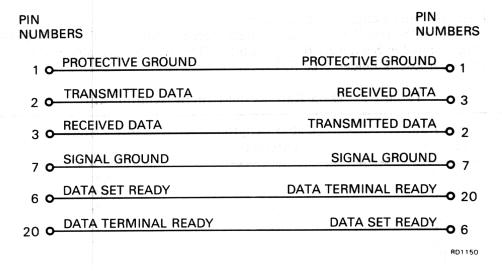

Cables of groups 1, 2, and 3 are all connected as in Figure 2-8. The cables are not polarized. They can be connected either way round.

Figure 2-8 Null Modem Cable Connections

#### 2.6.5 Full Modem Cables

Recommended full modem cables are as follows:

- 1. BC22F (for EMC/RFI shielded cabinets)

- Round 25-conductor fully shielded cable

- Subminiature 25-pin D-type female connector on one end, male connector on the other

- Lengths available:

```

BC22F-10 - 3.1 m (10 ft)

BC22F-25 - 7.62 m (25 ft)

BC22F-35 - 10.72 m (35 ft)

BC22F-50 - 15.24 m (50 ft)

BC22F-75 - 22.9 m (75 ft)

```

#### BC05D

- Round 25-conductor cable

- Subminiature 25-pin D-type female connector on one end, male connector on the other

- Lengths available:

```

BC05D-10 - 3.1 m (10 ft)

BC05D-25 - 7.62 m (25 ft)

BC05D-50 - 15.24 m (50 ft)

BC05D-60 - 18.6 m (60 ft)

BC05D-A0 - 30.48 m (100 ft).

```

#### **CAUTION**

In some countries, protective hardware may be needed when connecting to certain lines. Refer to the national regulations before making a connection.

# 2.6.6 Data Rate to Cable Length Relationships

All the recommended cables have data rate/cable length characteristics as in Table 2-5. Cables of lengths different from those quoted in Sections 2.6.4 and 2.6.5 will have to be specially made. A suitable non-FCC cable for this purpose is Belden type 8777.

Table 2-5 Data-Rate/Cable-Length Relationships

| Data Rate (Bits/s) | Cable Length (Meters) | Cable Length (Feet) |  |

|--------------------|-----------------------|---------------------|--|

| 110                | 914                   | 3000                |  |

| 300                | 914                   | 3000                |  |

| 1200               | 152                   | 500                 |  |

| 2400               | 152                   | 500                 |  |

| 4800               | 76                    | 250                 |  |

| 9600               | 76                    | 250                 |  |

#### **NOTE**

Cables longer than 15.24 m (50 ft) or with a capacitance greater than 2.5 nanofarads, violate RS-232-C and V.28 specifications. These are not supported by DIGITAL.

### 2.7 MULTIPLE COMMUNICATIONS OPTIONS

# 2.7.1 Floating Device Addresses

On UNIBUS and Q-bus systems, a band of addresses ( $xxx60010_8$  to  $xxx63776_8$ ) in the top 4K words is assigned as floating address space (xxx means all top address bits = 1).

Options which can be assigned floating device addresses are listed in Table 2-6. This table gives the sequence of addresses for both UNIBUS and Q-bus options. For example, the address sequences could be:

| UNIBUS | Q-Bus        |            |

|--------|--------------|------------|

| DJ11   | <b>DJ</b> 11 |            |

| DH11   | DH11         |            |

| DQ11   | DQ11         |            |

| DU11   | DÙV11        |            |

| DUP11  | DUP11        |            |

| DMC11  | DMC11        |            |

| DZ11   | DZV11        | and so on. |

|        |              |            |

Having one list allows us to use one set of configuration rules and one configuration program.

Table 2-6 Floating Device Address Assignments

| Rank                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Device      | Size<br>(Decimal) | Modulus<br>(Octal)    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------|-----------------------|

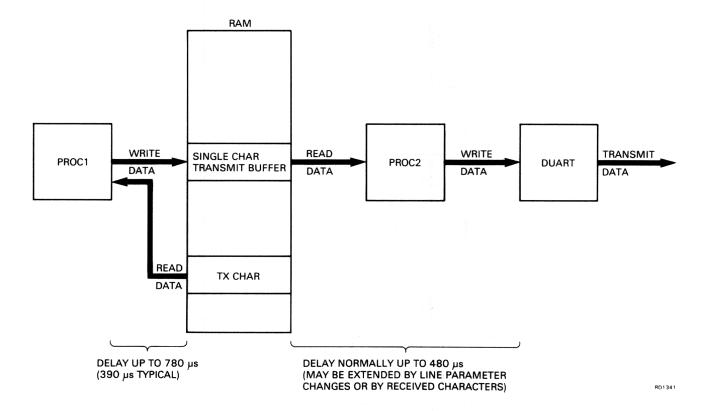

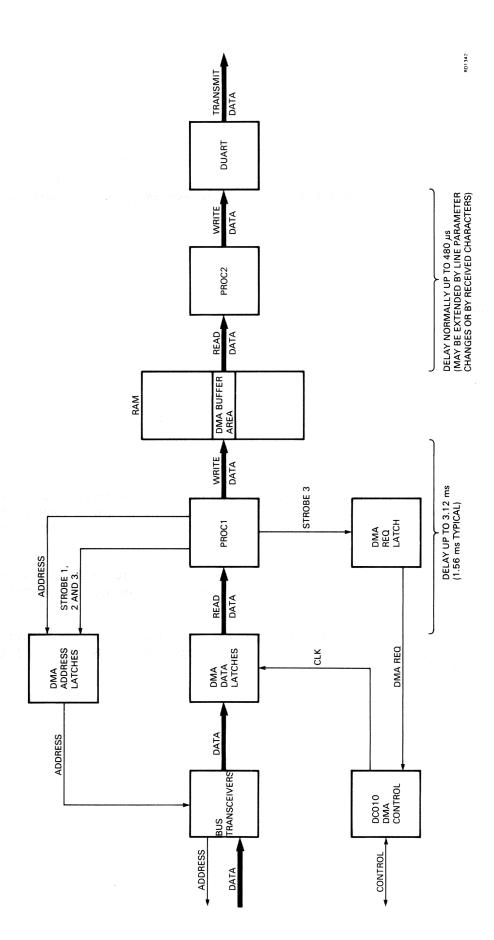

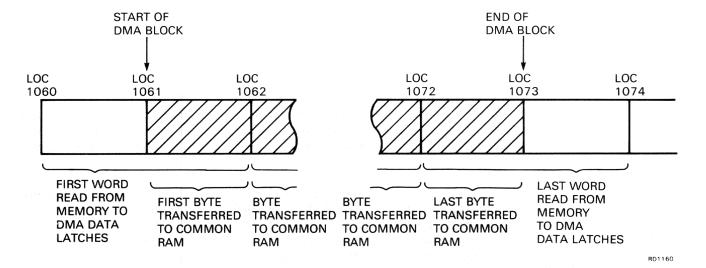

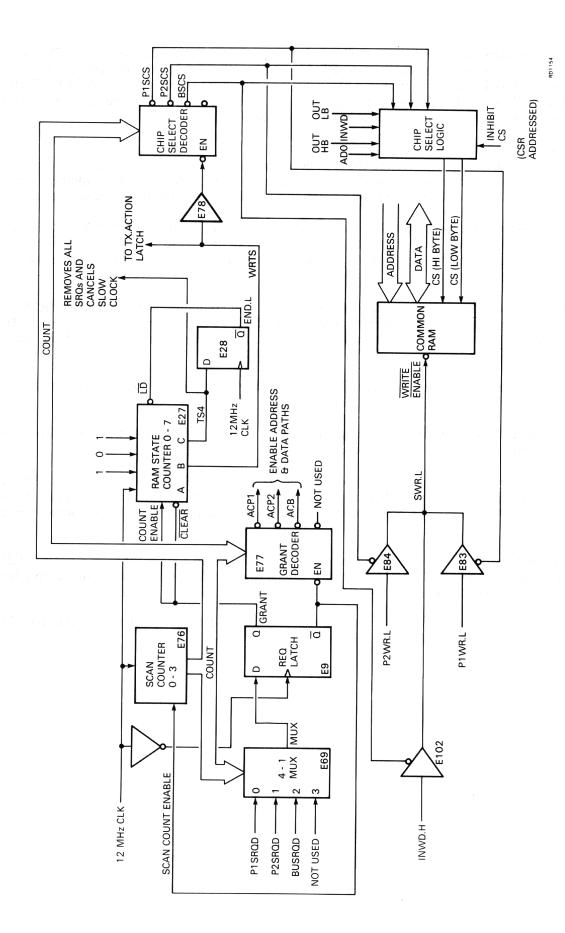

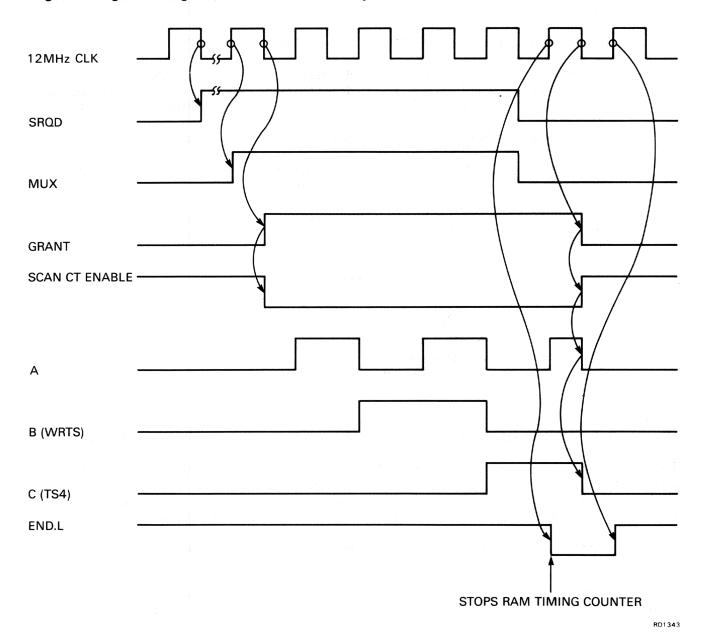

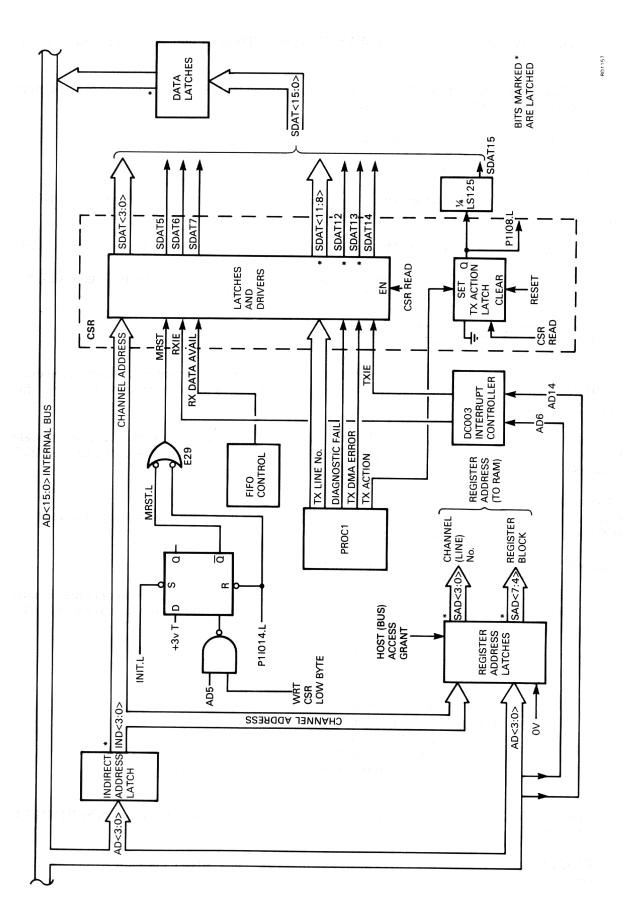

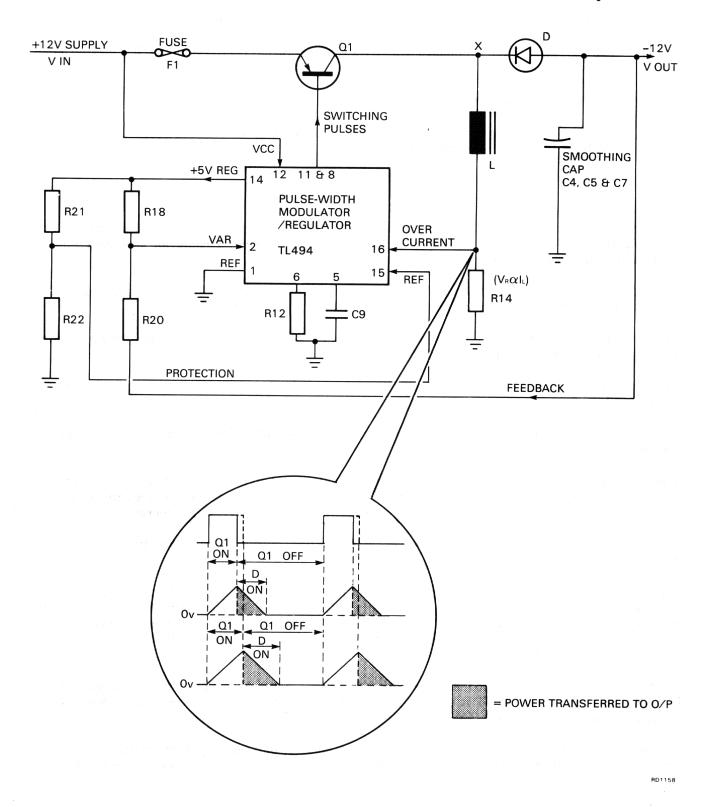

| which is a state of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DJ11        | 4                 | 10                    |