PDP-9 Maintenance Homework Sheets

Order Number: XX-E02FB-92

This document is a collection of homework exercises and their corresponding answers primarily focused on the PDP-9 and PDP-9/9L computer systems. It comprises "Homework Sheets" numbered #1, #2, #3, #4, #6, and #7, along with an additional "PDP-9/9L Homework" problem. The exercises delve into various aspects of computer architecture, instruction set, and system maintenance.

Key topics covered include:

- Instruction Set Architecture: Coding and decoding instructions like DZM, LAC, TAD, LAW, JMS, AND, XOR, and understanding their effects on registers and memory.

- Memory Operations: Analyzing memory reference instructions, calculating memory locations, understanding memory cycle timing, and the role of various flip-flops (e.g., SM flip-flop, Digit Write Sink).

- Register Management: Determining the contents of registers (AR, PC, MB, MA, AC) after specific operations or program execution.

- Digital Logic and Control: Examining the function of control flip-flops (AC0, AR1, SAO F/F), logical expressions for hardware events (e.g., ADD overflow), and the interaction of Control Memory (CM) with the Instruction Register (IR).

- Program Execution and Debugging: Simulating program runs, predicting outcomes like end-around carry or ADD overflow, and understanding the impact of console switches (Repeat, Single Step, Address Switches, Start Key) on computer operation.

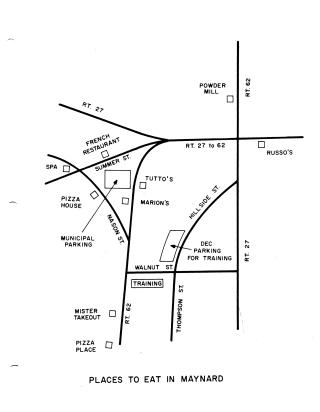

The first page of the document is an unrelated map titled "Places To Eat In Maynard," illustrating local roads and businesses in a town.

Site structure and layout ©2025 Majenko Technologies