Extended Addressing

Order Number: 5

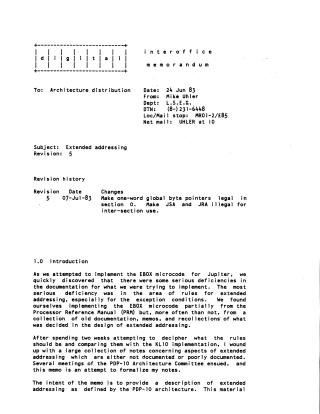

This memorandum formalizes the rules for extended addressing in the PDP-10 architecture, addressing deficiencies found in existing documentation during EBOX microcode implementation. The document aims to describe how extended addressing should be implemented in future PDP-10 processors.

Historically, the PDP-10's virtual address space expanded from 18-bit (256K words) to 30-bit (1 billion words), logically divided into 4096 sections of 256K words each. To maintain compatibility, section zero behaves like a non-extended processor, while other sections allow 30-bit addressing. The KL10 model B initially implemented 32 sections, with the KC10 implementing the full 30-bit space.

The core of extended addressing is the Effective Address Calculation (EA-calc) process, which computes a 30-bit address along with a local/global flag. Address words can be in Instruction Format Indirect Word (IFIW) or Extended Format Indirect Word (EFIW) format, and indices can be local or global, leading to complex EA-calc algorithms. The initial default section for an EA-calc is typically the PC section but can change, and the local/global flag from the last address word fetched determines the final result's type. Section zero can only be referenced from a non-zero section via specific EFIW indirect words.

The local/global flag has significant implications:

- AC References: Local addresses (bits 18-35 in 0-17 range) always refer to Accumulators (ACs), regardless of the section. Global addresses to section 1, locations 0-17 also refer to ACs.

- Incrementing/Decrementing: Local addresses wrap around within their section, while global addresses are treated as full 30-bit quantities, allowing them to cross section boundaries.

Multi-section EA-calc operations can lead to section changes. If an EA-calc enters section zero, all subsequent addresses are treated as local to section zero, and further operations obey section zero rules.

Several special instructions behave differently in an extended addressing environment:

- Byte and EXTEND instructions: Their byte pointer interpretation and EA-calc default sections depend on the section from which the byte pointer (or extended opcode) was fetched, or the PC section.

- JSP/JSR: In non-zero PC sections, they store the full 30-bit PC+1 (instead of 18-bit PC + flags). Inter-section calls using these are complex to return from.

- JSA/JRA: Restricted to intra-section use due to format incompatibility with extended addressing; inter-section usage is undefined.

- LUUOs: Trap through a four-word block addressed by the User/Executive Process Table (UPT/EPT) when the PC is in a non-zero section.

- BLT/XBLT: BLT is for intra-section transfers, incrementing section-local. XBLT was added for full 30-bit global block transfers.

- XMOVEI/XHLLI: Convert local AC references in non-zero sections to global AC addresses.

- XCT (Execute Instruction): The default section for the executed instruction's EA-calc is where the executed instruction was fetched. Tests for section zero rules related to the executed instruction are based on the XCT instruction's PC section. PC-storing instructions store values relative to the XCT's PC.

PXCT (Previous Context XCT) is a mechanism for the monitor to interact with a "previous context" (defined by Previous Context Section (PCS), Previous Context User (PCU), and Previous AC Block (PAB)). PXCT modifies how EA-calc and data references are made for executed instructions. While the PXCT instruction itself operates in the current context, its AC field bits can direct the executed instruction's memory and index register references to the previous context, altering default section settings and post-processing of EA-calc results. This allows the monitor to reference user data as if the user were running the instruction.

Site structure and layout ©2025 Majenko Technologies