EUNITS Introduction

Order Number: Chapter 1

This document provides a comprehensive overview of the architecture and functionality of the Execution Units (EUNITS) within the JUPITER CPU. It is organized into three main chapters, detailing the partitioning, operation, diagnostic interfaces, error control, and clocking mechanisms of its core components: the Instruction Box (IBOX), Execution Box (EBOX), and the Floating Point Accelerator (FPA).

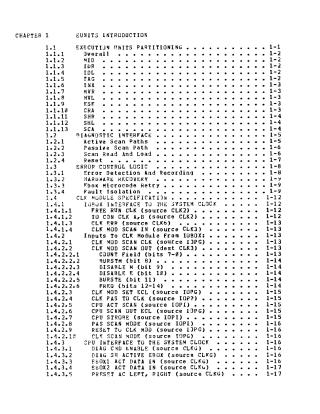

Chapter 1 introduces the various EUNITS modules, including MID, IDR, IDL, TAG, INX, MVR, MVL, ESE, CRA, SHR, SHL, and SCA, outlining their individual roles in instruction processing. It then describes the diagnostic interface, explaining active and passive scan paths for system monitoring and debugging, alongside procedures for system reset. A significant portion is dedicated to Error Control Logic, covering error detection, recording (using FRU codes), hardware recovery mechanisms (such as microcode retries), and fault isolation techniques. The chapter concludes with the CLK Module Specification, detailing how it controls synchronous clock phases, diagnostic start/stop functions, and various clock-related signals essential for the EUNITS.

Chapter 2 focuses in depth on the EBOX, highlighting its design for high-performance instruction execution. It details the MVE Module (containing MVL/MVR) responsible for binary/decimal arithmetic and Boolean functions, the SHL/SHR Modules for shifting and register file operations, and the SCA Module for managing shift control, accounting meters, and timers. This chapter extensively covers the EBOX's microcode control specification (implemented via ESE/CRA RAMs), explaining how various fields and bits control its internal operations, interfaces with other units, and handles errors.

Chapter 3 delves into the IBOX, emphasizing its primary function of prefetching instructions and operands from the MBOX to minimize memory access delays. It describes the IDL/IDR Modules, which manage the memory address path (VMA bus), the Index AC for effective address calculations, the EA ALU for address arithmetic, and mechanisms for instruction stream prefetching and conflict detection to ensure data consistency. The chapter also outlines the IBOX's error and diagnostic control for its address and data paths.

Overall, the document serves as a detailed technical reference for understanding the JUPITER CPU's execution pipeline, its robust diagnostic capabilities, and its intricate error detection and recovery mechanisms.

Site structure and layout ©2025 Majenko Technologies