M-1110 SeqBrk Jun61

Order Number: XX-CA15A-2E

This document details the evolution of Input-Output (I/O) communication methods for the PDP-1 computer, addressing the challenge of synchronizing diverse devices with the CPU while optimizing computer speed.

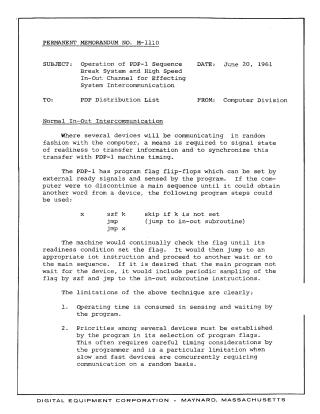

Normal In-Out Intercommunication: This basic method uses program flag flip-flops, set by external ready signals, which the program then polls using instructions like

szfandjmp. While functional, it's inefficient because it consumes CPU operating time waiting for devices and forces the programmer to manually manage priorities and timing, especially problematic for devices with varying speeds.Sequence Break System: An optional, more efficient system for concurrent operation of multiple asynchronous I/O devices with the main program. It provides:

- Automatic Interruption: The program is automatically interrupted (breaking to an I/O sequence) by a device's completion, an external signal, or the program itself.

- Priority-Based Interruption: Faster devices (e.g., magnetic tape) can interrupt slower ones (e.g., typewriter), enabling concurrent operation.

- Mechanism: It uses 16 priority channels. When an interrupt occurs, the current CPU state (AC, IO, PC registers) is stored in channel-specific memory registers, and control transfers to an I/O subroutine defined by an instruction in a fourth channel register. The process takes 20 usec to enter and 30 usec to terminate, plus the I/O sequence time. Higher priority interrupts can further interrupt an ongoing I/O sequence.

High Speed In-Out Channel: An optional feature designed specifically for rapid block transfers of words between memory and high-speed I/O devices (like magnetic tape).

- Efficiency: It drastically reduces transfer time to a single machine cycle (5 usec) per word after initial setup (25 usec to define the block by loading memory start/end addresses).

- Mechanism: It largely bypasses the main CPU, communicating directly with memory via the Memory Buffer Register. The channel automatically interrogates the memory bus, pausing the main program for only one memory cycle per word transfer. This allows block transfers to proceed with minimal disturbance to the main program.

- Advantage: Compared to using the Sequence Break System for magnetic tape (which takes ~80 usec per word and leaves ~80% computation time), the High Speed Channel offers significantly more available computation time (e.g., 98.7%), as it offloads the word-by-word transfer overhead from the CPU. Its benefit diminishes for slower I/O devices.

In summary, the document illustrates a progression from basic, CPU-intensive I/O handling to advanced, hardware-assisted systems that improve efficiency and CPU utilization, particularly for high-speed, block data transfers.

Site structure and layout ©2025 Majenko Technologies