4475212 Frequency-Independent Self-Clocking Encoding Technique and Apparatus for Digital Communications Sep81

Order Number: XX-769C0-72

This patent describes a frequency-independent, self-clocking encoding technique and apparatus for digital communications, specifically designed for synchronous transmission between devices like controllers and drives in data processing systems.

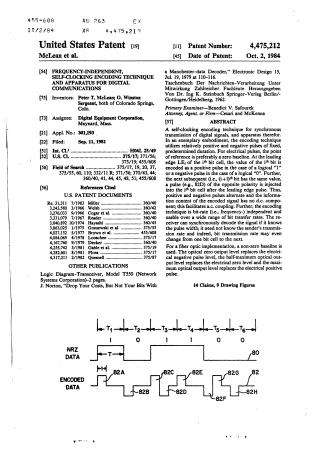

Core Mechanism: The technique utilizes fixed-duration, bipolar (positive and negative) pulses.

- Leading Edge Encoding: At the beginning of each bit cell (the leading edge), the value of the current bit is encoded. A logical '1' is represented by a positive pulse, and a logical '0' by a negative pulse.

- Look-Ahead Compensation: To maintain a DC-free signal, the system "looks ahead" to the next bit. If the current bit and the next bit have the same value, a second "compensation" pulse of the opposite polarity to the leading-edge pulse is injected into the current bit cell, after the initial leading-edge pulse.

Key Benefits & Features:

- Self-Clocking: Eliminates the need for a separate clocking signal, as both clock and data information are embedded in the encoded stream.

- DC-Free Signal: The alternating pulse polarities ensure the encoded signal has no DC component, which facilitates AC coupling and helps eliminate ground loop problems in electrical interconnections.

- Frequency-Independent (Bit-Rate Independent): The encoding is usable over a wide range of bit transfer rates. The receiver only needs to know the fixed pulse width, not the sender's transmission rate, making it highly flexible.

- Error Detection: The inherent alternating pulse polarities allow for the detection of missing or added pulses (e.g., due to noise).

Implementations:

- Electrical: Uses positive and negative electrical pulses relative to a zero baseline.

- Fiber Optic: A non-zero baseline is used, with different optical intensity levels replacing the electrical pulse levels (e.g., zero output for negative, half-maximum for zero, maximum for positive).

This method simplifies interconnections, improves communication robustness, and is cost-effective, particularly in secondary storage facilities.

Site structure and layout ©2025 Majenko Technologies