S205

Order Number: XX-56836-6C

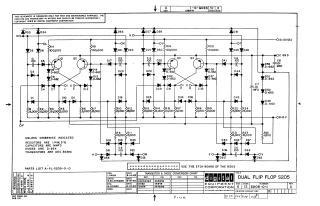

This document is a proprietary schematic diagram for a Digital Equipment Corporation (DEC) Dual Flip Flop, model S205-0-1 (Revision D), copyrighted in 1965.

It is intended for test and maintenance purposes.

The circuit design features two distinct flip-flop stages, utilizing DEC 3639C transistors (EIA 2N3639 equivalent), various diodes (primarily D-664 / IN3606, and D-662 / IN645), 1/4W 5% resistors, and micromicrofarad (MMFD) capacitors.

It operates with +10V, -15V, and ground power supplies.

Site structure and layout ©2025 Majenko Technologies