M310

Order Number: XX-BF1AE-A8

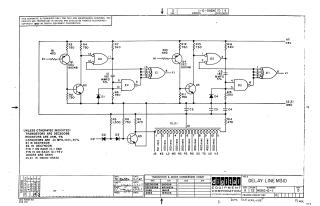

This document is a proprietary schematic for the "DELAY LINE M310" circuit board (M310-0-1, Revision D) from Digital Equipment Corporation (DEC), copyrighted in 1967. It is intended solely for test and maintenance purposes.

The schematic details an electronic circuit featuring:

- A central Digital Delay Line (DLDI), model DEC16-05530, with 11 taps providing delays from 50 nanoseconds up to 500 nanoseconds.

- Multiple transistors (DEC3009B and DEC6534B models).

- Integrated Circuits (ICs) identified as E1 (DEC7440N) and E2 (DEC7400N), which are likely TTL logic gates, powered by +5V (Pin 14) and grounded at Pin 7.

- Various diodes (D664).

- Standard resistors (1/4W, 5% tolerance) and capacitors (.01 MFD, 100V, 20% tolerance, with specific 180 MMFD, 5% capacitors for C1 and C5).

The document also includes a Transistor & Diode Conversion Chart providing equivalent EIA part numbers for DEC components (e.g., DEC3009B to 2N3009, D664 to IN3606) and a revision history.

Site structure and layout ©2025 Majenko Technologies