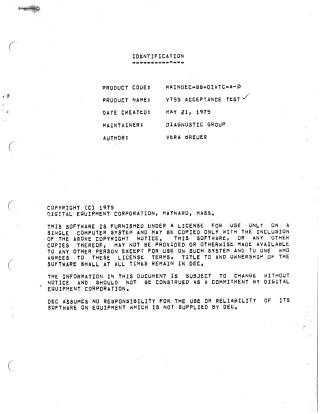

Vt55 Acceptance Test

Order Number: MAINDEC-08-DIVTC-A

This document provides the operational guide and assembly source code for the VT55 Acceptance Test, a program designed to verify the functionality of the VT55 Video Terminal when connected to a PDP-8 family computer via a DL-11 interface.

Summary of Operations:

- Purpose: The test uses 13 distinct visual patterns to verify terminal performance. Each pattern requires operator inspection to detect errors.

- Setup: The program runs on a PDP-8 with 4K of memory. The operator must specify the first and last receiver IOT addresses to be tested using location "FIRST" and "LAST" on page zero.

- Execution: The program can be started at address 200. It offers two modes of operation based on the state of switch bit 05: one under switch register control and another under keyboard control, allowing the operator to select or loop on specific test patterns.

- Controls: The program includes various control switch settings to manage error handling (e.g., inhibiting error halts, looping on errors, or halting after a program pass).

- Error Reporting: If an error occurs, the system prints a descriptive message identifying the error and the Program Counter (PC) location before halting.

- Test Patterns: The document details several specific visual diagnostic patterns, including growing horizontal and vertical lines, stepping lines, histograms, cursor patterns, and a final adjustment pattern consisting of rows of the letter "H" overlaid with lines.

Site structure and layout ©2025 Majenko Technologies