Pdp-12 Memory Organization

Order Number: XX-A5540-0D

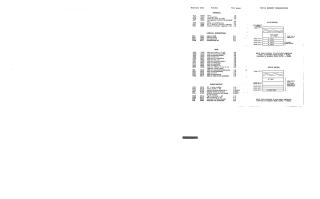

This document provides a detailed overview of the PDP-12 computer's memory organization and instruction set. It categorizes instructions by function, including "OPERATE" instructions (e.g., halt, clear registers, jump), "LOGICAL OPERATIONS" (e.g., AND, OR, complement), "SKIP" conditions (e.g., skip on AC conditions, sense switches, overflow, tape status), and "INPUT-OUTPUT" operations (e.g., relay buffer transfers, analog sampling, display functions, switch reads, transfer to PDP-8 mode, I/O execution). Each instruction is listed with its mnemonic code, function, and execution time in microseconds.

The document also illustrates the memory organization for both LINC-Mode and PDP-8 Mode. In LINC-Mode, memory features a 15-bit absolute addressing system with basic 4K PDP-12 memory expandable up to 32K. This extra memory is divided into 1K "FIELD" blocks, containing 15 auto-index registers, and utilizes 4-256 word "MEMORY BLOCKS." Specific "Trap" and Interrupt locations are defined for this mode. The PDP-8 Mode also includes a basic 4K PDP-12 memory, organized into a 4K "FIELD" and 32-128 word "PAGES" per 4K memory field, with each field containing 8 auto-index registers. An Interrupt location is specified for PDP-8 Mode as well.

Site structure and layout ©2025 Majenko Technologies